摘 要: 針對設(shè)計某高速衛(wèi)星數(shù)據(jù)通信幀同步系統(tǒng)" title="幀同步系統(tǒng)">幀同步系統(tǒng)中所遇到的問題,提出了一種新的并行幀同步設(shè)計方案,解決了同步字碼組不能穩(wěn)定提取、同步狀態(tài)判斷時間過短等問題,實現(xiàn)了高速衛(wèi)星數(shù)據(jù)通信系統(tǒng)的幀同步并得到了驗證。對于速度更高的數(shù)據(jù)通信系統(tǒng),給出了一種多路" title="多路">多路并行幀同步的設(shè)計方法。

關(guān)鍵詞: 幀同步 漢明距 FPGA

同步[3]是通信系統(tǒng)的一個重要環(huán)節(jié),通常包括載波同步、位同步和幀同步。幀同步系統(tǒng)的基本設(shè)計思想[1]是在系統(tǒng)發(fā)送端數(shù)據(jù)幀中適當(dāng)?shù)奈恢锰幉迦胪阶执a組,在接收端設(shè)計一個大的數(shù)據(jù)緩沖區(qū),能夠?qū)⑺型阶止?jié)恰好覆蓋,并在數(shù)據(jù)幀緩沖區(qū)的適當(dāng)位置處提取同步字碼組,同時將提取到的同步字碼組送入漢明距累加器計算漢明距并與檢測門限進(jìn)行比較;同步控制狀態(tài)機(jī)根據(jù)比較結(jié)果為接收系統(tǒng)提供同步控制信息,從而實現(xiàn)同步。當(dāng)數(shù)據(jù)幀較大時,由于數(shù)據(jù)緩沖器較長,隨著數(shù)據(jù)速率" title="數(shù)據(jù)速率">數(shù)據(jù)速率的提高,同步字碼組很難穩(wěn)定地從數(shù)據(jù)緩沖區(qū)中提取出來,同時由于同步判斷時間過短而又影響同步系統(tǒng)的穩(wěn)定性和魯棒性。為解決這一問題,本文給出了一種并行同步的設(shè)計方法。

1 并行同步的基本原理

當(dāng)通信系統(tǒng)的接收機(jī)收到一路初始位置隨機(jī)的高速數(shù)碼流時,為能穩(wěn)定地提取同步字碼組而實現(xiàn)同步,可將串行數(shù)據(jù)轉(zhuǎn)換為并行,從而降低數(shù)據(jù)率。經(jīng)串并轉(zhuǎn)換" title="串并轉(zhuǎn)換">串并轉(zhuǎn)換后的并行數(shù)碼流中,同步字節(jié)中各個比特的位置可存在幾種不同的情況。現(xiàn)在以一路到兩路的串并轉(zhuǎn)換為例進(jìn)行說明。假設(shè)圖1是一段包括一個同步字節(jié)的串行數(shù)碼流,其中A7 A6 A5 A4 A3 A2 A1 A0為同步字節(jié)中的八個比特,高位在前,箭頭表示數(shù)據(jù)傳輸方向。該數(shù)碼流在經(jīng)過一路到兩路的串并轉(zhuǎn)換后,由于數(shù)據(jù)起始比特的隨機(jī)性,同步字節(jié)各個比特的位置可能是圖2或圖3所示的情況。圖2中同步字節(jié)的奇數(shù)位和偶數(shù)位在兩路中恰好對稱分開,高位A7在上邊一路中。圖3中的同步字節(jié)沒有對稱分開,高位A7在下邊一路。同步過程中可以對這兩種同步字相位情況進(jìn)行搜索提取,計算漢明距。這樣同步系統(tǒng)的工作數(shù)據(jù)率就降為輸入數(shù)據(jù)率的一半,使得同步系統(tǒng)的性能穩(wěn)定可靠。

同理,串行數(shù)據(jù)經(jīng)一路到三路串并轉(zhuǎn)換后,同步字節(jié)在三路數(shù)據(jù)中的相位有三種情況,經(jīng)四路轉(zhuǎn)換有四種相位情況,…,可以推得,串行數(shù)據(jù)經(jīng)一路到N(N≤8)路串并轉(zhuǎn)換后,就有N種同步字相位情況,同步時建立N路的同步字碼組搜索系統(tǒng)。這樣數(shù)據(jù)速率就降為輸入數(shù)據(jù)速率的N分之一,從而改善了同步系統(tǒng)的性能,即多路并行同步。

2 兩路并行幀同步系統(tǒng)的設(shè)計與仿真

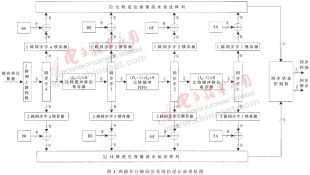

考慮到成本等具體情況,設(shè)計中采用了Altera公司Flex10K系列FPGA芯片EPF10K30RC240-3,需要設(shè)計的同步緩沖器是一個緩沖長度可調(diào)、深度可變、嵌有4個位置可變的同步字節(jié)數(shù)據(jù)緩沖區(qū),在第一、第二個同步字間和第三、第四個同步字間采用移位寄存器,其長度可調(diào);在第二、第三個同步字間由于要緩沖的數(shù)據(jù)較長,為節(jié)省資源采用FIFO仿真移位寄存器,其深度可變。設(shè)計中先將串行數(shù)據(jù)進(jìn)行一路到兩路轉(zhuǎn)換,再分別對兩種同步字相位進(jìn)行搜索提取同步字碼組,計算漢明距,經(jīng)同步狀態(tài)控制機(jī)給出同步控制信號和同步指示信號。該同步系統(tǒng)的設(shè)計原理框圖如圖4所示。

其中5A、0F、BE、66是十六進(jìn)制的四個同步字節(jié);Id和Di是交織器的兩個參數(shù);32比特進(jìn)位保留流水加法陣列用于計算漢明距;兩路漢明距發(fā)生器均采用華萊士樹流水累加計算方式,分別對不同相位所提取的同步字碼組進(jìn)行漢明距計算,并將結(jié)果送同步狀態(tài)控制機(jī),進(jìn)行同步搜索、同步監(jiān)視和同步保護(hù)等。

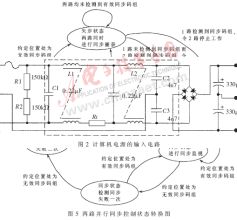

設(shè)計中的同步狀態(tài)控制采用IESS308標(biāo)準(zhǔn)[2]建議的同步捕獲判斷2次(檢測門限為漢明距不超過1)、失步" title="失步">失步保護(hù)判斷4次(檢測門限是漢明距超過6)的設(shè)計方案。同步字碼組提取采用兩路全節(jié)能搜索提取方式。同步系統(tǒng)的狀態(tài)轉(zhuǎn)換原理圖如圖5所示。系統(tǒng)剛開始處于失步狀態(tài)時,兩路搜索同時工作,當(dāng)?shù)谝宦窓z測到同步字碼組,就令第二路停止工作并給出第一路工作標(biāo)志(如果第一路未檢測到同步字碼組而第二路檢測到同步字碼組,就令第一路停止工作并給出第二路工作標(biāo)志),同時系統(tǒng)轉(zhuǎn)入按幀判斷方式,到下一幀該位置處判斷是否還是同步字碼組,是,系統(tǒng)進(jìn)入同步狀態(tài);不是,系統(tǒng)則轉(zhuǎn)回到兩路搜索捕獲狀態(tài)。當(dāng)系統(tǒng)完成首次漢明距不超過1的同步判斷后(包括同步監(jiān)視和同步保護(hù)狀態(tài)),同步系統(tǒng)兩路漢明距發(fā)生器轉(zhuǎn)入僅在每幀的同步字碼組處中的一路工作幾個時鐘周期(設(shè)計中工作7個時鐘周期,因為漢明距發(fā)生器加了7級流水)的工作方式,從而使得同步系統(tǒng)的能量消耗降為最小。進(jìn)入同步狀態(tài)后,當(dāng)系統(tǒng)在一幀的同步字碼組處檢測到的結(jié)果不滿足漢明距門限值時,則系統(tǒng)轉(zhuǎn)入同步保護(hù)一次狀態(tài);系統(tǒng)繼續(xù)在下一幀的同步字碼組處進(jìn)行檢測,當(dāng)再次檢測到結(jié)果不滿足漢明距門限值時,則系統(tǒng)轉(zhuǎn)入同步保護(hù)兩次狀態(tài);以此類推,當(dāng)同步系統(tǒng)連續(xù)四次判斷漢明距不滿足門限要求時,則系統(tǒng)轉(zhuǎn)入失步狀態(tài),同時令兩路同步搜索系統(tǒng)同時開始搜索,系統(tǒng)進(jìn)入并行同步捕獲狀態(tài)。注意:在捕獲過程中第一路搜索優(yōu)先于第二路。

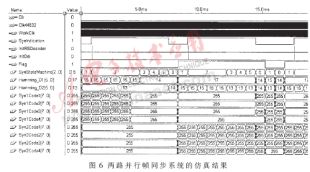

為了測試同步系統(tǒng),在模擬發(fā)送端數(shù)據(jù)幀結(jié)構(gòu)中設(shè)計了一個模擬同步信號源。該信號源僅在數(shù)據(jù)幀的同步字碼組處插入同步字碼組,在其它位置上均輸出255。采用該模擬同步信號源測試兩路并行同步系統(tǒng),在MaxplusII中進(jìn)行了仿真,仿真波形如圖6所示。圖6中Clk44832是輸入的基帶數(shù)據(jù)時鐘(時鐘周期20ns);SynIndication是同步指示信號,當(dāng)該信號變高時,表示系統(tǒng)進(jìn)入同步狀態(tài),變低時,則表示系統(tǒng)處于失步狀態(tài);InitDeI、InitRSDeCoder和Flag是同步系統(tǒng)的控制信號;SynStateMachine[2..0]是同步控制狀態(tài)機(jī)的狀態(tài)信息,0狀態(tài)和1狀態(tài)是失步狀態(tài),2狀態(tài)是同步監(jiān)視狀態(tài),3、4、5狀態(tài)是同步保護(hù)狀態(tài)。Syn1Code1[7..0]、Syn1Code2[7..0]、Syn1Code3[7..0]和Syn1Code4[7..0]是第一路同步系統(tǒng)的4個同步字節(jié)緩沖器;Syn2Code1[7..0]、Syn2Code2[7..0]、Syn2Code3[7..0]和Syn2Code4[7..0]是第二路同步系統(tǒng)的4個同步字節(jié)緩沖器,分別用于提取第一路、第二路同步系統(tǒng)的同步字碼組。Hamming_D1[5..0]、Hamming_D2[5..0]分別是第一路和第二路漢明距發(fā)生器計算所得到的漢明距。模擬同步信號源設(shè)計成從第一路同步到失步,從第二路同步到失步,再從第一路同步搜索轉(zhuǎn)換到第二路同步搜索、第二路同步的過程。從圖6中可清楚地看到同步系統(tǒng)各個狀態(tài)之間的轉(zhuǎn)換過程。證明同步系統(tǒng)工作正常。

3 兩路并行幀同步系統(tǒng)的測試與應(yīng)用

在正常情況下,系統(tǒng)初始化結(jié)束后,同步指示燈應(yīng)該變亮,此時表明同步系統(tǒng)已經(jīng)同步,電路已經(jīng)正常工作。測試過程中,首先按下復(fù)位鍵,讓同步指示燈熄滅,然后松開復(fù)位鍵,使得系統(tǒng)開始一次新的同步搜索;當(dāng)同步指示燈再次變亮?xí)r,說明系統(tǒng)已經(jīng)重新建立同步,根據(jù)系統(tǒng)測試控制開關(guān)的位置和測試端口的數(shù)據(jù),可以讀出同步計數(shù)器的數(shù)值,從而計算出同步捕獲時間。計算公式為:

同步捕獲時間=(高4位×65536+中8位×256+低8位)×40×10-9s?????????? (1)

其中,高4位、中8位和低8位分別表示同步計數(shù)器的高4位、中8位和低8位二進(jìn)制結(jié)果。

在沒有誤碼的理想情況下,本系統(tǒng)同步捕獲時間tc應(yīng)滿足:

(19968+7)×40×10-9s≤tc≤(19968×2+6)×40×10-9s

即:799μs≤tc≤1597.68μs????????????????????????????????????????? (2)

在有誤碼的情況下,系統(tǒng)漏掉一次同步字碼組的同步捕獲時間tc應(yīng)該滿足:

(19968×2+7)×40×10-9s≤tc≤(19968×3+6)×40×10-9s

即:1597.72μs≤tc≤2396.40μs????????????????????????????????????? (3)

在誤碼率很高、系統(tǒng)連續(xù)漏掉n次同步字碼組的同步捕獲時間tc應(yīng)該滿足:

[19968×(n-1)+7]×40×10-9s≤tc≤(19968×n+6)×40×10-9s?????????? (4)

實際測量中,采用偽隨機(jī)序列模擬噪聲干擾。在誤比特率為10-4情況下,對實際電路進(jìn)行了一系列的測量,表1是其中具有代表性的結(jié)果。

表1中的測量結(jié)果是根據(jù)公式(1)計算得出的,其中有5次結(jié)果滿足(2)式,說明此時同步系統(tǒng)沒有漏掉同步字碼組,達(dá)到了同步的期望效果;有一次結(jié)果超過1.59768ms了,但滿足(3)式,說明同步系統(tǒng)在該誤碼率情況下,漏掉了一個同步字碼組。在實際的大量測量過程中,這種情況出現(xiàn)的次數(shù)很少,說明這是小概率事件。

在本設(shè)計中,每幀數(shù)據(jù)為39936比特,采用兩路并行同步,每幀每路漢明距發(fā)生器要工作19968個時鐘。設(shè)計中采用的全節(jié)能設(shè)計是指系統(tǒng)在失步時,兩路同步搜索系統(tǒng)同時工作,在同步監(jiān)視和同步保護(hù)狀態(tài)時,同步系統(tǒng)僅在每幀的同步字碼組位置處其中的一路工作7個時鐘周期,其它時刻兩路均不工作。半節(jié)能設(shè)計是指系統(tǒng)在失步時,兩路同步搜索系統(tǒng)同時工作,在同步監(jiān)視和同步保護(hù)狀態(tài)時,只有其中的一路工作。在同步監(jiān)視和同步保護(hù)狀態(tài)時,全節(jié)能設(shè)計從每幀工作39936個時鐘降為7個時鐘,半節(jié)能設(shè)計從每幀工作39936個時鐘降為19968個時鐘。這樣,全節(jié)能設(shè)計與半節(jié)能設(shè)計相比,每幀數(shù)據(jù)同步系統(tǒng)少工作19961個時鐘。經(jīng)測試,采用全節(jié)能同步設(shè)計方案,接收板工作電流約為700mA,采用半節(jié)能同步設(shè)計方案,接收板工作電流約為780mA,因此全節(jié)能同步設(shè)計比半節(jié)能同步設(shè)計節(jié)省功耗約為(780-700)×5×10-3=0.4W。可見,節(jié)能效果明顯。

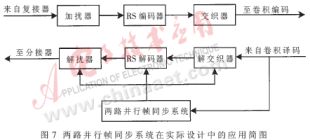

兩路并行同步設(shè)計方法設(shè)計的幀同步系統(tǒng)在實際的某衛(wèi)星數(shù)據(jù)通信系統(tǒng)抗干擾編解碼部分中工作穩(wěn)定、可靠,達(dá)到了理想的預(yù)期效果。該設(shè)計的應(yīng)用簡圖如圖7所示。

4 多路并行幀同步系統(tǒng)

當(dāng)數(shù)據(jù)速率進(jìn)一步提高,兩路并行同步也不能穩(wěn)定提取同步字碼組時,可以采用更多路的并行同步。實現(xiàn)方法是將輸入的串行高速數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換,再根據(jù)串并轉(zhuǎn)換后同步字可能存在的幾種不同相位進(jìn)行同步搜索,提取同步字碼組,計算漢明距,為同步狀態(tài)控制機(jī)提供同步信息。同步系統(tǒng)在開始時進(jìn)行多路并行同步搜索,當(dāng)其中一路捕獲到同步字碼組后,其它各路就停止工作,系統(tǒng)僅按一路同步系統(tǒng)工作。設(shè)計中可以設(shè)成同步捕獲優(yōu)先級從小到大,即第一路優(yōu)先于第二路,第二路優(yōu)先于第三路……。這樣有利于同步系統(tǒng)各個狀態(tài)之間的正常轉(zhuǎn)換。設(shè)計中要采用多路全節(jié)能設(shè)計方式,當(dāng)系統(tǒng)處于同步捕獲狀態(tài)時,多路同步搜索系統(tǒng)同時工作;當(dāng)系統(tǒng)處于同步監(jiān)視和同步保護(hù)狀態(tài)時,同步系統(tǒng)僅在每幀數(shù)據(jù)的同步字碼組位置處工作幾個時鐘。實際通信中,由于系統(tǒng)大部分時間處于同步監(jiān)視狀態(tài),因而全節(jié)能設(shè)計方案可以使得同步系統(tǒng)的功耗降為最小。由于兩路并行同步可以將數(shù)據(jù)速率降為輸入數(shù)據(jù)速率的二分之一,三路并行同步可以降為三分之一,…。當(dāng)采用N路并行同步時,可以將數(shù)據(jù)速率降為輸入數(shù)據(jù)速率的N分之一。設(shè)N為8,由于一路同步搜索系統(tǒng)至少可以穩(wěn)定可靠地工作于25Mbps上,則該同步系統(tǒng)可以穩(wěn)定工作的最高數(shù)據(jù)速率至少可以達(dá)到25×8=200Mbps。可見,多路并行幀同步設(shè)計方案對于高速數(shù)據(jù)幀同步系統(tǒng)的設(shè)計是有意義的。

參考文獻(xiàn)

1 鄒 翊. 衛(wèi)星通信信道單元關(guān)鍵技術(shù)的研究與實現(xiàn). 北京理工大學(xué)博士學(xué)位論文, 2002

2 Intelsat Earth Station Standards (IESS) Document IESS-308 (Rev.9). Performance Characteristics for Intermediate Data Rate Digital Carriers Using Convolutional Encoding/Viterbi Decoding and QPSK Modulation(QPSK/IDR),1998

3 John G.Proakis. Digital Communications. Beijing: Publishing House of Electronics Industry,2001

4 劉玉君.信道編碼. 鄭州:河南科學(xué)技術(shù)出版社,2001

5 宋萬杰,羅 豐,吳順君. CPLD技術(shù)及其應(yīng)用. 西安:西安電子科技大學(xué)出版社,2000