數(shù)字圖像穩(wěn)定是圖像序列處理中得一項重要的前處理步驟。早期的方法是對攝像機(jī)本身的機(jī)械和光路進(jìn)行穩(wěn)定,隨著數(shù)字技術(shù)的發(fā)展,可以對采集到的圖像進(jìn)行處理,使圖像在顯示器上能夠穩(wěn)定地顯示,同時也為了更好地為后續(xù)處理提供穩(wěn)定的圖像序列,如圖像拼接、圖像增強(qiáng)、信息融合、目標(biāo)追蹤、目標(biāo)識別等各種圖像處理技術(shù)的綜合運用。在實現(xiàn)實時圖像穩(wěn)定系統(tǒng)方面,由于圖像計算量大,必須選用高性能數(shù)字信號處理器。目前實現(xiàn)實時圖像處理的主要方式有4種:1)基于通用PC機(jī);2)基于通用DSP;3)基于專用或多DSP;4)基于可編程FPGA或DSP+FPG。在通用PC機(jī)上可方便地進(jìn)行各種圖像算法的仿真試驗,但是這種方法只能在實驗室進(jìn)行,難以現(xiàn)場應(yīng)用。其中基于通用DSP這種方案的優(yōu)點在于,價格便宜、資料豐富、開發(fā)相對簡單,并且處理速度也隨著器件性能提高,已經(jīng)能滿足圖像穩(wěn)定所需要的實時處理,形成脫機(jī)系統(tǒng)。針對實時數(shù)字圖像穩(wěn)定處理,介紹一種采用高性能系列的DSP C6416,開發(fā)出一套數(shù)字圖像處理系統(tǒng)。該系統(tǒng)采用雙口RAM作為高速數(shù)據(jù)輸入輸出緩沖通道,由CPLD進(jìn)行系統(tǒng)的邏輯控制,DSP的EDMA完成數(shù)據(jù)的片內(nèi)片外傳送,通過配置和軟件優(yōu)化,最終完成了系統(tǒng)的高度實時運行。

1 穩(wěn)像方法和步驟

數(shù)字圖像穩(wěn)定處理過程主要由3部分組成:運動矢量估計模塊(ME),運動矢量補(bǔ)償模塊(MC)和圖像序列合成模塊(IC)。通過ME模塊找到幀間運動偏移,由MC模塊進(jìn)行圖像拼接完成運動補(bǔ)償,最后經(jīng)IC模塊進(jìn)行圖像剪裁輸出。

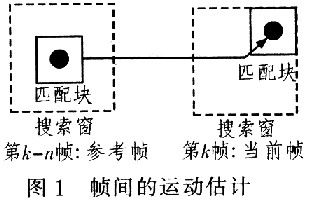

運動矢量估計模塊中,通過比較當(dāng)前圖像和參考圖像中相同的部分,找到兩幀圖像問的偏移量,即運動矢量,廣泛應(yīng)用于視頻處理與編碼,如圖1所示。

圖1中用實線所畫的方框表示匹配塊,虛線所畫的方框表示搜索窗。假定第k幀為當(dāng)前幀,為了計算第k幀相對于第k-n幀的運動偏移量。在第k-n幀的中心位置選擇一個N×N像素大小的匹配塊,同時在第k幀上選擇一個M×M(M>N)大小的搜索窗,搜索窗的中心位置與第k幀的匹配塊中心位置重合,通過用式(1)比較兩幅圖像間所有相應(yīng)像素間絕對差的累和VSAD(Sum of Absolute Difference),在搜索窗內(nèi)找出和匹配塊圖像最匹配的位置,即VSAD最小值的位置。該匹配位置坐標(biāo)和搜索窗中心點坐標(biāo)的相對位置(△x,△y),即為兩幀圖像的偏移運動矢量。

式中 ,分別為參考圖像和當(dāng)前圖像(i,j)位置的像素強(qiáng)度。

,分別為參考圖像和當(dāng)前圖像(i,j)位置的像素強(qiáng)度。

獲得的圖像序列之間的運動矢量參數(shù)后,糾正當(dāng)前圖像,使其恢復(fù)到正確的位置,獲得相對穩(wěn)定的圖像序列,然后送到相應(yīng)的顯示裝置或存儲介質(zhì)。

2 穩(wěn)像系統(tǒng)的方案設(shè)計

TMS320C6416是TI公司最新推出的高性能DSP,該器件擁有8個并行處理單元,工作頻率為600 Hz,最高處理速度可達(dá)4800M/s(MFLOPS)。采用類似RISC的超常指令字(VLIW)結(jié)構(gòu),在最好的情況下,TMS320 C64X系列的DSP在一個指令周期可同時執(zhí)行8條32位有效指令,因此可以達(dá)到極高的處理性能。

2.1 系統(tǒng)組成

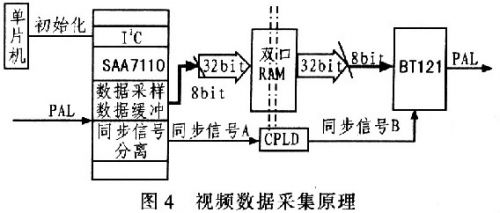

為適合高速圖像采集與處理,采用CPLD+DSP的應(yīng)用方案,由于DSP只專注數(shù)據(jù)處、理,但缺乏控制能力,利用高速邏輯器件CPLD配合DSP完成實時任務(wù)控制與處理,是系統(tǒng)的最佳組合。經(jīng)過比較,選用XC95144XL作為CPLD控制器,主處理DSP TMS320C6416系列器件進(jìn)行圖像處理計算。該系統(tǒng)結(jié)構(gòu)如圖2所示。

該系統(tǒng)輸入輸出都為標(biāo)準(zhǔn)模擬視頻信號,設(shè)計采集圖像大小為512×512像素,速度為30~60幀/s的實時采集。攝像頭輸入模擬視頻信號后,經(jīng)過SAA7110進(jìn)行A/D轉(zhuǎn)換和信號分離后,進(jìn)入輸入端高速數(shù)據(jù)緩沖區(qū)。輸出端緩存中的數(shù)據(jù),通過BT121進(jìn)行D/A轉(zhuǎn)換后,合成為標(biāo)準(zhǔn)模擬視頻信號,可直接送監(jiān)視器顯示。用邏輯器件CPLD控制系統(tǒng)的工作時序。為適應(yīng)高速數(shù)據(jù)吞吐,輸入輸出緩沖存儲器選用了雙端口RAM。

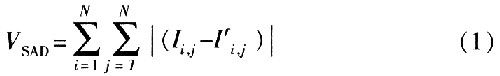

2.2 CPLD控制

系統(tǒng)的邏輯控制器是100引腳的XC95144,其主要工作是控制輸入/輸出幀存,以便DSP將存在其中的處理好的圖像數(shù)據(jù)讀出,并在同步控制信號和消隱信號的協(xié)同下形成標(biāo)準(zhǔn)視頻輸出信號,送到監(jiān)視器顯示。圖3給出了邏輯控制的原理框圖。

CPLD的邏輯控制的工作包括:1)根據(jù)SAA7110分離出的同步信號,經(jīng)過邏輯判斷后,給出BT121需要的同步信號;2)由于SAA7110輸出的LLC2時鐘與采樣時鐘、輸出時鐘是同步的,因而以LLC2作為采樣數(shù)據(jù)存儲和同步控制子系統(tǒng)的時鐘,CPLD內(nèi)部計數(shù)器進(jìn)行數(shù)據(jù)采樣計數(shù),產(chǎn)生偏移地址,以控制輸入/輸出緩沖讀寫數(shù)據(jù),使用LLC2時鐘也避免了使用外部時鐘需要解決的信號相互間的同步和鎖相:3)計數(shù)器產(chǎn)生控制中斷,通知DSP啟動數(shù)據(jù)讀/寫EDMA通道和進(jìn)行數(shù)據(jù)轉(zhuǎn)移;4)低位地址A0和A1進(jìn)行譯碼產(chǎn)生Bank Enable信號,送到雙口RAM以進(jìn)行數(shù)據(jù)位選通。由于輸入/輸出緩存具有對稱的硬件結(jié)構(gòu),所以XC95144在進(jìn)行地址計數(shù)時,產(chǎn)生兩套相同Bank信號和地址偏移,供輸入和輸出雙口RA-M。

3 數(shù)字圖像數(shù)據(jù)的采集與輸出

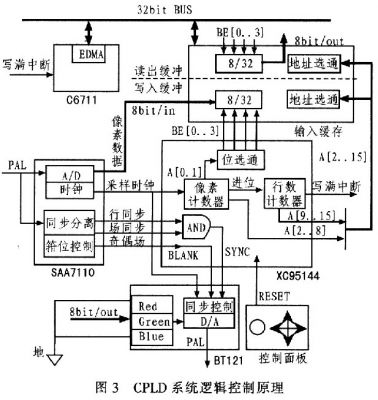

3.1 數(shù)據(jù)采集

系統(tǒng)的設(shè)計視頻信號采集能力是從CCD獲得模擬視頻信號中采集到512×512大小的數(shù)字圖像,并通過幀緩存——異步靜態(tài)雙端口存儲器(dual-port RAM),經(jīng)DSP的EDMA通道送到SDRAM中。采集模塊的結(jié)構(gòu)如圖4所示。

SAA7110的初始化通過I2C總線對其內(nèi)部控制寄存器進(jìn)行相應(yīng)設(shè)置而實現(xiàn),該系統(tǒng)將DSP上的McBSP(多通道緩沖串口)的兩個引腳與SCL和SDA相連,將McBSP的引腳配置成通用I/O口,這樣就能通過編寫DSP程序,在上電時通過DSP的多通道緩沖串口配置SAA7110。

3.2 數(shù)據(jù)位拼接

由于SAA7110和BT121都是8 bit精度器件,而雙口RAM的每邊都是36 bit精度的存儲器,但雙口RAM的4個BANK通道,每個BANK各9 bit,共36 bit數(shù)據(jù),可通過BEO~BE3信號選通,因此只有將SAA7110和BT121的8 bit數(shù)據(jù)進(jìn)行拼接后才能送到雙口RAM。由于雙口RAM的每個BANK都是9 bit,SAA7110和BT121的8 bit數(shù)據(jù)總線接在每個BANK的低8 bit,忽略最高位第9位,直接地,形成8 bit的數(shù)據(jù)精度,完成不同數(shù)據(jù)精度位器件間的握手。

3.3 數(shù)據(jù)輸出

處理完的圖像數(shù)據(jù),經(jīng)D/A轉(zhuǎn)換器BT121進(jìn)行數(shù)模轉(zhuǎn)換后,送到顯示器,這個過程必須在嚴(yán)格的同步時鐘控制下進(jìn)行。SAA7110給出的同步信號包括水平同步、垂直同步、奇偶場和采樣時鐘,而BT121的同步信號只有空白信號(BLANK)、合成信號(SYNC)和轉(zhuǎn)換時鐘。當(dāng)BLANK信號為1時,BT121才進(jìn)行D/A轉(zhuǎn)換,SYNC信號為1時才打開D/A通道。所以,2個器件間的同步信號不能直接握手,必須經(jīng)過一定的邏輯轉(zhuǎn)換。S-AA7110的同步信號引腳接到CPLD,由CPLD經(jīng)過一定的邏輯運算后,送出符合BT121同步要求的信號。

4 系統(tǒng)工作方法和優(yōu)化配置

4.1 系統(tǒng)工作方式

系統(tǒng)上電后,DSP從Flash讀入1 K大小的程序數(shù)據(jù),該引導(dǎo)程序繼續(xù)將其他主程序調(diào)入SDRAM中,在以后的運行過程中,DSP自動將運行所需程序從SDRAM裝入片內(nèi)存儲器。同時89C5l單片機(jī)對SAA7110進(jìn)行初始化。當(dāng)DSP準(zhǔn)備就緒后,通知CPLD開始控制向輸入端雙端口RAM寫入由S-AA7110采集的視頻圖像數(shù)據(jù)。輸入緩存的存儲空間分為奇、偶場空間,寫滿一場后向DSP發(fā)送中斷信號,DSP收到該中斷信號后以EDMA方式將數(shù)據(jù)讀入SDRAM等待處理。在DSP讀走和處理該部分?jǐn)?shù)據(jù)時,CPLD繼續(xù)控制向輸入緩存的另一部分空間寫入下一場采樣數(shù)據(jù)。當(dāng)DSP處理完上一場數(shù)據(jù)后,等待下一場視頻數(shù)據(jù)的寫滿信號。采用雙端口RAM作為系統(tǒng)的輸入輸出緩存,有效地避免了讀寫訪問沖突和系統(tǒng)總線的沖突,極大提高了系統(tǒng)的執(zhí)行效率。

4.2 配置L2 Cache和Memory的比例

由于片內(nèi)RAM與CPU工作在同一時鐘頻率,比片外RAM性能高得多。C64的兩級緩存機(jī)構(gòu)工作特點為:片內(nèi)分為兩級存儲結(jié)構(gòu)(L1和L2),L1不能設(shè)置為映射寄存器。L1又分為L1P和L1D,L1D指的是第1級的數(shù)據(jù)緩沖,為128 K字節(jié)的兩路成組相連結(jié)構(gòu)緩存。L2是第2級片內(nèi)緩存,大小為l 024 K(可同時存儲程序和數(shù)據(jù))。L1P和L1D都可以對L2進(jìn)行存取,當(dāng)L1D或L1P中沒有運行所需要的數(shù)據(jù)時(即產(chǎn)生cache miss時),首先向L2發(fā)出申請,當(dāng)L2中也發(fā)生cache miss時,將申請轉(zhuǎn)發(fā)給EDMA。申請的轉(zhuǎn)發(fā)將嚴(yán)重影響系統(tǒng)運行效率。所以根據(jù)算法數(shù)據(jù)流特性配置好兩極緩存的大小,預(yù)先將待處理的數(shù)據(jù)讀入,降低cache miss的次數(shù)以提高系統(tǒng)實時性。

以塊匹配運動估計為例,匹配塊32×32 pixel=1 K字節(jié),加上旋轉(zhuǎn)角度范圍:±7°,步長為O.2°,共產(chǎn)生70個旋轉(zhuǎn)1 K的小圖像;搜索窗為96×96 pixel=9 K字節(jié),共10 K字節(jié),所有待進(jìn)行運動估計的圖像數(shù)據(jù)為80 K,完全可以讀入L2Cache。這些數(shù)據(jù)可以用ODMA將數(shù)據(jù)全部讀入片內(nèi)L2。而這些數(shù)據(jù)是從一幀完整的圖像中“扣出”的,所以搬移方式采用2D-1D的方式,QDMA支持這種高效的數(shù)據(jù)傳輸能方法。

4.3 基于EDMA加快數(shù)據(jù)傳輸

當(dāng)使用雙緩沖結(jié)構(gòu)的時候,EDMA是另一種去除多余CPU開銷的重要機(jī)制。利用EDMA,可實現(xiàn)片內(nèi)存儲器(L2SRAM)、片內(nèi)外設(shè),以及外部空間之間的數(shù)據(jù)轉(zhuǎn)移。合理利用EDMA,還可以提高程序性能,由于圖像處理中的數(shù)據(jù)對象通常以8 bit為一單位,利用DMA的數(shù)據(jù)交織功能把來自圖像不同區(qū)域的4個數(shù)據(jù)并接為一個32位數(shù)據(jù),大幅度地提高效率。

系統(tǒng)采用“乒乓”結(jié)構(gòu)的數(shù)據(jù)交換,所以奇場和偶場的起始信號觸發(fā)EDMA通道中斷,雖然傳送數(shù)據(jù)的源地址相同,但目的地址卻不同。而C64的EDMA控制器提供了一種稱為連接(linking)的傳輸機(jī)制,可以將不同的傳輸參數(shù)組連接起來,組成一個傳輸鏈,為同一通道服務(wù)。在鏈中,一個傳輸結(jié)束后,自動裝載下一次傳輸所需要的事件參數(shù)。根據(jù)這個特點,為每個EDMA通道配置兩組參數(shù),用連接的方式完成“乒乓”結(jié)構(gòu)的數(shù)據(jù)讀寫。

5 算法程序優(yōu)化

由于圖像處理的數(shù)據(jù)量大,數(shù)據(jù)處理相關(guān)性高,并且具有嚴(yán)格的幀、場時間限制,因此如何針對圖像處理的特點對DSP進(jìn)行優(yōu)化編程,充分發(fā)揮其性能就成為提高整個系統(tǒng)性能的關(guān)鍵。主要在下面方面的優(yōu)化方法提高C代碼的性能:

1)使用內(nèi)聯(lián)函數(shù) C6000編譯器提供的內(nèi)聯(lián)函數(shù)(intrinsic functions)。內(nèi)聯(lián)函數(shù)是直接映射為內(nèi)聯(lián)的C6000指令的特殊函數(shù),可以快速優(yōu)化C代碼。

2)使用字訪問短型數(shù)據(jù) C6000的內(nèi)聯(lián)函數(shù)中的某些指令,如_add2()是對存儲在32位寄存器的高16位和低16位字段進(jìn)行操作。當(dāng)對一連串短型數(shù)據(jù)進(jìn)行操作時,可使用字(整型)一次訪問2個短型數(shù)據(jù),減少對內(nèi)存的訪問次數(shù)。

3)人工干預(yù)軟件流水 流水是用來安排循環(huán)指令,并使這個循環(huán)的多次疊代并行執(zhí)行的一種技術(shù),通過線性匯編指令,并行處理數(shù)據(jù)處理指令。

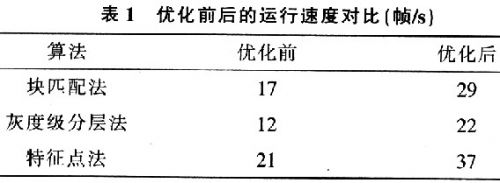

通過以上3種方法優(yōu)化,程序執(zhí)行效率提高70%以上,表1中列出各種算法速度做50次運算的平均值。

實際上,在程序優(yōu)化方面,還有很多的工作可作。另外,本實驗室前期開發(fā)的基于TMS320C6711型DSP的圖像開發(fā)板,工作頻率在200 MHz,優(yōu)化后對256×256大小的圖像進(jìn)行10~13幀/s的圖像穩(wěn)定,尚不能達(dá)到實時。而基于TMS320C6416的處理板,不優(yōu)化就能達(dá)到18~22幀/s的處理速度,經(jīng)過簡單優(yōu)化后,如提前進(jìn)行圖像塊旋轉(zhuǎn)并讀入片內(nèi),展開循環(huán),就能達(dá)到30幀/s的實時處理。現(xiàn)已移植的算法包括:基于快速搜索的塊匹配法、灰度級分層法、邊緣匹配法,各種算法都完全能夠進(jìn)行實時運行。

6 結(jié)論

該系統(tǒng)通過選用CPLD+DSP,既能保證系統(tǒng)的執(zhí)行速度,也能保證可靠的邏輯控制。該系統(tǒng)實現(xiàn)一個比較完整的圖像采集、傳輸、處理和送顯的硬件實驗系統(tǒng),由CPLD對系統(tǒng)的運行邏輯進(jìn)行控制,通過對編寫在DSP上運行的圖像處理程序進(jìn)行優(yōu)化后,能夠?qū)崿F(xiàn)大小為512×512像素圖像的實時穩(wěn)定。該穩(wěn)像系統(tǒng)作為一個獨立的圖像處理系統(tǒng),可完成多方面的圖像處理功能,也為其他基于DSP的圖像處理平臺的設(shè)計提供了參考。

本文來源于與非網(wǎng) http://www.eefocus.com

原文地址:http://www.eefocus.com/article/10-09/567911283850170.html