摘要:針對(duì)通信中的回波問題,,基于自適應(yīng)濾波的LMS算法,設(shè)計(jì)了自適應(yīng)回波抵消器,。并基于利用FPGA芯片,,在DSP Builder平臺(tái)上,有效結(jié)合MatLab/Simulink和Quanus II設(shè)計(jì)工具,,根據(jù)模塊化設(shè)計(jì)思想實(shí)現(xiàn)了LMS算法自適應(yīng)回波抵消器硬件電路設(shè)計(jì),。軟件仿真和系統(tǒng)FPGA硬件實(shí)測(cè)結(jié)果表明,該設(shè)計(jì)方法使回波抵消器的FPGA硬件實(shí)現(xiàn)更加簡(jiǎn)便快捷,。

關(guān)鍵詞:DSP Builder,;回波抵消器;FPGA

在數(shù)字通信,、衛(wèi)星通信等系統(tǒng)中,,不同程度的存在回波現(xiàn)象,影響了通信質(zhì)量,。為了消除回波可以采用回波抵消器,,它能估計(jì)回波路徑的特征參數(shù),以產(chǎn)生一個(gè)估計(jì)的回波信號(hào),,然后從接收信號(hào)中減去該信號(hào),,以實(shí)現(xiàn)回波抵消,。而一般采用自適應(yīng)濾波器模擬回波路徑,可以跟蹤回波路徑的變化,。

DSP Builder是Ahera公司推出的面向DSP開發(fā)的系統(tǒng)級(jí)工具,,它作為Matlab的一個(gè)Simulink工具箱出現(xiàn),使得用FPGA設(shè)計(jì)的DSP系統(tǒng)完全可以通過圖形化界面進(jìn)行設(shè)計(jì)和仿真,。

文中介紹以DSP Builder為平臺(tái)完成自適應(yīng)回波抵消器的FPGA電路設(shè)計(jì),,用FPGA驗(yàn)證設(shè)計(jì)電路的正確性和可靠性。

1 自適應(yīng)回波抵消器原理

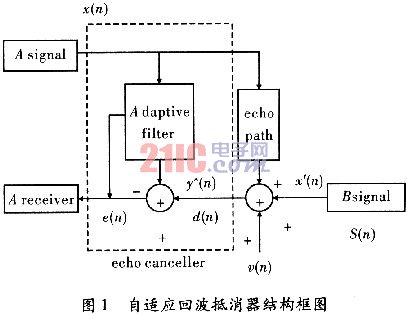

自適應(yīng)回波抵消結(jié)構(gòu)框圖,,如圖1所示,。

圖1中s(n)表示B信號(hào);x’(n)表示A信號(hào)產(chǎn)生的回波,;v(n)為近端環(huán)境噪聲,;y’(n)是濾波器模擬的回波信號(hào);e(n)是殘留回波信號(hào)或誤差信號(hào),。信號(hào)d(n)由B信號(hào)s(n)和回波x’(n)及噪聲組成,,即d(n)=x’(n)+s(n)+v(n)。假定模擬回波信號(hào)估計(jì)為

![]()

式中,,ωk(n)為自適應(yīng)濾波器的時(shí)變系數(shù),,從信號(hào)d(n)中減去模擬回波y’(n)信號(hào)后的殘留回波信號(hào)或誤差信號(hào)為

![]()

當(dāng)自適應(yīng)濾波器的單位脈沖響應(yīng)能很好地模擬回波通道的傳遞函數(shù)時(shí),可以認(rèn)為時(shí),,從而有e(n)=s(n)+v(n),,這樣傳向遠(yuǎn)端的信號(hào)中不包括回波信號(hào)x’(n),即回波被抵消,。

其中,回波抵消器的主要部分自適應(yīng)濾波器所用算法選擇LMS算法,,其迭代公式為

![]()

式中,,X(n) =[X(n),X(n-1),,X(n-2),,…,X(n-M+1)]T表示時(shí)刻n時(shí)的輸入信號(hào)矢量,,由最近M個(gè)信號(hào)采樣值構(gòu)成,,W(n)=[W0(n),Wl(n),,…,,WM-1(n)]T表示n時(shí)刻自適應(yīng)濾波器的系數(shù)矢量估值,μ是控制穩(wěn)定性和收斂速度的步長(zhǎng)參量,。

2 FPGA硬件設(shè)計(jì)

設(shè)計(jì)選用FPGA是Altera公司Cyclone系列的EPlCl2Q240C8,。FPGA中I/O端口可自由定義,,電路設(shè)計(jì)方便、編程靈活,、不易受外部干擾,。系統(tǒng)編譯環(huán)境采用QuartusⅡ,頂層設(shè)計(jì)為圖形化方式,。芯片模塊劃分為分頻模塊,、D/A轉(zhuǎn)換模塊和回波抵消器模塊。分頻模塊采用VHDL語(yǔ)言編程實(shí)現(xiàn),,D/A轉(zhuǎn)換模塊采用硬件電路實(shí)現(xiàn),,同波抵消器模塊用DSPBuilder軟件進(jìn)行設(shè)計(jì)。

2.1 分頻模塊設(shè)計(jì)

分頻模塊是將外部時(shí)鐘進(jìn)行分頻設(shè)定,,得到系統(tǒng)內(nèi)部DA模塊和回波抵消器模塊所需要的時(shí)鐘,。分頻模塊的外部時(shí)鐘輸入頻率為50 MHz,8分頻后產(chǎn)生的時(shí)鐘頻率約為6 MHz,。

2.2 回波抵消器模塊設(shè)計(jì)

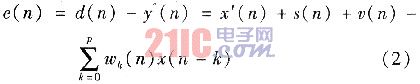

該部分采用層次化的設(shè)計(jì)方法,。利用DSP Builder模塊構(gòu)建自適應(yīng)算法部分,根據(jù)LMS算法迭代公式(4)和濾波器的估計(jì)輸出式(2),,建立加權(quán)分量模型,。如圖2(a)所示。

在圖2(a)中,,第i個(gè)延時(shí)單元的輸入信號(hào)為x(n),,延時(shí)后的輸出信號(hào)為x(n-1),同時(shí)輸入信號(hào)x(n)產(chǎn)生一個(gè)乘積y’(n)=ω(n)x(n),,由于是濾波器的估計(jì)輸出是一系列權(quán)值分量與輸入矢量的各分量乘積之和,。因此,除第一級(jí)外,,后續(xù)單元必須加上前一級(jí)的加權(quán)單元的輸出,。封裝后,則可以根據(jù)濾波器階數(shù)的不同而相應(yīng)調(diào)整,,以實(shí)現(xiàn)多級(jí)級(jí)聯(lián),。尤其是在構(gòu)造階數(shù)可變和階數(shù)較大的濾波器時(shí)更能顯出其靈活性。然后將封裝后的加權(quán)分量單元依照階數(shù)級(jí)聯(lián),,并再次封裝即構(gòu)成抵消器模塊,。可運(yùn)用于頂層模型中,。

在頂層系統(tǒng)模型中連接各子模塊,,如圖2(b)所示,圖中兩個(gè)信號(hào)源sin2,,sin1采用正弦信號(hào)發(fā)生器實(shí)現(xiàn),,利用正弦查找表產(chǎn)生正弦波數(shù)據(jù),,函數(shù)調(diào)用格式為lOsin([0:2π/2∧4:2π])和5sin[0:2π/2∧6:2π],其輸入地址分別為4位和6位,,輸出為16位,。Dixiaoqi模塊由圖2(a)級(jí)聯(lián)封裝得到,模塊Parallel to serial為并行/串行轉(zhuǎn)換器,。

設(shè)計(jì)中,,因語(yǔ)音信號(hào)頻率可以看作約為3.4 kHz,所以信號(hào)采樣頻率設(shè)為8 kHz,,假設(shè)回波延遲2.5 ms(小于回波對(duì)聽覺產(chǎn)生干擾的范圍20 ms),,考慮收斂速度和實(shí)現(xiàn)情況,步長(zhǎng)采用0.1,,計(jì)算得出濾波器階數(shù)20,。

2.3 D/A轉(zhuǎn)換模塊設(shè)計(jì)

利用Texas Instruments公司的D/A芯片TLC5620,并輔助使用4輸入與門SN74HC08M和運(yùn)算放大器LM358AM,,構(gòu)建數(shù)模轉(zhuǎn)換器,。TLC5620是8位電壓輸出的數(shù)模轉(zhuǎn)換器,需5V外接電壓,,有4個(gè)輸出端口可以選擇,。利用擴(kuò)展插槽與FPGA連接,信號(hào)接119腳,,時(shí)鐘由所編程序在FPGA內(nèi)實(shí)現(xiàn),,通過73腳與TLC5620連接,控制信號(hào)通過63腳連接TLC5620,。

3 DSP Builder仿真和FPGA驗(yàn)證

通過Simulink仿真得到波形,,如圖3(a)所示,圖中第一行為返回A聽筒的誤差e信號(hào)波形,,第二行為輸入話筒的所有信號(hào),,即B信號(hào)與回波信號(hào)之和。由變化的波形可以看出,,隨著自適應(yīng)濾波器的“學(xué)習(xí)”過程,,回波逐漸被抵消,。

利用ModelSim針對(duì)生成的RTL級(jí)VHDL代碼進(jìn)行功能仿真,,設(shè)置信號(hào)為模擬形式,如圖3(b)所示,,圖中為減去回波后的誤差信號(hào),,與Simu-link仿真結(jié)果一致。

使用ModelSim完成RTL級(jí)功能仿真,,其仿真結(jié)果并不能精確反映電路的全部硬件特性,,進(jìn)行門級(jí)的時(shí)序仿真仍然十分重要,。在Quartus Ⅱ下編譯后進(jìn)行時(shí)序仿真,其仿真波形,,如圖3(c)所示,。

把回波抵消器模型轉(zhuǎn)化生成圖元文件,作為一個(gè)子模塊在頂層系統(tǒng)中調(diào)用,。在QuartusⅡ環(huán)境下,,調(diào)用各個(gè)子模塊,構(gòu)成完整的系統(tǒng)原理圖設(shè)計(jì),,然后進(jìn)行編譯,、仿真和引腳分配等工作。最后下載到FPGA芯片中,,對(duì)硬件進(jìn)行測(cè)試,,采用SignalTapⅡ?qū)嶋H測(cè)得的值如圖4所示,驗(yàn)證本設(shè)計(jì)的正確性,。

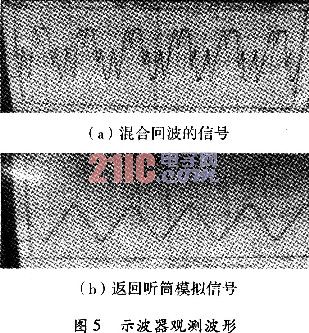

最后通過D/A轉(zhuǎn)換電路接入示波器,。觀測(cè)結(jié)果,如圖5(a),,圖5(b)所示,,通過比較混合回波的信號(hào)和經(jīng)過抵消后得到的返回聽筒的消除回波以后的信號(hào),可以看出回波已基本消除,,設(shè)計(jì)達(dá)到目的,。通過測(cè)試,回波衰減率約為25 dB,,基本達(dá)到ITUTG.167標(biāo)準(zhǔn)中回波衰減率至少20 dB的要求,。

4 結(jié)束語(yǔ)

采用DSP Builder進(jìn)行設(shè)計(jì),使用圖形界面,,用模塊化設(shè)計(jì)代替以往的VHDL語(yǔ)言編程,,并綜合多種設(shè)計(jì)工具,便于研究者迅速地將算法級(jí)的構(gòu)思應(yīng)用于系統(tǒng)設(shè)計(jì)中,,從而可以專注于系統(tǒng)算法的設(shè)計(jì),,避免了繁瑣的語(yǔ)言編程和電路設(shè)計(jì),提高了設(shè)計(jì)速度,,縮短設(shè)計(jì)周期,,為產(chǎn)品開發(fā)節(jié)約了研發(fā)時(shí)間。