1 引言

1553B 總線是MIL-STD-1553B 總線的簡稱,其全稱為飛機(jī)內(nèi)部時分制指令/響應(yīng)式多路傳輸數(shù)據(jù)總線,是一種滿足實時性、數(shù)據(jù)完整性和系統(tǒng)可靠性的通用機(jī)載串行多路總線標(biāo)準(zhǔn),該總線標(biāo)準(zhǔn)首先在航空工業(yè)中得到廣泛應(yīng)用。隨著衛(wèi)星技術(shù)的發(fā)展,1553B 總線在國內(nèi)航天領(lǐng)域的應(yīng)用也日益廣泛,作為與之配套的地面檢測設(shè)備也需要具有1553B 總線接口 的通信板卡。

2 方案設(shè)計

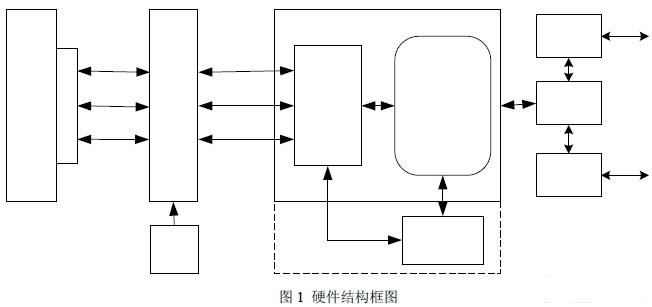

本板卡是基于PCI 總線的1553B 總線接口卡,要實現(xiàn)的功能是利用PCI 總線作為媒介, 實現(xiàn)計算機(jī)控制1553B 總線BC 端和RT 端進(jìn)行數(shù)據(jù)傳輸?shù)墓δ埽罱K在衛(wèi)星地面測試過程中 實現(xiàn)由計算機(jī)對遠(yuǎn)程終端的設(shè)備進(jìn)行測試和控制。板卡硬件結(jié)構(gòu)如圖1 所示,主要由PCI 協(xié)議接口芯片、1553B 總線控制器、收發(fā)器和變壓器等組成。

3 PCI-1553B 接口卡功能實現(xiàn)

3.1 1553B 協(xié)議

1553B 總線系統(tǒng)中包含三種不同類型的終端:總線控制器(BC)、總線監(jiān)視器(MT)和 遠(yuǎn)程終端(RT)。由于1553B 數(shù)據(jù)總線采用的是主從控制方式的總線控制,主節(jié)點即總線控 制器(BC)負(fù)責(zé)控制整個網(wǎng)絡(luò),控制數(shù)據(jù)流從BC 流向RT、RT 流向BC 以及RT 流向RT。數(shù) 據(jù)流的基本形式是消息,協(xié)議規(guī)定一個消息傳輸?shù)耐暾^程由指令字、數(shù)據(jù)字(或指令字和狀態(tài)字)組成。每一種字長為20 位,有效消息位是16 位,每種字的前三位為同步頭,最后一位是奇偶校驗位。在本系統(tǒng)中,主要數(shù)據(jù)傳輸方式是BC→RT 和RT→BC 兩種。 BC 端向RT 端的數(shù)據(jù)傳輸過程是首先由BC 發(fā)出一個接收指令字及規(guī)定數(shù)目的數(shù)據(jù)字到 RT,后者在核實消息后發(fā)回一個狀態(tài)字給BC,指令字和數(shù)據(jù)字應(yīng)以沒有字間間隔的連續(xù)形 式發(fā)出。

RT 端向BC 端的數(shù)據(jù)傳輸過程是首先由BC 向RT 發(fā)出一個發(fā)送指令字,該RT 在核實指令字后,發(fā)回一個狀態(tài)字給BC,繼之以規(guī)定數(shù)目的數(shù)據(jù)字,狀態(tài)字和數(shù)據(jù)字應(yīng)以沒有字間 間隔的連續(xù)形式發(fā)出。

3.2 1553B 總線協(xié)議控制器的實現(xiàn)

1553B 總線協(xié)議控制器是本板卡構(gòu)成的關(guān)鍵。市場上實現(xiàn)1553B 總線協(xié)議的芯片很多,目前應(yīng)用比較廣泛的是美國數(shù)據(jù)設(shè)備公司(DDC)的BU-61580,它雖然能夠完整的實現(xiàn) 1553B 總線協(xié)議,但缺點是設(shè)置比較復(fù)雜、體積比較大、功耗比較高。本設(shè)計采用Condor Engineering 公司的FlightCORE-1553 IP 核作為總線協(xié)議控制器,它完全滿足1553B 總線協(xié) 議,為主處理器和1553B 總線提供了完整、靈活的接口,能夠?qū)崿F(xiàn)總線控制器(BC)、遠(yuǎn)程 終端(RT)和總線監(jiān)視器(BM)三種模式,并且適應(yīng)ALTEA 和XILINX 大部分型號的FPGA, 與BU-61580 等協(xié)議芯片相比,具有使用靈活、功耗低、節(jié)省印制板面積等特點。

該總線控制器內(nèi)部有 1K×16bits 的存儲空間,在存儲空間的低地址區(qū)是硬件寄存器、固件保留區(qū)和文件寄存器,通過對這些寄存器的設(shè)置,可以方便地將控制器配置為BC、RT 或者BM。

下面對常用的寄存器進(jìn)行說明: 1. 配置寄存器:用來選擇工作模式,即 BC、RT 或BM;

2. 控制寄存器:用來啟動相應(yīng)的工作模式;

3. 中斷使能寄存器:設(shè)置產(chǎn)生中斷的條件;

4. 中斷狀態(tài)寄存器:當(dāng)中斷產(chǎn)生時,固件將該寄存器相應(yīng)位設(shè)置為有效,主處理器通 過讀該寄存器判斷是否有中斷發(fā)生;

5. 自檢寄存器:該寄存器具有只讀屬性,表明工作狀態(tài)。 實際應(yīng)用中,該控制器需要4K 字的存儲空間才能正常工作,所以需要擴(kuò)充存儲空間, 考慮到控制器接收處理總線數(shù)據(jù)后計算機(jī)能及時獲取而又不影響其正常工作,采用雙口RAM 比較合適,其中控制器前1K 字的存儲空間和雙口RAM 的地址空間是重疊的。

3.3 PCI 功能的實現(xiàn)

PCI 協(xié)議接口芯片采用PLX9054,通過XILINX 的FPGA 實現(xiàn)PLX9054 與1553 總線協(xié)議的通信。當(dāng)計算機(jī)啟動時,9054 需要串行EEPROM 為其提供一些必要的配置信息以實現(xiàn)對PCI 配置寄存器和本地寄存器的設(shè)置,這些信息除了局部空間的范圍和基地址外,還包括設(shè)備信 息和中斷資源等,這些需要我們事先燒寫到EEPROM 中,本文EEPROM 采用93LC56B。

實際應(yīng)用中,需要根據(jù)存儲空間大小配置相應(yīng)的9054 的地址空間,1553B 總線控制器 本身含有1K 字的寄存器空間,為了擴(kuò)大存儲器空間,在FPGA 內(nèi)例化了8K×16bits 的雙口 RAM。在9054 的本地端,將地址總線設(shè)為32 位,每一次32 位的讀寫操作僅對其低16 位進(jìn) 行,高16 位未用,因此實際需要配置2 倍于雙口RAM 大小的空間,即32KByte,故EEPROM 中的局部地址空間0 范圍寄存器設(shè)為FFFF8000,局部地址空間0 描述寄存器設(shè)為4B430043。

3.4 PCI 總線和1553B 總線的橋接

在PCI 總線一邊,9054 的PCI 總線端需要和主機(jī)上的PCI 插槽進(jìn)行連接。由于9054 是 專用的PCI 協(xié)議芯片,所以它的PCI 端可以直接通過插卡上的引線和PCI 插槽連接。

9054 的本地端和1553B 總線控制器HOST 端通過FPGA 實現(xiàn)邏輯轉(zhuǎn)換。9054 支持三種傳輸模式,即主模式、從模式和DMA 模式,DMA 模式適合突發(fā)的大量數(shù)據(jù)的傳輸,由于1553B 總線的數(shù)據(jù)速率為1Mbps,數(shù)據(jù)量很小,因此采用從模式中的單周期讀寫模式,相對于主模 式而言電路設(shè)計和時序控制也相對簡單。

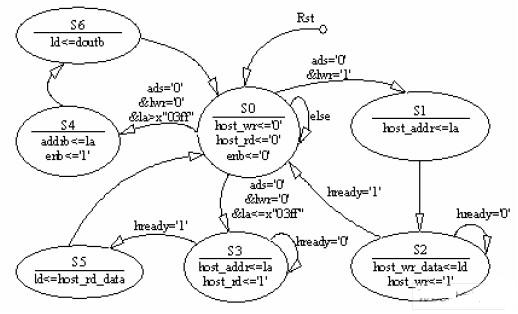

根據(jù)9054 從模式下單周期讀寫時序、1553B 總線控制器HOST 端時序和雙口RAM 時序采 用如圖2 所示的狀態(tài)機(jī)實現(xiàn)PCI 總線對1553B 總線控制器和雙口RAM 空間的讀寫操作。

圖2 狀態(tài)轉(zhuǎn)換圖

當(dāng)9054 的局部總線復(fù)位信號有效后,狀態(tài)機(jī)進(jìn)入S0 狀態(tài),當(dāng)啟動本地總線的單周期寫操作時,在檢測到地址選通信號有效,且寫信號有效后,狀態(tài)機(jī)進(jìn)入S1 狀態(tài),將本地地址 總線賦給1553B 總線控制器的地址總線,狀態(tài)機(jī)進(jìn)入S2 狀態(tài),將本地數(shù)據(jù)總線賦給1553B 總線控制器的數(shù)據(jù)總線,直到數(shù)據(jù)寫入后,狀態(tài)機(jī)重新回到S0 狀態(tài);當(dāng)啟動本地總線單周 期讀操作時,在地址選通信號有效且讀信號有效后判斷本地地址總線,當(dāng)本地地址大于等于 1024 時,訪問雙口RAM 的B 端口,當(dāng)本地地址小于1024 時,訪問1553B 總線控制器內(nèi)的寄 存器,這樣做的好處是防止對雙口RAM 操作時出現(xiàn)讀寫沖突的問題。

3.5 接口卡外圍電路

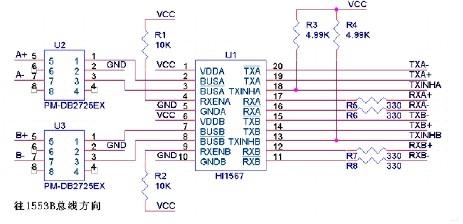

接口卡外圍電路主要包括收發(fā)器、變壓器和 RT 子地址電路等。 收發(fā)器分為接收和發(fā)射兩部分,接收部分的功能是將 1553 總線上傳輸?shù)碾p極性差分曼 徹斯*轉(zhuǎn)化為適合FPGA 輸入的互補(bǔ)CMOS/TTL 電平。發(fā)射部分是接收部分的逆過程,它將互補(bǔ)的CMOS/TTL 電平轉(zhuǎn)為適合1553B 總線傳輸?shù)碾p極性差分曼徹斯*。本設(shè)計收 發(fā)器采用HOLT 公司的HI1567,由于HI1567 的工作電壓是5V,在與IO 電壓非5V 的FPGA 互聯(lián)時需要串接330 歐姆的電阻。

接口卡通過短截線與 1553B 主總線相連。在短截線和收發(fā)器之間需要設(shè)置隔離變壓器,以提供總線驅(qū)動電壓,防止終端因短路引起損壞和接口卡產(chǎn)生的噪聲影響1553B 主總線上的信號。短截線與1553B 主總線的連接方式有兩種:直接耦合和變壓器耦合。直接耦合是直接將短截線連接到主總線。變壓器耦合在直接耦合的基礎(chǔ)上加了一個耦合變壓器,對終端實行兩級隔離,增加了數(shù)據(jù)傳輸?shù)木嚯x,同時提高了系統(tǒng)的可靠性。直接耦合短截線的長度 最大為1 英尺(約0.3 米),而變壓器耦合方式短截線最大可以達(dá)20 英尺(約6 米)。

本文 變壓器采用HOLT 公司的PMDB2725EX,該變壓器提供兩種變壓比,即1:2.5 和1:1.79,分別適應(yīng)直接耦合和變壓器耦合兩種方式。需要注意的是無論采用哪種方式,都必須在1553B 總線和變壓器之間串聯(lián)隔離電阻對總線進(jìn)行短路保護(hù)。收發(fā)器和變壓器電路如圖3 所示。 RT 子地址不僅可以通過板卡上的手動開關(guān)來完成1553B 總線終端RT 地址的設(shè)置,也 可以通過上位機(jī)進(jìn)行軟件設(shè)置。

圖 3 收發(fā)器變壓器電路圖

4 驅(qū)動及應(yīng)用軟件設(shè)計

驅(qū)動程序的基本功能是完成設(shè)備的初始化、對端口的讀寫操作,中斷的響應(yīng)以及調(diào)用。本文采用DDK(驅(qū)動程序開發(fā)包)來編寫驅(qū)動程序,這里就不做詳細(xì)介紹。 應(yīng)用軟件采用 Visual C++編寫,完成對PCI 的讀寫操作,進(jìn)而實現(xiàn)控制1553B 總線的 數(shù)據(jù)傳輸。其中,BC 模式下的流程為:

(1)讀取自檢寄存器,判斷工作狀態(tài);

(2)通過配置寄存器,設(shè)置工作模式為總線控制器(BC);

(3)根據(jù)中斷條件設(shè)置中斷使能寄存器;

(4)初始化中斷隊列;

(5)定義BC 塊和發(fā)送接收數(shù)據(jù)緩沖區(qū);

(6)將控制字、命令字和需要發(fā)送的數(shù)據(jù)寫入相應(yīng)的消息塊中;

(7)設(shè)置控制寄存器啟動傳輸;

(8)輪詢中斷狀態(tài)寄存器,如果中斷,進(jìn)入中斷程序,處理相應(yīng)的中斷。

5 結(jié)束語

為實現(xiàn)有效載荷地面測試過程中終端設(shè)備與星上1553B總線上被測試設(shè)備之間的信息交互,需要應(yīng)用1553B總線到計算機(jī)標(biāo)準(zhǔn)接口的通信板卡。本文通過對1553B總線和PCI總線協(xié)議的分析,結(jié)合航天地面測試實際要求提出了一種1553B-PCI總線接口卡的實現(xiàn)方法,給出了硬件結(jié)構(gòu)框圖,部分原理圖和接口控制的FPGA實現(xiàn)。經(jīng)過測試,實現(xiàn)了計算機(jī)通過PCI總線與遠(yuǎn)程終端設(shè)備的信息交互,滿足了實際要求,并在XXX型號地面測試中應(yīng)用。