摘要:低功耗是嵌入式系統(tǒng)的發(fā)展趨勢(shì),也是便攜式嵌入式設(shè)備設(shè)計(jì)中要解決的關(guān)鍵問(wèn)題之一。對(duì)影響嵌入式系統(tǒng)功耗的因素進(jìn)行了分析,指出了降低系統(tǒng)功耗的途徑,從硬件設(shè)計(jì)和軟件設(shè)計(jì)兩個(gè)方面闡述了超低功耗嵌入式系統(tǒng)設(shè)計(jì)的技巧。

關(guān)鍵詞:超低功耗;嵌入式系統(tǒng);硬件設(shè)計(jì);軟件設(shè)計(jì)

無(wú)論是在軍事還是在商業(yè)上的應(yīng)用,便攜式嵌入式系統(tǒng)一般是由可充電電池來(lái)供電的,因此,采用有效的節(jié)能技巧來(lái)改進(jìn)系統(tǒng)的軟硬件設(shè)計(jì),降低系統(tǒng)的功耗以增加電池供電設(shè)備的使用時(shí)間,是便攜式嵌入式系統(tǒng)設(shè)計(jì)中需要研究和解決的關(guān)鍵問(wèn)題。

1 影響功耗的因素

1.1 集成電路功耗

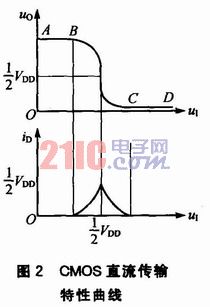

CMOS倒相器在集成電路分析中具有非常重要的意義,常用它來(lái)進(jìn)行集成電路延遲時(shí)間和功耗的分析。CMOS倒相器如圖1所示,圖2是倒相器的直流傳輸特性曲線。

若電路處在靜態(tài)(不發(fā)生狀態(tài)翻轉(zhuǎn))并忽略漏電流的前提下,反相器的功耗幾乎為零,如圖2中的AB段和CD段。當(dāng)電路發(fā)生狀態(tài)翻轉(zhuǎn)時(shí),N管和P管具有同時(shí)導(dǎo)通的一段時(shí)間,此時(shí)從電源通過(guò)2個(gè)管子流向地的電流iD達(dá)到一個(gè)很高的峰值,如圖2對(duì)應(yīng)于BC段的電流。很大的電流意味著較高的功率消耗和熱能的損失,這在時(shí)鐘頻率較高時(shí)尤為突出。時(shí)鐘速度越高意味著每秒鐘狀態(tài)的切換次數(shù)就越多,也意味著更多的電能損耗。除此之外,在工作時(shí)還存在著靜態(tài)漏電功耗,下面對(duì)這2類功耗分別進(jìn)行分析。

1.1.1 動(dòng)態(tài)功耗

CMOS倒相器從一種穩(wěn)定工作狀態(tài)突然轉(zhuǎn)變到另一種穩(wěn)定狀態(tài)的過(guò)程中,將產(chǎn)生附加的功耗,稱之為動(dòng)態(tài)功耗。這一功耗是由2部分組成的,一部分是瞬時(shí)導(dǎo)通功耗PT,另一部分是對(duì)負(fù)載電容充放電所消耗的功率PC,其表達(dá)式為:

![]()

式(1)中,VDD為電源電壓;ITC為2個(gè)管同時(shí)導(dǎo)通所產(chǎn)生的瞬時(shí)電流,不是固定的數(shù)值,如圖2所示;a為活動(dòng)因子,表示電容充放電的平均次數(shù)相對(duì)于開(kāi)關(guān)頻率的比值;CL為進(jìn)行充放電的等效負(fù)載電容,包括柵電容、節(jié)點(diǎn)電容、互連電容等;f為開(kāi)關(guān)頻率,即電路的工作頻率。

1.1.2 靜態(tài)漏電功耗

靜態(tài)漏電功耗是由亞閾值電流和反向偏壓電流造成的。在集成電路中,動(dòng)態(tài)功耗是整個(gè)CMOS集成電路功耗的主要組成部分,一般約占電路總功耗的90%以上,靜態(tài)漏電功耗占電路總功耗的1%以下,因而在大多數(shù)情況下可以忽略。

1.2 其他功耗

①純電阻元件上消耗的功率。電阻為耗能元件,只要電路中使用電阻,就存在著能量消耗。

②有源開(kāi)關(guān)器件在狀態(tài)轉(zhuǎn)換時(shí),電流和電壓比較大,將引起功率消耗。

③非理想元件由于等效電阻的存在而消耗的功率。如電路中的儲(chǔ)能元件電感和電容,理想情況下它們是不消耗能量的,但是實(shí)際使用的電感和電容都存在著等效串聯(lián)電阻(ESR),就意味著能量的消耗。

④印制電路板中的走線上消耗的功率,如電源線由于電阻的存在會(huì)造成電能的損耗,實(shí)際中地線上也存在著電流的流動(dòng)。由于導(dǎo)線阻抗的存在,串聯(lián)單點(diǎn)接地的不同接地點(diǎn)之間會(huì)存在著電位差,因此在這些地線上也存在著能量的消耗。

2 降低系統(tǒng)功耗的途徑

①降低集成電路的動(dòng)態(tài)功耗。根據(jù)式(1)可知,要降低集成電路的動(dòng)態(tài)功耗,途徑有:a.降低活動(dòng)因子,也就是降低電容充放電的平均次數(shù)。b.降低電源電壓。因?yàn)閯?dòng)態(tài)功耗與電壓的平方成正比,瞬時(shí)導(dǎo)通功耗與電壓成正比,因此在滿足電路速度的前提之下,降低電源電壓是降低電路功耗的最有效的辦法。c.降低負(fù)載電容。為了減小負(fù)載電容,在工藝方面可以選擇小的器件,物理實(shí)現(xiàn)時(shí)減小連線的長(zhǎng)度。d.降低開(kāi)關(guān)頻率,在式(1)中,電路的功耗與工作頻率成正比,因此降低時(shí)鐘頻率可以直接降低動(dòng)態(tài)功耗。

②盡可能選用靜態(tài)功耗小的CMOS集成芯片,以降低系統(tǒng)的靜態(tài)漏電功耗。

③盡可能地減少純電阻的使用。純電阻是耗能元件,電能直接轉(zhuǎn)化為熱能消耗掉了,所以要盡可能地避免電阻的使用。

④減少有源開(kāi)關(guān)器件的使用。有源開(kāi)關(guān)器件(如晶體管)在狀態(tài)轉(zhuǎn)換期間有比較大的電流消耗,減少這類器件的使用有助于減小功耗。

3 設(shè)計(jì)技巧

3.1 硬件方面

在器件選擇上,要盡量實(shí)現(xiàn)全CMOS化的硬件設(shè)計(jì)。在設(shè)計(jì)超低功耗系統(tǒng)時(shí),要對(duì)電源電壓、時(shí)鐘頻率以及靜態(tài)功耗進(jìn)行控制,并遵循系統(tǒng)硬件設(shè)計(jì)的4項(xiàng)基本原則:電壓能低就不高,頻率能慢就不快,系統(tǒng)能靜(態(tài))就不動(dòng)(態(tài)),電源能斷就不通。

3.1.1 微處理器選擇

隨著低功耗系統(tǒng)需求的增加,很多單片機(jī)廠商都推出了自己的低功耗產(chǎn)品,如Philips公司的P8XLPC系列,TI公司的MSP430系列,Micro-chip公司的PIC單片機(jī)以及NXP公司的ARM Cortex-M0系列。如果處理器本身具有超低功耗特性,首先必須能在低電壓和低頻率工作,其次還要看單片機(jī)自身的特性,看是否是面向超低功耗應(yīng)用而設(shè)計(jì)的單片機(jī),需要對(duì)處理器的工作模式、工作電流、休眠電流、掉電電流作詳細(xì)的統(tǒng)計(jì)。

Microchip公司采用nanoWatt XLP(eXtreme Low Power)極低功耗技術(shù)的MCU的典型電流消耗為:掉電電流小于100 nA;看門狗電流消耗小于800 nA;實(shí)時(shí)時(shí)鐘和日歷電流消耗小于800 nA。該公司的PIC24F16KA系列的MCU,典型休眠電流可以低至20 nA,實(shí)時(shí)時(shí)鐘電流490 nA,看門狗定時(shí)器電流370 nA。該系列的MCU可使應(yīng)用連續(xù)運(yùn)行20年以上而無(wú)需更換電池。

NXP公司采用ARM Cortex-M0內(nèi)核的LPCllxx系列32位處理器的能耗僅為85μW/MHz,此系列處理器的功耗統(tǒng)計(jì)如表1和表2所列。

3.1.2 外圍集成電路

與TTL數(shù)字集成電路相比,CMOS數(shù)字集成電路在低功耗特性上具有無(wú)可比擬的優(yōu)越性能。在存儲(chǔ)容量需求較小的條件下,采用FRAM代替一般的Flash或E2PROM,將會(huì)節(jié)省很多電能,因?yàn)镕RAM的寫(xiě)入功耗是Flash和E2PROM的1/1 000~1/100 000。

3.1.3 低電壓供電

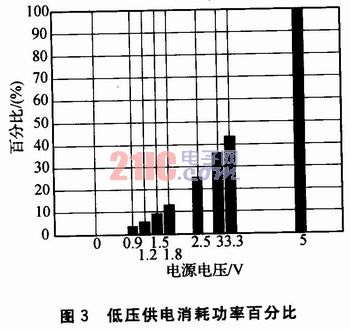

目前許多芯片的電源電壓范圍都比較寬,系統(tǒng)的功耗和系統(tǒng)的供電電壓存在著一定的函數(shù)關(guān)系。對(duì)于純電阻電路,功耗為P=V2/R;對(duì)于容性負(fù)載電路,動(dòng)態(tài)功耗為,見(jiàn)式(1)。從以上2式可以看出,系統(tǒng)的功耗與系統(tǒng)供電電壓的平方成正比。當(dāng)供電電壓由5 V降到3.3 V時(shí),功耗將減少50%以上;當(dāng)電壓降到1.8 V時(shí),功耗將減少80%以上,如圖3所示。

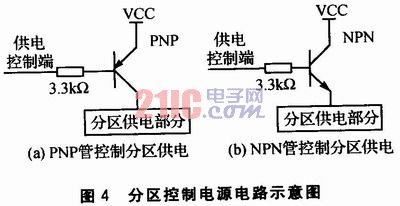

3.1.4 分區(qū)供電

分區(qū)供電就是要控制電源供電部分,需要對(duì)電源進(jìn)行分割,使系統(tǒng)功能模塊的電源供電相對(duì)獨(dú)立,同時(shí)實(shí)現(xiàn)其可控設(shè)計(jì),便于獨(dú)立供電和動(dòng)態(tài)管理;在閑置時(shí)利用開(kāi)關(guān)控制各個(gè)部分的關(guān)斷,以節(jié)省電能。在系統(tǒng)休眠或掉電工作時(shí)關(guān)掉外圍電路的電源,僅僅保留CPU和定時(shí)器電路的電源。分區(qū)控制電源電路示意圖如圖4所示。

圖4中的晶體管用作電源開(kāi)關(guān),控制電源VCC向分區(qū)供電部分供電,供電控制端接到處理器的輸出引腳上。對(duì)于圖4(a)中的PNP管,高電平切斷分區(qū)供電部分的電源,低電平使PNP晶體管導(dǎo)通,此時(shí)VCC向分區(qū)供電部分供電;對(duì)于圖4(b)中的NPN管,供電情形則相反。

3.1.5 低頻工作方式

低功耗微處理器中幾乎全部采用CMOS器件,而CMOS集成電路的結(jié)構(gòu)決定了它的靜態(tài)功耗幾乎為零,僅在邏輯狀態(tài)發(fā)生翻轉(zhuǎn)的過(guò)程中電路中有電流流過(guò)。所以它的動(dòng)態(tài)功耗和它的邏輯轉(zhuǎn)換頻率成正比,和電路的邏輯狀態(tài)轉(zhuǎn)換時(shí)間成正比。所以CMOS集成電路從降低功耗的角度上來(lái)說(shuō)應(yīng)當(dāng)快速轉(zhuǎn)換,低頻工作。

當(dāng)程序在Flash中運(yùn)行,VDD=3.3 V時(shí),LPCllxx處理器功耗如表2所列。

3.1.6 電源轉(zhuǎn)換芯片選擇

手持設(shè)備一般是由電池供電,為獲得較長(zhǎng)的電池使用時(shí)間,一般采用DC/DC開(kāi)關(guān)電源或LDO(Low Drop Outregulatot,低壓差線性穩(wěn)壓器)。在價(jià)格允許的前提下,最好選擇那些效率高、靜態(tài)電流小,并且有使能端的芯片。效率高是為了減少電池能量在轉(zhuǎn)化的過(guò)程中造成的損失。靜態(tài)電流小可以減小芯片在待機(jī)狀態(tài)的漏電流功耗。選擇具有使能端的芯片可以利用微處理器進(jìn)行關(guān)斷控制,有利于獨(dú)立供電支路功耗的管理。凌力爾特公司的DC/DC芯片LTC3417具有高達(dá)95%的效率和低于1μA的靜態(tài)電流,已經(jīng)在作者的有源手持機(jī)項(xiàng)目中得到了應(yīng)用,取得

了顯著的低功耗效果。

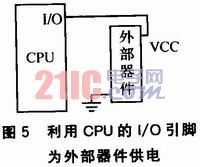

3.1.7 I/O引腳供電

可以直接利用嵌入式微處理器的I/0引腳為外部設(shè)備提供電源,如圖5所示,只要這些I/O接口的驅(qū)動(dòng)能力足以驅(qū)動(dòng)外部設(shè)備。

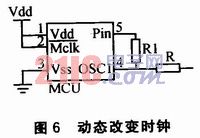

3.1.8 MCU時(shí)鐘

單片機(jī)的工作頻率和功耗的關(guān)系很大,頻率越高功耗越大。處理器動(dòng)態(tài)改變CPU時(shí)鐘的具體做法是:在CPU等事件發(fā)生時(shí),引腳輸出低電平,增大電阻將會(huì)降低內(nèi)部的時(shí)鐘的頻率;當(dāng)需要處理事務(wù)時(shí),輸出高電平減小電阻,提高時(shí)鐘頻率。實(shí)現(xiàn)這一技術(shù)的方法如圖6所示。當(dāng)CPU處于等待狀態(tài)下可以將I/O引腳輸出低電平,此時(shí)內(nèi)部時(shí)鐘頻率降低;當(dāng)CPU需要處理事務(wù)的時(shí)候,通過(guò)將I/O引腳設(shè)定為輸出高電平,電阻Rl的加入將提高時(shí)鐘頻率。

3.1.9 未用引腳

處理好處理器和CMOS芯片未用的輸入引腳。若未用的處理器引腳不加以處理,很容易造成電荷積累。根據(jù)電量與電容C和電壓U的關(guān)系Q=C·U可知,當(dāng)電荷的累積Q與電容C可比的情況下,就會(huì)產(chǎn)生影響引腳電平狀態(tài)的U,這個(gè)電平會(huì)隨著電荷的累積而導(dǎo)致數(shù)字邏輯狀態(tài)在“O”和“1”之間變化,當(dāng)輸入引腳電平處于O、1之間的過(guò)渡區(qū)時(shí),會(huì)使電路中反相器的P管和N管都處于導(dǎo)通狀態(tài),導(dǎo)致功耗大大增加。

CMOS電路未用的引腳,一般采取加上拉電阻(1~10 kΩ)的方法處理,為節(jié)能起見(jiàn),阻值要取大一些。

3.1.10 局部電路的節(jié)電技巧

①采用RC振蕩器比晶體振蕩器或鎖相環(huán)更省電。

②接口電平要盡量匹配,以減少電平匹配電路帶來(lái)的額外功耗。

③在保證驅(qū)動(dòng)能力的前提下,電路中應(yīng)盡可能采用阻值較大的上拉/下拉電阻,以減小在電阻上的能量消耗。

④如果允許,適當(dāng)降低外部驅(qū)動(dòng)引腳的電壓。

⑤選擇合適的驅(qū)動(dòng)接口參數(shù),以減小緩沖器的使用量。

⑥少用驅(qū)動(dòng)電阻或雙極晶體管,這些器件需維持恒定的電流,從而增加了電能消耗。

3.2 軟件方面

3.2.1 避免查詢方式和延時(shí)

A/D轉(zhuǎn)換器在采集少量的數(shù)據(jù)時(shí),MCU讀取A/D轉(zhuǎn)換數(shù)據(jù)的方式有2種:查詢方式和中斷方式。查詢方式和中斷方式的低功耗特性相差甚遠(yuǎn):使用中斷方式,MCU可以什么都不做,甚至可以進(jìn)入待機(jī)或者停止模式;而查詢方式下,MCU必須不停地讀取I/O端口寄存器,消耗很多額外的功耗。

如果系統(tǒng)的定時(shí)器資源充裕,在需要定時(shí)的場(chǎng)合,最好采用硬件定時(shí)器,當(dāng)定時(shí)器到了定時(shí)時(shí)間后,向MCU發(fā)出中斷請(qǐng)求信號(hào),這樣可以減少M(fèi)CU的工作時(shí)間,進(jìn)而可以節(jié)省功耗。

3.2.2 運(yùn)行管理

①動(dòng)態(tài)電源管理(Dynamic Power Management,DPM)。有選擇地把閑置的系統(tǒng)部分置于低功耗狀態(tài),從而有效地利用電能。充分利用處理器和外圍電路的低功耗工作模式,當(dāng)系統(tǒng)和外圍電路不工作的時(shí)候,軟件設(shè)計(jì)時(shí)應(yīng)該使處理器和外圍電路及時(shí)地進(jìn)入待機(jī)或者休眠模式。可選擇關(guān)斷CPU時(shí)鐘或系統(tǒng)時(shí)鐘,對(duì)時(shí)鐘的控制要做到忙時(shí)多用、閑時(shí)少用、不用關(guān)斷。

②間歇性使用電路的控制。對(duì)于間歇性使用的外圍電路,在軟件控制中通過(guò)片選使能端控制其工作時(shí)間。在某些功能沒(méi)有使用到時(shí),適時(shí)地將嵌入式處理內(nèi)部電路的全部或部分關(guān)斷,或者進(jìn)入睡眠或待機(jī)狀態(tài),同時(shí)關(guān)閉不用的外圍接口電路,如串口、ADC/DAC、I2C、SPI、PWM等電路。

③未用I/0引腳的軟件處理。對(duì)于未用的處理器I/O引腳,軟件中也要進(jìn)行初始化,若不進(jìn)行初始化,將有可能會(huì)增加單片機(jī)的漏電流,最好將其設(shè)置為輸入或者輸出,且接一個(gè)固定的電平。

3.2.3 用宏代替子程序

宏是在編譯器預(yù)處理階段進(jìn)行替代,而子程序調(diào)用中MCU需要進(jìn)行現(xiàn)場(chǎng)保護(hù)。進(jìn)入子程序之前要將當(dāng)前的MCU寄存器壓入RAM中分配的棧,在離開(kāi)的時(shí)候,要把棧中的內(nèi)容彈出來(lái)恢復(fù)MCU的寄存器,這樣至少會(huì)帶來(lái)2次對(duì)RAM的操作。盡管用宏增加了代碼的長(zhǎng)度,但是加快了代碼執(zhí)行的速度,對(duì)于目前很多MCU來(lái)說(shuō),代碼的Flash空間根本不是大問(wèn)題,這種做法將會(huì)在一定程度上降低系統(tǒng)功耗。

3.2.4 采用高效率算法

①用查表的方法代替實(shí)時(shí)的計(jì)算。特別是在沒(méi)有硬件浮點(diǎn)處理單元的MCU進(jìn)行浮點(diǎn)處理的時(shí)候,直接用MCU進(jìn)行浮點(diǎn)處理將會(huì)消耗大量的時(shí)間。如果將一些運(yùn)算的結(jié)果事先計(jì)算好,存儲(chǔ)在程序存儲(chǔ)器的代碼段中,在需要某個(gè)數(shù)據(jù)時(shí)用查表的辦法把數(shù)據(jù)取出來(lái),可以減少M(fèi)CU的運(yùn)算量,有效地降低MCU的功耗。這種處理方法在離散余弦變換和A/D數(shù)據(jù)采集中能夠帶來(lái)可觀的效率提升。

②用移位運(yùn)算代替乘除法運(yùn)算。用MCU計(jì)算乘除法也是非常耗時(shí)的事情,如果盡可能避免直接的乘除運(yùn)算,而采用左移和右移的辦法來(lái)實(shí)現(xiàn),將會(huì)減少運(yùn)算時(shí)間,進(jìn)而節(jié)省功耗。如要進(jìn)行y=x·15的運(yùn)算,可以轉(zhuǎn)化為x<<4-x。對(duì)于特殊的除法,要采取右移的辦法。如3000÷256可以直接轉(zhuǎn)化為3 000>>8。當(dāng)然,除法的移位計(jì)算只能針對(duì)除數(shù)比較特殊的時(shí)候。

③采用快速算法。在搜索算法中,使用二分搜索算法和分段查找算法的效率是不同的。理論上可以估算,在1 024個(gè)測(cè)量值的查找中,二分搜索最壞情況下10次可以查找到結(jié)果,順序搜索最壞可能需要1 024次。這個(gè)在測(cè)量數(shù)值更多的情況下更為突出,一個(gè)高效率的查找算法有

助于減小程序運(yùn)行功耗。數(shù)字信號(hào)處理中的運(yùn)算,采用FFT和快速卷積等,可以節(jié)省大量運(yùn)算時(shí)間,從而減少功耗。

④在精度允許的情況下,使用簡(jiǎn)單函數(shù)代替復(fù)雜函數(shù)作近似也是減少功耗的一種方法。