1 引 言

電子記帳控稅終端機(jī)屬于高度安全和可靠的產(chǎn)品,關(guān)系到信息安全和金融安全,長期使用國外的核心器件將給國家安全帶來嚴(yán)重隱患。擁有自主知識產(chǎn)權(quán)的嵌入式處理器、專用芯片及其嵌入式操作系統(tǒng)已成為振興我國電子行業(yè)的當(dāng)務(wù)之急。

目前國家正在大力發(fā)展金稅工程,本文作者參與了針對電子記帳控稅終端機(jī)設(shè)計的片上系統(tǒng)(System on Chip,SOC)芯片的研究。

2 總體方案

本SoC芯片是面向電子記帳終端設(shè)備而設(shè)計的符合國家電子記帳終端設(shè)備標(biāo)準(zhǔn)的高性能嵌入式的系統(tǒng)芯片,其中以32位的SPARC V8架構(gòu)的處理器為內(nèi)核,集成了符合ISO7816標(biāo)準(zhǔn)的智能卡控制器和符合ISO7811/2標(biāo)準(zhǔn)的磁卡控制器接口等外圍設(shè)備。他的應(yīng)用既降低了電子記帳終端設(shè)備的成本,又大大提高了系統(tǒng)的可靠性。

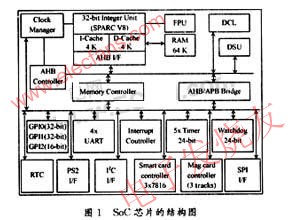

2.1 SoC的結(jié)構(gòu)

本SoC芯片內(nèi)部采用可裁減的總線式結(jié)構(gòu),選用ARM公司的AMBA總線作為SoC內(nèi)部總線,總線上各個模塊采用統(tǒng)一的接口方式和總線連接,從而實現(xiàn)了模塊開發(fā)的標(biāo)準(zhǔn)化,降低了開發(fā)的工作量。本SoC芯片的結(jié)構(gòu)如圖1所示。

本SoC采用"Harvard"結(jié)構(gòu),地址總線和數(shù)據(jù)總線分開,分別連接到獨立的"cache"控制器上。指令cache和數(shù)據(jù)cache均為直接映射cache,配置各為4 kB;各部分的功能簡述如下:

(1)32位整型數(shù)處理單元(Integer Unit,IU)支持SPARC V8指令集。IU的主要功能是執(zhí)行整數(shù)運算、計算要訪問的存儲器的地址,另外他也支持指令計數(shù)器和控制指令的執(zhí)行。IU具有以下特點:

①5級單一指令流水;

②單獨的指令cache和數(shù)據(jù)cache;

③標(biāo)準(zhǔn)的8個寄存器窗口;

④硬件乘法、除法器;

⑤帶40位累加器的16×16位MAC。

(2)浮點運算單元(Floating Point Unit,F(xiàn)PU)提供遵循SPARC V8標(biāo)準(zhǔn)的全部浮點指令,其浮點數(shù)據(jù)的格式和浮點指令遵循ANSI/IEEE 754-1985標(biāo)準(zhǔn),F(xiàn)PU連接在IU上。FPU有32個32 b的浮點寄存器。芯片使用標(biāo)準(zhǔn)的LD/ST指令在FPU和存儲器之間移動數(shù)據(jù)。存儲器地址由IU計算,浮點操作指令完成浮點算術(shù)運算。

內(nèi)部的AMBA總線包括2種總線:AHB和APB。APB總線用來訪問片內(nèi)外設(shè)的寄存器;AHB總線用作高速數(shù)據(jù)傳輸。AHB總線連接處理器cache控制器和其他的高速單元,IU是總線上惟一的主控單元。AHB總線從屬單元有:存儲器控制器、AHB/APB轉(zhuǎn)換橋等。AHB/APB轉(zhuǎn)換橋作為一個從屬設(shè)備連接在AHB總線上,是APB總線惟一的主控單元,處理器通過AHB/APB橋訪問大部分片內(nèi)外設(shè)。

(3)SOC的片上外設(shè),智能卡控制器(Smartcard controller):符合ISO7816標(biāo)準(zhǔn):

磁條卡控制(magnetic stripe card Controller):符合ISO7811/2標(biāo)準(zhǔn);

通用輸入輸出接口(GPIO):共80個GPIO端口;

通用異步串口(UART):一個16550UART和3個普通UART;

中斷控制器(Interrupt Controller):支持16個一級中斷源,32個二級中斷源;

定時器(Timer):5個24位的通用目的定時器;

看門狗(Watch Dog):24位看門狗定時器;

實時時鐘(RTC):計算秒、分、小時、天、月、年,具有潤月補(bǔ)償功能,計時可至2100年,通過后備電源使實時時鐘工作在低功率模式;

PS/2控制器(PS/2 I/F):符合PS/2標(biāo)準(zhǔn),支持第一套和第二套掃描碼集;

I2C控制器(I2C I/F):兼容Phillips公司的I2C標(biāo)準(zhǔn);

SPI控制器(SPI I/F):兼容SPI和Microwire/Plus兩個企業(yè)標(biāo)準(zhǔn)。

2.2 SoC芯片的設(shè)計要點

在SoC的體系架構(gòu)、邏輯設(shè)計和電路設(shè)計中采用正向設(shè)計方法:

建立深亞微米自頂向下設(shè)計流程,實現(xiàn)硬/軟件協(xié)同仿真、設(shè)計、驗證技術(shù),建立芯片正向設(shè)計平臺;

低功耗設(shè)計技術(shù),包括對RTC及SRAM的低功耗優(yōu)化設(shè)計;

采用深亞微米(0.18μm)必須解決的設(shè)計問題,包括。EMI,CrOSS talk,天線效應(yīng)和熱電子效應(yīng)等;

采用現(xiàn)代SoC設(shè)計技術(shù),實現(xiàn)片上外設(shè)包括IC卡、磁卡、I2C、SPI、PS/2等功能接口的高度集成設(shè)計和測試;

高可靠、實時多任務(wù)處理平臺技術(shù),支持嵌入式操作系統(tǒng)及其任務(wù)調(diào)度管理;

支持ANSIC的標(biāo)準(zhǔn)應(yīng)用,實現(xiàn)底層驅(qū)動軟件的模塊化、標(biāo)準(zhǔn)化設(shè)計。

同時,針對以上技術(shù)挑戰(zhàn)必須實現(xiàn)如下技術(shù)創(chuàng)新:

該項目為自主知識產(chǎn)權(quán)的內(nèi)嵌32位RISC處理器以及大量功能接口模塊的SoC設(shè)計,突破嵌入式SoC的高度集成、高可靠、低功耗、實時多任務(wù)處理等關(guān)鍵技術(shù);

建立自頂向下的深亞微米設(shè)計流程,實現(xiàn)硬、軟件協(xié)同設(shè)計、仿真、綜合、驗證技術(shù);采用大容量FPGA和嵌入式操作系的統(tǒng)功能驗證平臺;應(yīng)用樣機(jī)對SoC進(jìn)行全面驗證,確保了該項目的技術(shù)路線實施及產(chǎn)品的實際應(yīng)用;

支持多任務(wù)實時嵌入式操作系統(tǒng)。

3 功能驗證

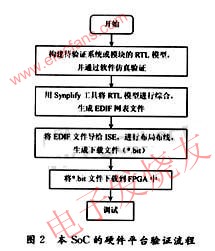

在集成電路的設(shè)計過程中,需要進(jìn)行大量的驗證工作,SoC功能驗證采用專門的開發(fā)軟件把設(shè)計模型轉(zhuǎn)換成相應(yīng)的配置文件,下載到硬件平臺的FPGA或CPLD芯片中,在實際的應(yīng)用系統(tǒng)中來驗證SoC功能的正確性。

在對本SoC進(jìn)行硬件平臺驗證過程中,采用的FPGA綜合工具是Synplicity公司的Synplify Pro 7.7,F(xiàn)PGA布線工具選用的是Xilinx公司的ISE 5.0,硬件平臺的核心FPGA芯片選用的是Xilinx公司的Virtex II系列的XC2V2000。驗證流程如圖2所示[1-3]。

3.1 驗證平臺的設(shè)計

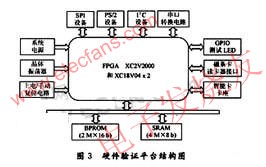

本SOC芯片內(nèi)部采用AMBA總線,內(nèi)嵌32 b整數(shù)處理單元,優(yōu)化的32/64 b浮點數(shù)處理單元,并且內(nèi)嵌了大量的外設(shè),主要包括:80位GPIO口、4路UART控制器、5個24 b定時器、看門狗、.PS/2控制器、I2C總線控制器、SPI總線控制器、1個三磁道磁卡控制器,3個智能卡控制器等。為了完整地測試本SoC的所有功能,硬件測試平臺如圖3所示,包含下列基本組成部分:

FPGA芯片;配置PROM;程序BPROM;SRAM;串口轉(zhuǎn)換芯片;I2C總線設(shè)備;SPI總線設(shè)備;磁卡讀卡器接口;智能卡及卡座;GPIO測試點;PS/2設(shè)備;系統(tǒng)時鐘發(fā)生設(shè)備;上電復(fù)位電路;電源。

3.2 FPGA平臺驗證結(jié)果

將由SoC的RTL模型產(chǎn)生的FPGA下載文件(*.bit文件)下載到FPGA中,在Unix環(huán)境下,用SPARC-GCC編譯器編譯測試程序(標(biāo)準(zhǔn)C程序),然后觀察程序運行結(jié)果,就可以驗證整個SoC系統(tǒng)或某一模塊功能的正 確性。

下面以獲取智能卡復(fù)位應(yīng)答(Answer To Reset,ATR)字節(jié)為例,闡述此過程。

事先知道待測智能卡的ATR字節(jié)為:3b,7a,18,0,0,21,8,11,12,13,14,15,16,17,18。

測試結(jié)果為:

Smartcard controller testing…

ATR over,and ATR characters:

3b,7a,18,0,0,21,8,11,12,13,14,15,16,17,18

以上結(jié)果說明,智能卡控制器可以接收到卡的復(fù)位應(yīng)答字節(jié),SoC的此功能正確。采用同樣的方法及過程可以驗證其他功能的正確性。

4結(jié) 語

該SoC芯片如今已經(jīng)成功應(yīng)用到了多種電子記帳終端設(shè)備中,為國內(nèi)外的電子記帳終端設(shè)備制造商們提供了一種高性價比的選擇,為"中國芯"家族又增添了一位新成員。所以,可以認(rèn)為該SoC芯片的設(shè)計還是非常成功的。

設(shè)計中存在的主要問題就是內(nèi)置的RAM空間還不夠大,對于高端的電子記帳終端設(shè)備,必須外擴(kuò)一定容量的RAM存儲器,希望在下一款同類芯片設(shè)計中加以改進(jìn)。