作者:肖小虎 高珊 陳軍寧 柯導(dǎo)明

0 引言

隨著功率集成電路的飛速發(fā)展,功率半導(dǎo)體器件的研究與開發(fā)顯得愈發(fā)重要。LDMOS是DMOS器件的一種橫向高壓器件。具有耐壓高、增益大、失真低等優(yōu)點(diǎn),并且更易與CMOS工藝兼容,因此在射頻集成電路中得到了廣泛的應(yīng)用。目前LDMOS設(shè)計(jì)的重點(diǎn)是如何合理緩和擊穿電壓與導(dǎo)通電阻之間的矛盾,并且保證其有較高的穩(wěn)定性。

場板技術(shù)是功率LDMOS器件中使用最為頻繁的一種終端技術(shù)。合理的場板設(shè)計(jì)可以使漂移區(qū)的平均電場增加,減小電場峰值,從而達(dá)到抑制熱載流子效應(yīng),提高擊穿電壓等目的。因此,建立LDMOS的電場分布模型,理論上對場板下的電場分布進(jìn)行數(shù)值分析有重要的現(xiàn)實(shí)指導(dǎo)意義。本文將通過建立二維解析模型研究LDMOS的場板的不同結(jié)構(gòu)對于其漂移區(qū)電場和電勢的影響,并在此基礎(chǔ)上通過優(yōu)化場板來提高LDMOS的性能。

1 二維解析模型

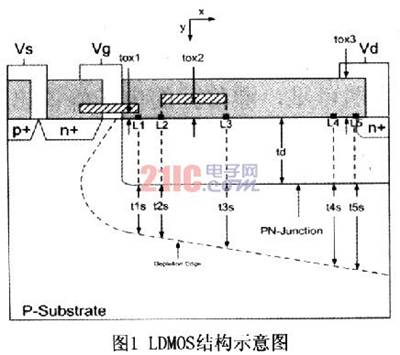

LDMOS的橫向切面圖如圖l所示。其中X和Y分別為距漂移區(qū)左上角的橫向距離和縱向距離,漂移區(qū)分成五部分,各區(qū)邊界點(diǎn)的橫坐標(biāo)分別設(shè)為L1、L2、L3、L4和L5。各區(qū)對應(yīng)的襯底耗盡層寬度分別為tis(i=1,2,3,4,5)。柵極下氧化層的厚度為tox1,場板下的氧化層厚度為tox2,漏端下氧化層厚度為tox3。n-drift漂移區(qū)的濃度為Nn,厚度為td。P型硅襯底濃度為Nsub,所加?xùn)艍簽閂g1,場板所加電壓為Vg2,漏壓Vd。源極和襯底接地。則漂移區(qū)的二維電勢分布φ(x,y)滿足二維泊松方程:

![]()

其中εo和εsi分別為真空介電常數(shù)和Si的介電常數(shù)。

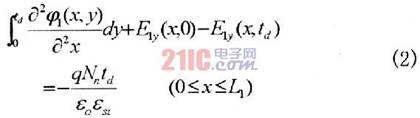

由于漂移區(qū)是均勻摻雜的,在1區(qū)(0≤x≤L1)對式(1)進(jìn)行y方向的積分可得:

由于Si02/Si界面上的電位移是連續(xù)的,忽略Si02中固定電荷,可得:

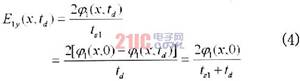

由于2、4、5區(qū)中縱向電場和橫向電場相比可忽略,可近似認(rèn)為

其他各區(qū)的對應(yīng)的耗盡層厚度可由![]() 得到,而由[2]可定義

得到,而由[2]可定義

根據(jù)漂移區(qū)表面電場和電勢的連續(xù)性可得出邊界條件

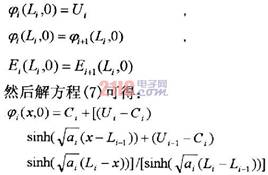

將上式在x方向微分,解得

式中Ui(i=1,2,3,4)的值可由Ei(Li,0)=Ei+1(Li,0)解得。

2 結(jié)果和分析

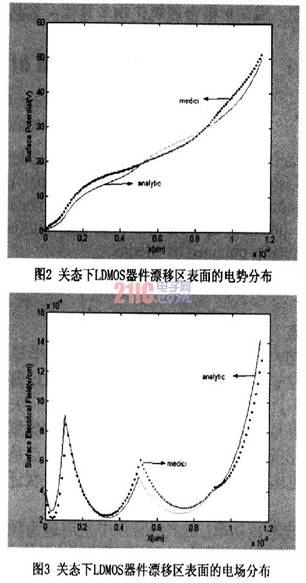

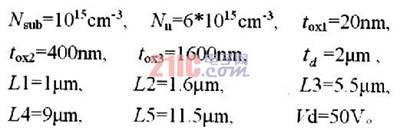

上圖是在器件關(guān)態(tài)條件下漂移區(qū)表面電勢和電場分布的理論值。采用的數(shù)據(jù)如下:

從圖中可以看出,LDMOS處于關(guān)態(tài)時(shí)根據(jù)理論模型計(jì)算得到的結(jié)果和Medici仿真結(jié)果的比較。由于本文的模型忽略了氧化層固定電荷,所以和Medici仿真結(jié)果有差異較小。由圖可見,漂移區(qū)的電場峰值出現(xiàn)在p阱/n-漂移區(qū)結(jié)處、場板的兩端與漏端附近。這些電場峰值處也就是最可能的擊穿點(diǎn)。

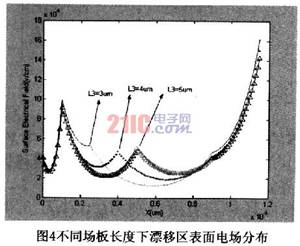

下面將詳細(xì)討論多晶柵場極板的長度和位置對漂移區(qū)表面電場和電勢的影響。圖4為不同場板長度下漂移區(qū)表面電場分布。由圖可見,隨著場板長度的增加,場板下的電場峰值先減小后增加,這是因?yàn)閳霭彘L度較短時(shí),場板末端與場氧鳥嘴區(qū)以及p阱/n-漂移區(qū)結(jié)距離較近,等勢線在此區(qū)域分布較密,三者相互作用可使此處表面電場增強(qiáng),器件容易在此處發(fā)生雪崩擊穿;隨著場板長度增加,場板末端和漏極距離縮短,進(jìn)而調(diào)制漏電極附近的電場峰值,使得電場在整個(gè)漂移區(qū)內(nèi)分布更加均勻,提高器件的耐壓能力。但是場板長度過長時(shí),反而會增強(qiáng)漏端電場,因此,對于LDMOS,場板長度有一個(gè)最優(yōu)值。

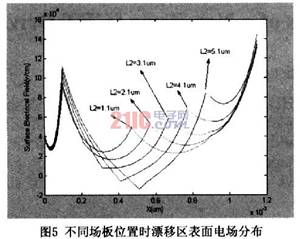

圖5為不同場板位置時(shí)漂移區(qū)表面電場分布,此時(shí)場板長度取2.5μm。由圖知,隨著場板向漏端靠近,場板下的電場峰值逐漸增加,這是場板所加電壓與漏壓共同作用所致。這一點(diǎn)對提高器件的耐壓能力很有幫助,也是優(yōu)化設(shè)計(jì)場極板位置的主要依據(jù)。當(dāng)場極板遠(yuǎn)離柵極時(shí),出現(xiàn)溝道末端電場上升,漏端電場下降的趨勢。考慮到漏端電場峰值更大,此處是器件的擊穿點(diǎn),因此設(shè)計(jì)時(shí)主要考慮降低漏端電場峰值。因此,針對文中的LDMOS器件結(jié)構(gòu),場板位置應(yīng)該設(shè)計(jì)在靠近漏極處。從圖4和圖5可見最大電場峰值位于漏端,因此一旦發(fā)生熱載流子效應(yīng),這里電離積分很大,是熱電子產(chǎn)生的主要區(qū)域。與柵氧化層處的熱載流子效應(yīng)不同,漏端熱載流子進(jìn)入場氧化層形成的界面電荷距離溝道很遠(yuǎn),因此不會改變器件的閾值電壓,但是這部分電荷會影響到漂移區(qū)電流密度的分布,進(jìn)而改變器件的驅(qū)動電流和跨導(dǎo),對LDMOS的可靠性產(chǎn)生影響。

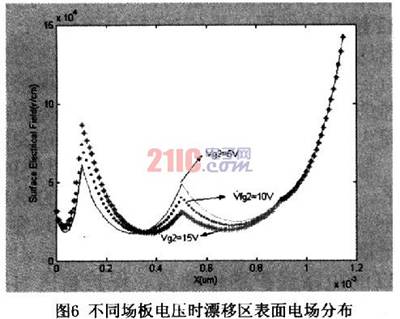

圖6為場板加不同電壓時(shí)的漂移區(qū)表面電場分布圖。此時(shí)場板長度取2.5μm,場板距離柵極0.5μm。從圖中可以看出,隨著場板所加電壓的增大,場板靠近柵極的一端電場峰值增大,而靠近漏極一端的電場峰值減小,即整個(gè)場板區(qū)的電勢降落隨場板電壓的增大而增大。而其他區(qū)域的電場隨場板電壓變化不大。因此對于LDMOS場板電壓的控制也是器件設(shè)計(jì)的一個(gè)重要因素。

3 結(jié)論

本文根據(jù)LDMOS器件漂移區(qū)電場分布和電勢分布的二維解析模型,通過分段求解泊松方程得出了器件漂移區(qū)表面電勢分布和電場分布的解析表達(dá)式,并根據(jù)所得的表達(dá)式分析了LDMOS一階場板的長度和位置以及場板所加電壓對于其漂移區(qū)表面電勢和電場分布的影響。計(jì)算結(jié)果表明,LDMOS的場板各參數(shù)對于器件的性能有很大影響。因此,本文的分析模型對于實(shí)際LDMOS器件的設(shè)計(jì)有著重要的指導(dǎo)意義。