摘 要: 在簡要介紹同步數字復接" title="復接">復接基本原理的基礎上,采用VHDL語言對同步數字復接各組成模塊進行了設計,并在ISE集成環(huán)境下進行了設計描述、綜合、布局布線及時序仿真,取得了正確的設計結果,同時利用中小容量的FPGA實現了同步數字復接功能。

關鍵詞: 同步數字復接/分接 FPGA 位同步" title="位同步">位同步 幀同步" title="幀同步">幀同步檢測

基群速率數字信號的合成設備和分接設備是電信網絡中使用較多的關鍵設備,在數字程控交換機的用戶模塊、小靈通基站控制器和集團電話中都需要使用這種同步數字復接設備。近年來,隨著需要自建內部通信系統(tǒng)的公司和企業(yè)不斷增多,同步數字復接設備的使用需求也在增加。FPGA(現場可編程門陣列)器件的高性能簡化了數字通信系統(tǒng)的設計與實現。本文基于FPGA的技術特點,結合數字復接技術的基本原理,實現了基群速率(2048kbps)數字信號的數字分接與復接。

1 同步數字復接的基本原理

在數字通信網中,為了擴大傳輸容量和傳輸效率,常常需要把若干個低速數字信號合并成為一個高速數字信號,然后通過高速信道傳輸;而在接收端又按照需要分解成低速數字信號。數字復接技術就是實現這種數字信號合并(復接)和分解(分接)的專門技術[1]。

1.1 系統(tǒng)劃分

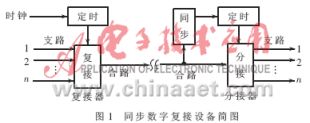

同步數字復接終端包括同步數字復接器" title="復接器">復接器(Synchronous Digital Multiplexer)和同步數字分接器" title="分接器">分接器(Synchronous Digital Demultiplexer)兩部分,如圖1所示。數字復接器把兩個或兩個以上的支路數字信號按時分復用方式合并成單一的合路數字信號;數字分接器把單一的合路數字信號分解為原來的各支路數字信號。通常總是把數字復接器和數字分接器裝在一起做成一個設備,稱為復接分接器(Muldex),一般簡稱數字復接設備[2]。

同步數字復接器由定時和復接單元組成;而同步數字分接器則由同步、定時和分接單元組成。定時單元給設備提供各種定時信號,復接器的主時鐘可由內部產生,也可由外部提供,而分接器主時鐘則從接收信號中提取,并通過同步電路的調整控制,使得分接器基準時序信號與復接器基準時序信號保持正確的相位關系,即收發(fā)同步。同步的建立由同步單元實現[1]。

1.2 位同步[3]

在數字通信中,位同步是最基本的同步。位同步的基本含義就是收端和發(fā)端時鐘信號必須同頻同相,這樣接收端才能正確接收和判決發(fā)送端送來的每一個碼元。為了達到收發(fā)端時鐘同頻同相,接收端需要從收到的碼流中提取發(fā)送端的時鐘信號來控制接收端時鐘,從而做到位同步。實現位同步的方法分為插入導頻法和直接法兩類。而直接法按照提取同步信號的方式,大致又可分為濾波法和鎖相法。鎖相法的原理是:在接收端用鑒相器比較接收碼元和本地產生的位同步信號的相位,如果兩者不一致,則用鑒相器輸出誤差信號去控制本地同步信號的相位,直至本地的位同步信號的相位與接收信號的相位一致為止。

1.3 幀同步

在復接分接器中,如果只是循環(huán)交織地復接各支路數字信號,那么一旦合并成為一個合路數字信號后就難以正確地實施分接。為了保證接收端分路系統(tǒng)能和發(fā)送端一致,在保持位同步的基礎上還必須要有一個幀同步系統(tǒng),以實現發(fā)送端與接收端的幀同步[2]。

實現幀同步的基本方法是在發(fā)送端預先規(guī)定的時隙(即幀同步碼時隙)插入一組特殊碼型的幀同步碼組;在接收端由幀同步檢測電路檢測該碼組以保證收發(fā)幀同步[2]。

幀同步檢測狀態(tài)有失步態(tài)、同步校核態(tài)、同步態(tài)和同步保護態(tài)四種狀態(tài)。

2 基于FPGA的同步數字復接的設計與實現

FPGA/CPLD既繼承了ASIC的大規(guī)模、高集成度、高可靠性的優(yōu)點,又克服了普通ASIC設計的設計周期長、投資大、靈活性差的缺點,逐步成為復雜數字電路設計的理想首選[4]。

ISE是XILINX公司提供的一個開發(fā)FPGA/CPLD的集成環(huán)境,其集成的工具可以完成從設計輸入、功能仿真、綜合優(yōu)化、綜合后仿真、布局布線、時序仿真到配置芯片等整個FPGA/CPLD開發(fā)過程。

本設計采用ISE集成環(huán)境進行開發(fā),使用SPARTAN-3系列FPGA器件實現設計。

2.1 按碼字復接系統(tǒng)的設計

數字信號復接主要有兩種方式[1]:一種是“逐位復接”,另一種是“按碼字復接”。其中按碼字復接方式保留了碼字結構,有利于多路合成處理和交換。本設計要實現32路信號的復接,信息位采取各支路彼此循環(huán)且每次插入一個8位信息位到合路數字信號中的碼字復接形式,幀同步碼采用CCITT推薦的10011011。

2.1.1 復接器和分接器的設計

復接器應完成兩個功能。一是循環(huán)接收32個64kbps的支路信號,每支路每次送入8位信息位(其中第一支路送入固定的幀同步碼10011011),形成合路數據;二是將合路數據以2048kbps的速率發(fā)送出去,形成合路信號——基群速率信號。

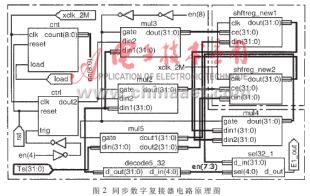

同步數字復接器電路原理圖如圖2所示,復接器由移位寄存器和定時模塊兩部分構成。移位寄存器分兩組,每組由32個8位移位寄存器組成。在一幀時間(125μs)內,當其中一組移位寄存器在64kHz時鐘控制下同時移入32個支路的數據時,另一組移位寄存器在2048kHz時鐘(xclk_2M)的控制下將上次存入的32個支路的數據依次送出。在下一幀時間內,則由第一組移位寄存器輸出2048kbps的合路信號,第二組移位寄存器讀入32個64kbps的支路數據。依此規(guī)律,在定時模塊的控制下,由兩組移位寄存器交替變換工作任務,實現了支路輸入和合路輸出的連續(xù)性。定時模塊由計數器(cnt)、多路選擇器(mul2~mul5)等組成,為兩組移位寄存器提供工作允許信號、合路信號輸出的切換選擇信號。

為了提高時鐘的可靠性、降低時鐘的延時抖動、提高時鐘的驅動能力,從而更好地完成同步復接,利用FPGA自身提供的全局時鐘資源驅動本設計的主時鐘,將外部時鐘從芯片的全局時鐘管腳輸入,經過BUFGP(IBUFG+BUFG)后通過全局時鐘網絡送至同步復接部分。

分接器的功能與復接器相反。分接器在其定時單元的控制下,對兩組移位寄存器進行2048kbps的數據寫入和64kbps的數據讀出,實現基群速率合路數字信號的32路分接。

2.1.2 位同步提取電路的設計

實現合路數字信號的分接,需要從數據流中提取時鐘同步信息。目前,在數字通信系統(tǒng)中,常常采用數字鎖相法提取位同步信號[3]。

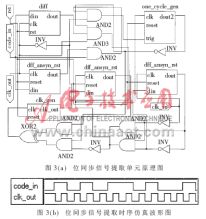

位同步提取電路如圖3(a)所示,主要由微分與鑒相模塊、添門/扣門控制模塊、高頻時鐘模塊以及分頻器(clk_gen)等部分組成。微分電路(diff)的功能是把非歸零碼轉換為歸零碼,以利于定時信息的提取。鑒相器的功能是比較接收碼元(code_in)與分頻器輸出的本地時鐘信號(clk_out)的相位,若本地時鐘超前于接收碼元的相位,鑒相器向扣門電路輸出一個超前脈沖,在16分頻器輸入端扣除一個高頻窄脈沖,使分頻器輸出的時鐘信號的相位滯后1/16周期;若本地時鐘滯后于接收碼元的相位,鑒相器向添門電路輸出一個滯后脈沖,增加一個高頻窄脈沖,使分頻器的輸出脈沖的相位提前1/16周期。高頻時鐘模塊將本地高頻時鐘輸入信號clk_in轉換為兩路相位差為90°的窄脈沖序列,分別為添門和扣門提供高頻窄脈沖序列。添門為常閉門,在沒有滯后脈沖控制時,此門始終關閉;扣門為常開門,若無超前脈沖控制時,窄脈沖信號通過此常開門。分頻器將輸入的高頻時鐘信號分頻后輸出位同步信號clk_out。

對位同步提取電路進行時序仿真,得到的時序仿真波形圖如圖3(b)所示。圖中,code_in為輸入碼流,clk_out為位同步信號輸出。由圖可知,該電路可以從輸入碼流中準確提取位同步信號,并且在碼流相位有變化的時,位同步信號可以快速地做出相位調整,保持同步。

2.1.3 幀同步單元的設計

為了正確地實施分接,在分接前必須先通過幀同步單元對合路信號進行幀同步檢測。

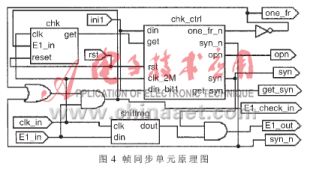

幀同步單元是復接設備中較復雜也很重要的部分。如圖4所示,它主要由同步碼檢測模塊(chk)和同步檢測控制模塊(chk_ctrl)兩部分組成。其中,同步碼檢測模塊對輸入的數據流進行搜索,一旦檢測到幀同步碼(10011011),立即輸出一個捕獲脈沖信號(get);同步檢測控制模塊由幀同步系統(tǒng)狀態(tài)計數器和一幀計數器等構成,完成幀同步單元的狀態(tài)轉換控制、每幀檢測同步頭的控制等功能。

幀同步的關鍵部分是前方保護和后方保護的設計。為了減少從失步到重新獲得同步的時間和減小信道誤碼對同步工作狀態(tài)的影響,從而得到較好的通信質量,本設計采用了2幀后方保護和3幀前方保護的方案。

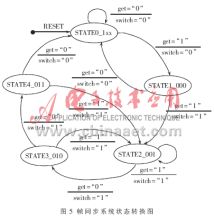

幀同步系統(tǒng)狀態(tài)轉換圖如圖5所示。系統(tǒng)上電復位后,在起始時刻處于失步狀態(tài)(STATE0_1xx——其中x表示無關值),系統(tǒng)從外部輸入的合路碼流中搜捕幀同步碼“10011011”,若合路碼流中沒有幀同步碼,狀態(tài)計數器仍保持為1xx;若從合路碼流中檢測出同步碼(get=“1”),則狀態(tài)計數器清零為000,系統(tǒng)進入同步校核態(tài)(STATE1_000),開始將合路碼流寫入移位寄存器,分接器輸出開關仍然為關閉狀態(tài)(switch=“0”)。在同步校核狀態(tài)下,若下一幀確認幀同步碼不正確,判斷為虛假同步,則狀態(tài)計數器減1變?yōu)?11,系統(tǒng)回到失步態(tài);相反,若下一幀確認幀同步碼正確,則系統(tǒng)進入同步態(tài)(STATE2_001),分接器輸出開關打開(switch=“1”),開始正常分接合路碼流。系統(tǒng)進入同步態(tài)后,若合路碼流中出現幀同步碼丟失,則狀態(tài)計數器加1,系統(tǒng)進入同步保護態(tài)1(STATE3_010);若下一幀仍然檢測幀同步碼失敗,則狀態(tài)計數器再加1,系統(tǒng)進入同步保護態(tài)2(STATE4_011);若連續(xù)第三幀未收到幀同步碼,則狀態(tài)計數器再加1轉為100,系統(tǒng)進入失步狀態(tài),停止分接合路碼流(switch=“0”),同時重新開始搜捕幀同步碼“10011011”。系統(tǒng)在同步保護態(tài)(狀態(tài)計數器值為01x)下,若檢測幀同步碼正確,則狀態(tài)計數器置數為001,系統(tǒng)回到同步態(tài)。

2.2 系統(tǒng)仿真與驗證

在ISE集成環(huán)境下,調用ModelSim仿真軟件對系統(tǒng)各模塊進行功能仿真、綜合后仿真以及布局布線后的時序仿真。仿真結果表明,復接器、分接器、同步單元等所有模塊的設計均滿足設計要求。

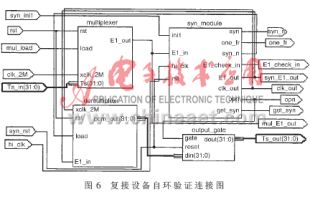

為了進一步確保系統(tǒng)設計的可實用性,將系統(tǒng)各組成模塊按照自環(huán)工作狀態(tài)連接起來,對系統(tǒng)各模塊進行了聯合仿真。復接設備自環(huán)驗證的原理圖如圖6所示。

將32路64kbps的支路信號Ts_in(31:0)送到復接器(multiplexer)的支路信號輸入端Ts(31:0),復接器的合路信號輸出端E1_out與同步單元syn_module(包括位同步和幀同步)的合路信號輸入端E1_in相連(自環(huán)),合路信號經過位同步信號提取以及幀同步檢測后,由同步單元將非失步狀態(tài)下的合路序列從信號輸出端E1_out送出,同步單元還提供位同步信號clk_out,送分接器demultiplex的輸入端xclk-2M,同步單元輸出的合路序列送入分接器的合路信號輸入端E1_in,經過分接器實施分接后,最后從支路輸出控制單元output_gate的輸出端可以得到各個支路的輸出信號Ts_out(31:0)。

圖7為復接設備自環(huán)驗證的仿真時序圖。其中,Ts_in為32個支路送來的64kbps的激勵信號;mul_E1_out為經復接器實施復接后的合路信號;E1_check_in為進入幀同步碼檢測模塊的合路序列;get_syn為幀同步碼檢測的結果;one_fr為同步校核和同步保護所需的幀同步碼檢測控制信號;syn_n為系統(tǒng)失步信號;syn_E1_out為非失步狀態(tài)下的合路序列;opn為支路信號輸出允許信號;Ts_out為實施分接后各支路的64kbps輸出信號;Ts_in(1)為復接器第一支路輸入信號;Ts_out(1)為分接器第一支路輸出信號。

將輸入激勵信號Ts_in與系統(tǒng)支路輸出信號Ts_out相比較,結果表明,在從同步到下一次失步的時間內,Ts_out與Ts_in信號波形基本一致——Ts_out中會出現一些1~2ns的過渡值,這些過渡值是由于Ts_out總線中32個支路信號到達寄存器輸出端的時間不一致而造成的,這是由FPGA器件時延不確定性決定的。由Ts_in(1)和Ts_out(1)的波形比較可知,對于每個單一的支路信號,并不存在這種過渡值,分接后的支路信號與復接器支路輸入信號一致。因此,Ts_out總線中出現的這種過渡值不會影響系統(tǒng)的性能。

時序仿真結果表明,復接、同步以及分接功能均正常,滿足設計要求。在5萬門的SPARTAN-3系列FPGA器件xc3s50上實現設計,硬件資源的使用情況如下:319個Slice,263個Slice Flip Flop,562個4 input LUT,70個bonded IOB,2個GCLK。該設計已作為一個模塊應用到其它系統(tǒng)中,具有一定的實用價值。同時,由于該設計采用VHDL語言描述,具有可移植性,利用中小容量的FPGA就能實現該系統(tǒng)功能。

參考文獻

1 張應中,張德民,溫 榮.數字通信工程.北京:人民郵電出版社[M],1996.8

2 曹志剛,錢亞生.現代通信原理[M].北京:清華大學出版社,1992.8

3 段吉海,黃智偉.基于CPLD/FPGA的數字通信系統(tǒng)建模與設計[M].北京:電子工業(yè)出版社,2004.8

4 王 誠,薛小剛,鐘信潮.FPGA/CPLD設計工具——Xilinx ISE 5.x使用詳解[M]. 北京:人民郵電出版社,2003.6