本文主要介紹一款基于復(fù)雜可編程邏輯器件的壓電生物傳感器檢測(cè)電路。該檢測(cè)電路核心為高性能CPLD,主要實(shí)現(xiàn)對(duì)壓電生物傳感器10MHz高頻信號(hào)的測(cè)量與采集以及所采集的頻率數(shù)據(jù)動(dòng)態(tài)、實(shí)時(shí)顯示以及頻率數(shù)據(jù)串行通信等功能。此外詳細(xì)闡明了系統(tǒng)整體結(jié)構(gòu)設(shè)計(jì)以及系統(tǒng)硬件部分的實(shí)現(xiàn),并給出了CPLD內(nèi)核仿真結(jié)果和數(shù)據(jù)采集軟件實(shí)測(cè)頻率曲線。該系統(tǒng)還可以通過RS-232串行接口與計(jì)算機(jī)連接進(jìn)行數(shù)據(jù)傳輸和數(shù)據(jù)存儲(chǔ)及分析。與此同時(shí),本電路優(yōu)點(diǎn)還有很多,例如體積小、集成度高,具有可靠性高、實(shí)時(shí)性高等。

國內(nèi)外基于壓電石英晶體微天平技術(shù)的檢測(cè)儀器大多數(shù)使用自行設(shè)計(jì)的振蕩電路盒,使用高分辨的頻率計(jì)數(shù)器測(cè)量頻率輸出,然后進(jìn)行定時(shí)人工記數(shù),儀器復(fù)雜,自動(dòng)化程度低.微型壓電生物傳感器檢測(cè)電路采用當(dāng)前最有發(fā)展前景的復(fù)雜可編程邏輯器件(CPLD)為核心器件設(shè)計(jì)而成.目前,CPLD集成度可達(dá)25萬等效門,工作速度可達(dá)180MHz.它借助自動(dòng)化程度高的內(nèi)核程序開發(fā)工具,可以大大縮短系統(tǒng)的計(jì)周期,而且數(shù)據(jù)采集可以由一塊CPLD芯片完成,整個(gè)系統(tǒng)的硬件規(guī)模明顯減小.在系統(tǒng)的研制階段,由于CPLD器件引腳比較靈活,又有可擦除可編程的能力,因此對(duì)原設(shè)計(jì)進(jìn)行修改時(shí),只需要修改原設(shè)計(jì)文件再對(duì)CPLD芯片重新編程即可,而不需要修改電路布局,更不需要重新加工印刷線路板,這就大大提高了系統(tǒng)的靈活性.結(jié)合壓電生物傳感器特性,研制一種微型化的壓電傳感器檢測(cè)電路有十分重要的意義.

1 壓電生物傳感器原理

壓電石英晶體頻移ΔF與在晶體表面均勻吸附的極薄層剛性物質(zhì)量Δm之間存在正比關(guān)系,由Sauerbrey方程描述,并且對(duì)于AT切割的石英晶體,可得到Sauerbrey方程式:

式中,ΔF、Fq(晶體基頻)、Δm、A單位分別為Hz、Hz、g.cm-2、cm2.石英晶片在氣相中振蕩時(shí),Δf與Δm呈簡單的線性關(guān)系,因此石英晶片可用來做非常敏感的質(zhì)量檢測(cè)器,其檢測(cè)限可以達(dá)到ng級(jí)(10-9g.cm-2),甚至pg(10-12g.cm2)級(jí)水平.

根據(jù)壓電石英晶體傳感器的原理設(shè)計(jì)了一種微型化的壓電傳感器檢測(cè)電路,其檢測(cè)原理為在傳感器上預(yù)先固定與待測(cè)物能發(fā)生親和反應(yīng)的“探針”,檢測(cè)待測(cè)物時(shí),隨著親和反應(yīng)的進(jìn)行,檢測(cè)電路實(shí)時(shí)跟蹤反應(yīng)過程,記錄傳感器上質(zhì)量變化引起頻率變化,再通過上述定量關(guān)系式計(jì)算待測(cè)物的量,其靈敏度可以達(dá)到納克級(jí)水平,結(jié)合納米金技術(shù)可將傳感器的靈敏度提高3~5倍.

2 電路硬件設(shè)計(jì)

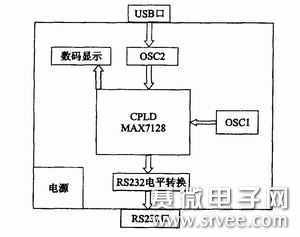

微型壓電傳感器檢測(cè)電路是經(jīng)過前幾代儀器的開發(fā)經(jīng)驗(yàn)總結(jié)和改進(jìn)基礎(chǔ)上完成的。它摒棄以往TTL集成電路或MCS51單片機(jī)為核心電路波動(dòng)大,穩(wěn)定性差,電路板繪制復(fù)雜,不利于升級(jí)換代的缺點(diǎn),選擇使用ALTERA公司生產(chǎn)的復(fù)雜可編程邏輯器件(CPLD)MAX7128為核心,基于RS232通信方式的串行接口數(shù)據(jù)采集分析平臺(tái).該系統(tǒng)分為7個(gè)模塊:電源供電模塊,RS-232電平轉(zhuǎn)換模塊,振蕩電路模塊,時(shí)鐘模塊,數(shù)碼顯示模塊,MAX7128內(nèi)核模塊.其電路線路板布局如圖1所示.

圖1硬件結(jié)構(gòu)圖

圖1中,USB口為壓電生物傳感器與檢測(cè)電路相連接的接口;RS-232口為與計(jì)算機(jī)相連接的接口,將數(shù)字化的傳感器信號(hào)(頻率值)上傳到計(jì)算機(jī),由計(jì)算機(jī)(PC機(jī))實(shí)現(xiàn)傳感器信號(hào)的實(shí)時(shí)采集和顯示,采集數(shù)據(jù)程序由VC++6.0編寫;OSC1為提供系統(tǒng)工作時(shí)鐘振蕩電路,由TTL芯片和12MHz標(biāo)準(zhǔn)晶振組成,產(chǎn)生1s脈沖信號(hào),作為CPLD工作時(shí)鐘輸入、RS-232通信時(shí)序脈沖以及數(shù)碼管動(dòng)態(tài)顯示時(shí)序脈沖,準(zhǔn)確度高、且精確;OSC2為傳感器振蕩電路,經(jīng)過幾代反復(fù)改良,在氣相、液相均能夠正常振蕩且波形正常,將傳感器表面生物反應(yīng)信號(hào)轉(zhuǎn)化成脈沖信號(hào),輸入CPLD進(jìn)行信號(hào)數(shù)據(jù)采集;數(shù)碼顯示采用共陰極8×8段數(shù)碼管,動(dòng)態(tài)掃描顯示當(dāng)前傳感器信號(hào)值和簡單數(shù)據(jù)分析判斷結(jié)果;電源給系統(tǒng)提供直流5V工作電壓,含有直流6~15V變成5V穩(wěn)壓電路;RS-232電平轉(zhuǎn)換電路將從CPLD輸出的CMOS電平轉(zhuǎn)化為計(jì)算機(jī)所接受的TTL電平,而且可增加數(shù)據(jù)傳輸距離.

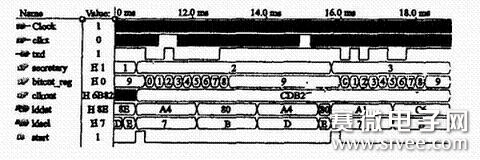

作為系統(tǒng)內(nèi)核的CPLD,采用VerilogHDL硬件設(shè)計(jì)語言、MAX+plusII10.1編譯系統(tǒng)編寫基于Altera公司CPLD(MAX7128)器件的內(nèi)核程序,設(shè)計(jì)實(shí)現(xiàn)了秒時(shí)鐘定時(shí)、10MHz頻率測(cè)量、RS-232通信時(shí)序發(fā)生器、RS-232協(xié)議數(shù)據(jù)通信、頻率數(shù)據(jù)判斷簡單分析以及數(shù)碼管動(dòng)態(tài)掃描顯示控制等綜合功能,其原理如圖2所示.

圖2 CPLD內(nèi)核原理圖

3 系統(tǒng)仿真及實(shí)測(cè)結(jié)果

系統(tǒng)仿真結(jié)果:為了便于觀察,將秒時(shí)鐘計(jì)數(shù)判斷設(shè)置為66C0,得到內(nèi)核模塊的仿真圖,如圖3所示.仿真圖給出了頻率采集細(xì)節(jié),數(shù)碼管顯示控制以及串行通信控制.

圖3 CPLD內(nèi)核仿真圖

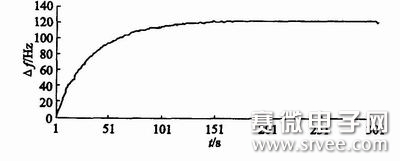

仿真結(jié)果吻合了設(shè)計(jì)思路,把內(nèi)核程序下載到CPLD(MAX7128)器件中,實(shí)際測(cè)試過程中,數(shù)碼管可以正確顯示當(dāng)前傳感器的響應(yīng)信號(hào),使用自己開發(fā)的采集程序通過計(jì)算機(jī)串行通信采集數(shù)據(jù)數(shù)據(jù)曲線如圖4所示.所采集的數(shù)據(jù)與仿真情況一致,更進(jìn)一步驗(yàn)證了設(shè)計(jì)思路的成功.

圖4 采集程序?qū)崪y(cè)頻率數(shù)據(jù)曲線

4結(jié)語

通過擴(kuò)展,壓電生物傳感器檢測(cè)電路能夠升級(jí)為單通道微型壓電生物分析一起。基于核酸雜交的特異性,其不僅可以用于生物樣品分析,在醫(yī)學(xué)臨床研究領(lǐng)域用于疾病診斷或者基于抗原/抗體之間的特異性結(jié)合反應(yīng),還具有靈敏度高、特異性強(qiáng)等優(yōu)點(diǎn)。如果采用CPLD升級(jí)為大容量FPGA后,本檢測(cè)電路能夠十分簡便的升級(jí)為多通道生物分析系統(tǒng),可以在生物分析檢測(cè)各個(gè)領(lǐng)域應(yīng)用。