電子攝像系統(tǒng)已廣泛應(yīng)用于軍用及民用測繪系統(tǒng)中,,但是效果受到其載體不同時刻姿態(tài)變化或震動的影響,。當(dāng)工作環(huán)境比較惡劣,尤其是在航空或野外操作時,,支撐攝像機(jī)平臺的震動會引起圖像畫面的抖動,,令觀察者視覺疲勞,從面產(chǎn)生漏警和虛警,。所以在運行中,,如何穩(wěn)像成為十分重要的問題,特別是在長焦距,、高分辨力的監(jiān)視跟蹤系統(tǒng)中更加突出,。具璞蒿、實性性強(qiáng),、體積小巧等特點,,得到更廣泛的應(yīng)用,。

穩(wěn)像系統(tǒng)的反應(yīng)速度是電子穩(wěn)像要解決的關(guān)鍵技術(shù)之一。傳統(tǒng)的基于“攝像機(jī)-圖像采集卡-計算機(jī)”模式的穩(wěn)像系統(tǒng),、圖像檢測和匹配算法全部由計算機(jī)以軟件方式實現(xiàn),。盡管當(dāng)今計算機(jī)的性能很高,能夠部分滿足單傳感器電子穩(wěn)系統(tǒng)的實時處理要求,,但在以下幾個方面有著難以解決的問題:首先,,其固有的串行工作方式使得單計算機(jī)難以適應(yīng)其于多傳感器視頻處理系統(tǒng)的實時穩(wěn)像,阻礙了在實際中的應(yīng)用adw欠,,傳統(tǒng)的圖像采集卡中能將采集圖像數(shù)據(jù)實時傳輸給計算機(jī),,而不能傳輸給標(biāo)準(zhǔn)接口的視頻監(jiān)視設(shè)備lk之很多應(yīng)用場合對聽要求很高。因此,,研制專用的電子穩(wěn)像平臺,,既能實時地高速獲取視頻數(shù)據(jù),又能將數(shù)據(jù)實時地傳后續(xù)的圖像處理系統(tǒng),,既有實際意義又有工程價值,。

1 系統(tǒng)涉及的關(guān)鍵技術(shù)

攝像頭輸入的PAL制式電視信號首先通過視頻處理接口完成對其解碼、同步和數(shù)字化的工作,,數(shù)字化后的圖像信息進(jìn)入到由FPGA實現(xiàn)的幀存控制器中,,完成數(shù)據(jù)的交換(數(shù)據(jù)的緩沖),同時完成系統(tǒng)要求的去隔行和放大的操作,,最后處理好的數(shù)據(jù)通過VGA控制器,,完成時序變化,經(jīng)視頻,、A變?yōu)槟M信號送到VGA監(jiān)視器上實時顯示,。

1.1 視頻處理接口

由于在進(jìn)行視頻處理時,多為從攝像頭輸入模擬信號,,如NTSC或PAL制式電視信號,,除圖像信號外,還包括行同步信號,、行消隱信號,、場同步信號、場消隱信號以及槽脈沖信號等,。因而對視頻信號進(jìn)行A/D轉(zhuǎn)換的電路也非常復(fù)雜,。PHILIPS公司將這些轉(zhuǎn)換電路集成到了一塊芯片中,從而生產(chǎn)出功能強(qiáng)大的視頻輸入處理芯片SAA7111,,為視頻信號的數(shù)字化應(yīng)用提供了極大的方便,。

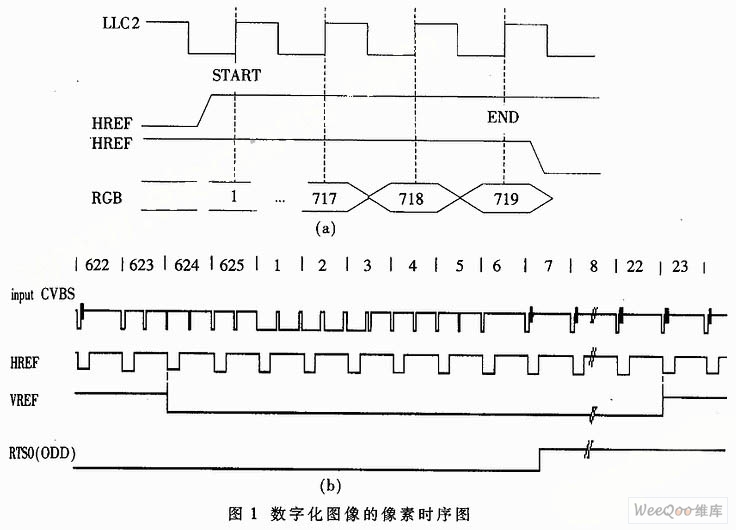

系統(tǒng)設(shè)計采用SAA7111對復(fù)合信號進(jìn)行采樣、同步產(chǎn)生,、亮色分離并輸出標(biāo)準(zhǔn)的數(shù)字化信號,。SAA7111輸出的數(shù)字化圖像信息符合CCIR.601建議,,PAL制式的模擬信號數(shù)字化后的圖像分辨率為720×572,像素時鐘13.5MHZ,。在本穩(wěn)像系統(tǒng)中要求圖像輸出符合VGA(640×480,,60Hz)標(biāo)準(zhǔn),因此在采集數(shù)據(jù)時要對數(shù)據(jù)進(jìn)行選擇,,避開行,、場消隱信號和部分有效像素信息,在較大的圖像中截取所需要的大小,。SAA7111向幀存控制電路輸出像素時鐘(LCC2),、水平參數(shù)(HREF)、垂直參考(VREF),、奇偶場標(biāo)志信號(ODD)和16位像素信息(RGB565).其中LCC2用來同步整個采集系統(tǒng);HREF高電平有效,,對應(yīng)一行720個有效像素;VREF高電平有效,對應(yīng)一場信號中的286個有效行;ODD=1時,,標(biāo)志當(dāng)前場為奇數(shù)場;ODD=0時,,標(biāo)志當(dāng)前場為偶數(shù)場。采用16位RGB表示每個像素的彩色信息,。圖1(a)為數(shù)字化圖像中的一行像素的時序圖,。其中兩個HREF分別表示有效行的起始與結(jié)束位置,實際為一個信號;可以清楚地看到一行中有效的720個像素與像素時鐘LLC2的對應(yīng)關(guān)系,,在采集時通過幀存器控制電路選擇其中部的640個像素進(jìn)行采集。圖1(b)為一幀數(shù)字圖像的輸出時序圖,??梢钥吹皆诘?~22行時,VREF處于無效狀態(tài),,因此在后續(xù)的采集中,,這部分的信息不予處理并通過ODD的電平區(qū)分奇偶場數(shù)據(jù)。

1.2 去隔行支持

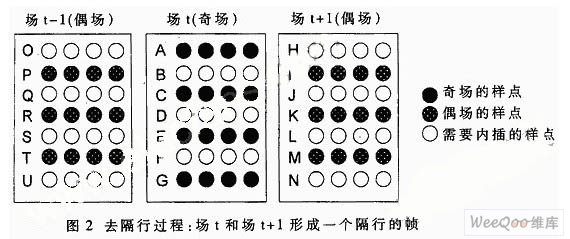

PAL制電視信號采用隔行掃描機(jī)制,,采用人眼的視覺暫留來實現(xiàn)兩場1/50s掃描312.5行的圖像構(gòu)成625行(一幀)圖像,。而標(biāo)準(zhǔn)的VGA顯示模式采用逐行掃描方式,在一個掃描周期內(nèi)實現(xiàn)對圖像的完全掃描,。因此需要對視頻信號進(jìn)行去隔行處理,。視頻信號在經(jīng)過緩沖后,按照取樣時鐘把經(jīng)過模數(shù)轉(zhuǎn)換的數(shù)字信號送入存儲器緩存,,通過數(shù)據(jù)內(nèi)插的方法進(jìn)行數(shù)據(jù)擴(kuò)展,,即相鄰行之間按照一定的算法進(jìn)行加權(quán),從而得到內(nèi)插行的數(shù)據(jù),,再以適當(dāng)?shù)乃俣茸x取處理后的數(shù)據(jù),,即可實現(xiàn)倍行頻/倍場頻的掃描,。倍行頻掃描可以消除行間的閃爍現(xiàn)象,倍場頻掃描雖然行掃描頻率不變,,但是場頻加倍,,即能消除行間閃爍現(xiàn)象,還可以消除場間的大面積閃爍,。去隔行問題的實質(zhì)就是在每一場中填補被跳過的那些行,,其過程如圖2所示。

實際上為實現(xiàn)去隔行已經(jīng)提出了很多簡單的濾波器,。一種選擇是用同一場中的垂直內(nèi)插值,,這是個一維二倍上轉(zhuǎn)換的問題。理想的垂直濾波器是一個半帶低通濾波器,。然而,,這個濾波器要求無限長度沖擊響應(yīng)是不可實現(xiàn)的。實際應(yīng)用中使用的是短得多的濾波器,。最簡單的是行平均,,它用丟失行的上一行和下一行的平均來估計該丟失行。在圖2中,,對于第t場,,D=(C+E)/2。由于沒有使用時域濾波,,所以它沿時間頻率軸具有全通特性,。為了改進(jìn)性能,另一種選擇是使用更長的垂直內(nèi)插濾波器,,其頻率響應(yīng)更接近理想的半帶低通濾波器,。對于第t場的行,滿意的內(nèi)插方法是D=(A+7C+7E+G)/16,。以上兩種方法都是只用了垂直內(nèi)插,。一種替代方法是使用時間內(nèi)插。值得注意的是,,對于一場中每個丟失行,,在同一幀的另一場中有一個對應(yīng)行。一個簡單的時間內(nèi)插方案是復(fù)制此對應(yīng)行,,即D=K,,J=C。這種方法稱為場合并,。因為每一個去隔行幀都由合并兩場獲得,但是這兩場的時間內(nèi)插是相反的(對于某些特殊圖案可能會產(chǎn)生視覺人為失真),。由于只在時間方向上進(jìn)行了濾波,因此在垂直方向上是全通的。

為了改進(jìn)性能,,可以使用一種對稱的濾波器,,例如,對前一場和后一場中的對應(yīng)行去平均以獲得當(dāng)前場中丟失的行,,即D=(K+R)/2,。這種方法稱為場平均。然而這種辦法內(nèi)插任何一場需要涉及三個場,,需要兩幀存儲器,。與場合并的方法相比,在存儲器容量和延時上有不可忽視的增加,。為了在時間和空間人為失真方面達(dá)到折衷,,較好的方法是既用垂直內(nèi)插也用時間內(nèi)插。例如,,通過對同一場中上一個和下一個像素以及前一場和后一場取平均進(jìn)行內(nèi)插的辦法得到一個丟失的像素,。綜上所述,當(dāng)成像的景物在相鄰兩場之間靜止時,,在奇數(shù)場中丟失的偶行數(shù)應(yīng)該與前一個和后一個偶場中對應(yīng)的偶數(shù)行完全一樣,。因此時間內(nèi)插將產(chǎn)生精確的估計。另一方面,,當(dāng)景物中存在運動時,,相鄰場中對應(yīng)行可能不在同一個物體位置上,時間內(nèi)插將產(chǎn)生不可接受的人為失真,。而同時使用空間和時間平均的方法將產(chǎn)生不太嚴(yán)重的人為失真,,但在存儲器容量和反應(yīng)時間方面作出犧牲。

通過上述方案的對比及系統(tǒng)的具體要求,,設(shè)計中采用了場合并的辦法,,具體實現(xiàn)由幀存控制器完成。

1.3 幀存控制器

幀存儲器是圖像處理器與顯示設(shè)備之間的通道,,所有要顯示的圖形數(shù)據(jù)先存放到幀存儲器中,然后再送到顯示設(shè)備進(jìn)行顯示,,因此幀存儲器的設(shè)計是圖形顯示系統(tǒng)設(shè)計的一個關(guān)鍵,。傳統(tǒng)上,可以實現(xiàn)幀存儲器的存儲器件有多種,,如DRAM,、SDRAM及SRAM等。DRAM,、SDRAM屬于動態(tài)存儲器,,容量大、價格全家但速度較慢,且在使用中需要定時刷新,。對于基于FPGA的視頻處理器,,需要設(shè)計專用的刷新電路,增加了系統(tǒng)設(shè)計的復(fù)雜程度,。SRAM速度高,、接口簡單、容量較小,。隨著集成電路技術(shù)的不斷發(fā)展,,容量不斷增大,價格也不斷下降,。在需要高速實時顯示的視頻處理系統(tǒng)中的使用越來越普遍,。

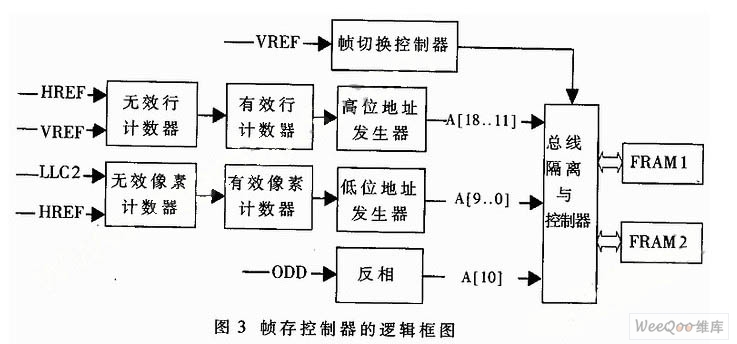

幀存控制器的設(shè)計對于實現(xiàn)兩種不同視頻系統(tǒng)之間的圖像信號的存儲、采集和顯示顯得非常重要,。為了保證數(shù)據(jù)處理與采集的連續(xù),,設(shè)計中使用了兩組幀存儲器(FRAM1、FRAM2),,由于數(shù)字化的圖像每幀大小為640×480=307200(16bit)共300K×16bit的數(shù)據(jù)量,,筆者使用每組512K×16bit的靜態(tài)存儲器,存儲時間為12ns,,可以保證快速地讀出和寫入圖像數(shù)據(jù),。圖3為幀存控制器的邏輯框圖。

由于輸入信號為隔行掃描的圖像數(shù)據(jù),,顯示輸出需要逐行掃描數(shù)據(jù),,因此數(shù)據(jù)存入幀存儲器時需要進(jìn)行處理。設(shè)計中采用場合并行法,,將兩場的數(shù)據(jù)寫入一個幀存中,,構(gòu)成一幅完整的逐行掃描圖像,系統(tǒng)利用VREF信號對此進(jìn)行控制,,產(chǎn)生的幀切換控制信號控制數(shù)據(jù)在兩個幀存中的切換,。當(dāng)VREF信號有效時,表明新的一場開始了,,此時無效行計數(shù)器開始工作,,控制不需要采集的圖像行,計數(shù)到閾值后,,有效行計數(shù)器開始工作,,控制所要采集的圖像行,并發(fā)出高位地十信號A[18..11];同樣,,當(dāng)HREF有效后,,無效像素計數(shù)器開始計數(shù)每行中的無效像素,然后有效像素計數(shù)器開始計數(shù)需要采集的行聽有效像素;每次計滿640個像素后,等待下一次有效行信號的到來,,同時將有效行計數(shù)器加1,。由于系統(tǒng)選用的幀存容量較大,因此利用ODD的反相信號作為幀存地址的A10,,為每行圖像提供了1024個存儲空間(實際使用640個),,可以簡化數(shù)據(jù)寫入與讀出的控制電路。隔行的視頻信號就會被逐行地存儲到幀存體中,??偩€隔離與控制電路用來完成數(shù)據(jù)在幀存中的寫入與讀出的同步。由于采用SRAM作為幀存體,,有效像素的寫入與后續(xù)視頻接口的讀出不能在一個幀存體中同時進(jìn)行,,系統(tǒng)采用雙幀存輪流操作的方法,系統(tǒng)采用雙幀存輪流操作的方法:當(dāng)數(shù)字化后的圖像信息寫入其中的一個幀存時,,幀存控制器將另一個幀存中的像素順序讀出,,送到顯示設(shè)備,反之亦然,。

1.4 視頻圖像的放大變換

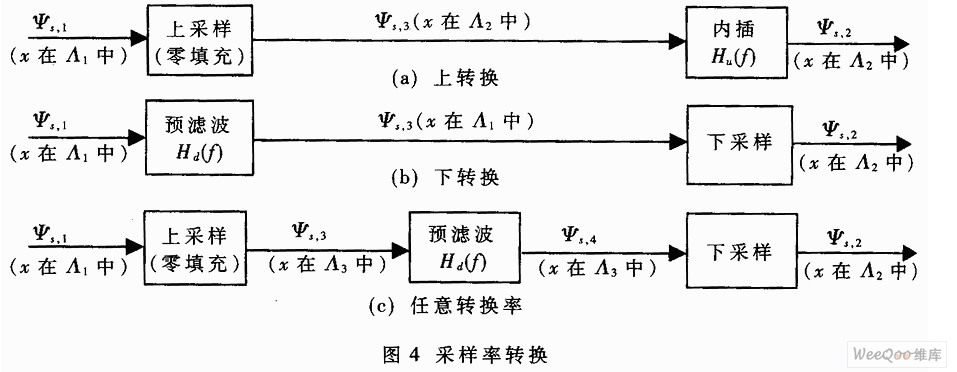

應(yīng)用柵格理論幾何變換處理過程可以按下面方式進(jìn)行描述:給定一個定義于點陣Λ1上已采樣信號,,需要產(chǎn)生一個定義于另一個點陣Λ2上的信號。如果,,Λ1中的每一個點也在Λ2中,,那么此問題是上轉(zhuǎn)換(或內(nèi)插)問題,可以先將那些在Λ2中而不在Λ1中的點添零(即零填充),,然后用一個作用于Λ2上的內(nèi)插濾波器估計這些點的值;若Λ1)Λ2,,即為下轉(zhuǎn)換(或抽取)問題,可以簡單地從Λ1中取出那么也在Λ2中的點,。然而,,為避免下采樣信號中出現(xiàn)混疊,需要對信號進(jìn)行預(yù)濾波,,以將其帶寬限制到Λ2*的沃格納晶體,。上轉(zhuǎn)換和下轉(zhuǎn)換的過程示于圖4(a)、(b)中,。更一般的情況,,如果Λ1和Λ2互相不包含,就需要找到另一個即包括Λ1又包括Λ2的點陣Λ3,,可以先將Λ1上采樣到Λ3,然后再下采樣到Λ2,。此過程示于圖4(c),。圖4(c)中Λ3中的中間濾波器完成兩個任務(wù):首先,內(nèi)插出Λ1中漏下的采樣點;其次把Λ3中的信號頻譜限制于Λ2*的沃格納晶格。

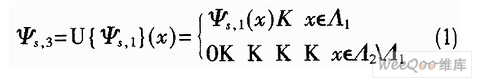

由于系統(tǒng)中進(jìn)行放大變換采用FPGA實現(xiàn),,因此本文討論的重點在于如何簡化實現(xiàn)并提高轉(zhuǎn)換速度,,上轉(zhuǎn)換中的上采樣過程為:

(1)式中Ψs,1和Ψs,3分別為原理圖像和上采樣信號;U(.)為上采樣運算;Λ2\Λ1表示在Λ2而不在Λ1內(nèi)的點的集合。插值濾波器的定義如下:

(2)式中,,d(Λ)為柵格Λ的采樣密度;v*表示柵格Λ的轉(zhuǎn)逆柵格的Voronoi單元,,即柵格Λ原點的單位元,它向所有柵格點平移將會無重疊地覆蓋整個連續(xù)空間,。最簡單的插值濾波為線性插值,,也可以采用二加權(quán)濾波的方法。圖像的縮放還可以采用3次樣條插值和小波分解的方法,,雖然這些方法在理論上可以取得很好的圖像縮放效果,,但計算復(fù)雜,即使采用快速算法,,也難以實現(xiàn)視頻圖像的實時顯示,。

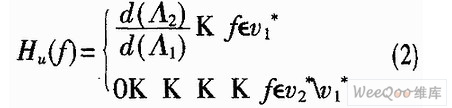

針對視頻信號數(shù)據(jù)量大、數(shù)據(jù)流速度的特點,,采用FPGA設(shè)計,,可以完成幀存控制、視頻信號的實時放大與疊加功能,?;谶\算速度與算法實現(xiàn)的難易程度分析,對視頻信號的放大采用了簡單的線性插值的辦法,,原理如圖5所示,。視頻信號是以場或幀進(jìn)行存儲的,由于數(shù)據(jù)寫入時存儲地址與圖像顯示的空間位置有確定的對應(yīng)關(guān)系,,因此系統(tǒng)需要的放大處理就變?yōu)閷鎯w的地址線的控制問題,。

對于本系統(tǒng)具體的4倍放大要求,將行同步信號先進(jìn)行二倍行使能運算,,并利用場同步信號對該寄存器進(jìn)行復(fù)位,,將生成后的二分頻行同步信號控制行地址發(fā)生器,也就是產(chǎn)生幀存儲器所需的高位地址;類似地利用像素時鐘,、行同步信號和場同步信號就可以得到所需的低位地址,。由于在幀存控制器向幀存儲器寫入數(shù)據(jù)時采用了一行點1024個位置的辦法,所以在低位地址后連接了一個比較器,,當(dāng)產(chǎn)生的低位地址小于640時,,幀存儲器的讀信號有效,否則無效,,以保證不會混疊入無效的數(shù)據(jù),。

1.5 VGA接口控制器

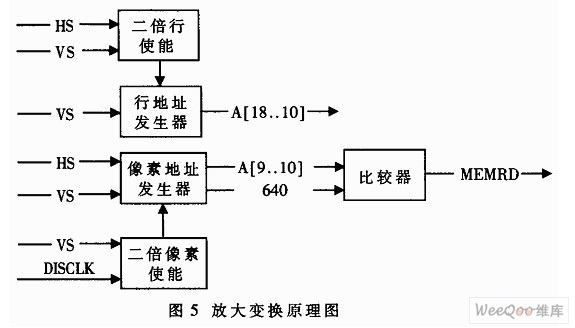

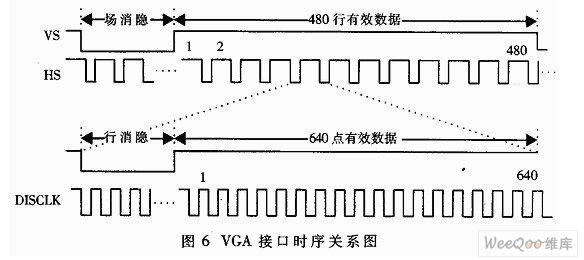

標(biāo)準(zhǔn)的VGA(640×480,,60Hz)接口需要提供以下幾組信號:3個RGB模擬信號、行同步信號HS和場同步信號VS,。它的信號時序如圖6所示,。

圖6中VS為場同步信號,場周期為16.683ms,,每場有525行,,其中480行為有效顯示行,45行為場消隱區(qū),,場同步信號每場有一個脈沖,,該脈沖的低電平寬度為63μs(2行)。行周期為31.78μs,,每顯示行包括800點,,其中640點為有效顯示區(qū),160點為行消隱區(qū)(非顯示區(qū)),。行同步信號HS每行有一個脈沖,。該脈沖的低電平寬度為3.81μs(即96個脈沖)。因此,,VGA控制器的任務(wù)就是按要求產(chǎn)生所需要的時序,。

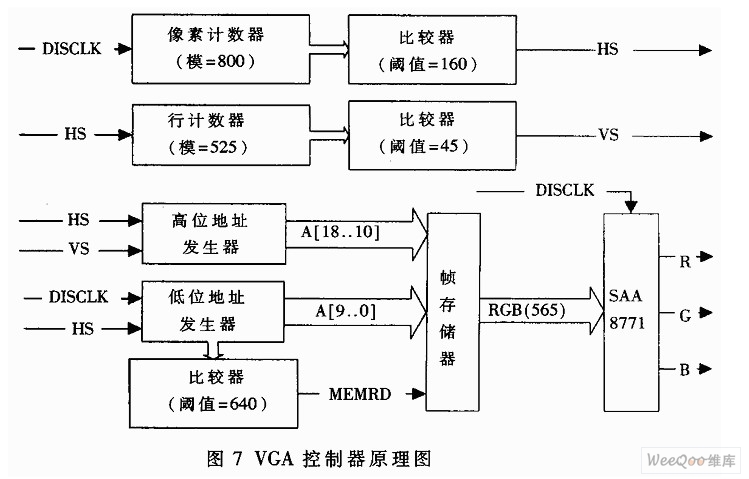

DISCLK為視頻顯示時鐘,頻率為25MHz,,首先輸入到模等于800的像素計數(shù)器中,,輸出的計數(shù)值與一個預(yù)先設(shè)好的比較器進(jìn)行比較,當(dāng)計數(shù)器的值大于160時,,輸出高電平,,反之輸出低電平,作為行同步信號;同理,,利用一個模等于525的計數(shù)器對行同步信號進(jìn)行計數(shù)和一個閾值為45的比較器可以產(chǎn)生所需要的場同步脈沖VS,。

產(chǎn)生的行、場同步信號和像素顯示時鐘分別被送到兩個地址發(fā)生器中,,產(chǎn)生所需要的控制幀存儲器的地址信號,。由于前面介紹的幀存控制器中采用為每行數(shù)據(jù)提供1024個存儲空間的辦法,因此在數(shù)據(jù)讀出時也要進(jìn)行相應(yīng)管理,。低位地址發(fā)生器產(chǎn)生的地址數(shù)據(jù)與一個比較器進(jìn)行比較,。當(dāng)?shù)刂沸∮?40時,幀存儲器的讀信號MEMRD位低電平有效,,否則無效,,這樣有效像素數(shù)據(jù)就被完整地提出。由于VGA是一個模擬的接口標(biāo)準(zhǔn),,RGB彩色信息需要輸入模擬量,,因此幀存儲器輸出的數(shù)字信息還要經(jīng)過D/A變換,。系統(tǒng)先用飛利浦公司出品的TDA8771AH,它內(nèi)部集成了三個視頻D/A轉(zhuǎn)換器,,基于電阻網(wǎng)絡(luò)架構(gòu),轉(zhuǎn)換速率最高可達(dá)35MHz,。由于它專用于數(shù)字電視,、視頻處理等相關(guān)領(lǐng)域,因此使用十分簡單,,只需要提供24bit數(shù)字信息和一個轉(zhuǎn)換時鐘即可,。VGA控制器原理圖如圖7所示。

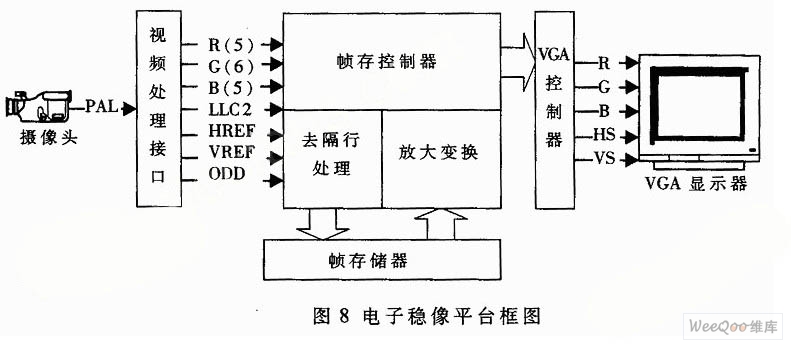

2 系統(tǒng)集成

綜上所述,,完整的電子穩(wěn)像系統(tǒng)結(jié)構(gòu)如圖8所示,。攝像頭輸入的信號采用PAL制式,經(jīng)過視頻處理接口后形成RGB565格式的數(shù)字視頻信號和控制信息;幀存控制器作為整個平臺的核心,,在將數(shù)據(jù)寫入幀存儲器的同時,,對數(shù)字化的圖像信息進(jìn)行去隔行處理,再將數(shù)據(jù)讀出送往VGA控制器時進(jìn)行放大變換,。VGA控制器則負(fù)責(zé)將數(shù)據(jù)按照VGA標(biāo)準(zhǔn)時序送往顯示器上,。

在該平臺上實現(xiàn)了文獻(xiàn)中K0等人提出的一種最簡單的基本位平面的電子穩(wěn)像算法,對于8位的灰度圖像,,可以表示為:利用第4層進(jìn)行運算,,其依據(jù)是在多幀圖像進(jìn)行BPM運算后發(fā)現(xiàn),該層的誤差結(jié)果較平滑,。然而,,K0的BMP-b4算法在不同的圖像序列和信噪比的情況下,并不能總得到一個最優(yōu)解;在某些情況下,,b4,、b5或b6會得到更好的結(jié)果。

目前資料顯示電子穩(wěn)像技術(shù)作為近年新興技術(shù)還處于試驗研究階段,,因其適用范圍廣闊而展現(xiàn)了樂觀的研發(fā)前景,。