由于不斷追求更高性能,,有效數(shù)據(jù)窗的單位間隔(UI)繼續(xù)縮短,。速率為1Gbps時,UI為1000 ps,;5Gbps縮短為200ps,;10Gbps則為100ps。對于100ps的有效數(shù)據(jù)窗,,在系統(tǒng)沒有連貫而可靠地發(fā)送和接收數(shù)據(jù)之前,,只能容忍很小的Tj (總抖動)。以上述速度傳輸時,,Tj結(jié)果需遠小于100ps,,而Rj (隨機抖動)更是以飛秒(fs)為單位。有什么技術(shù)和工具能用來檢定這些飛秒系統(tǒng)呢,?

基本上,,隨著速度的提升,高速I/O設(shè)計遭遇到較以往更大的挑戰(zhàn)。很多最新標準要求物理層的比特誤碼率為10–12,。然而,,隨著UI逐漸縮小,要想保持這個數(shù)量級的誤碼率也越來越難,。最終,,這就意味著設(shè)備級抖動要繼續(xù)縮短。例如,,5Gbps的SuperSpeed USB 3.0規(guī)定Rj為2.42ps RMS,;10Gbps的SFP規(guī)定Tj為28ps,Rj為1ps左右,。

定時分析

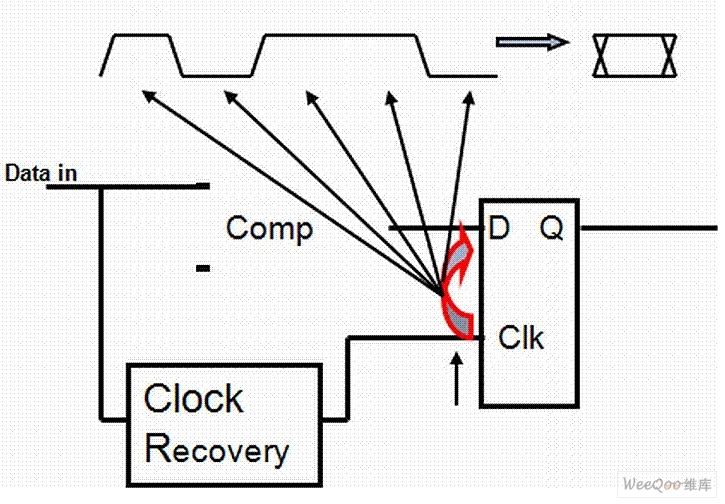

所有采用電壓變換來體現(xiàn)定時情況的電氣系統(tǒng),,都伴有討厭的定時抖動。當(dāng)信號速率不斷提高,、電壓擺動縮小以降低功耗時,,系統(tǒng)的抖動在信號發(fā)送間隔占到相當(dāng)大的比重。這種情況下,,抖動成為基本的性能限制。是否具有抖動檢定能力,,對成功運用符合性能要求的高速第三代(Gen 3)系統(tǒng)至關(guān)重要,。如圖1所示,每個時鐘的數(shù)據(jù)級,、上升沿和下降沿都在D處表示出來,。數(shù)據(jù)鎖存是數(shù)據(jù)通信的關(guān)鍵環(huán)節(jié),無論在何種工具(示波器或軟件仿真系統(tǒng))上,,都以眼圖形式顯示,。在每個時鐘上,邊沿的定時位置(如果有的話)有助于時鐘/數(shù)據(jù)延時統(tǒng)計分布,。這種位移即抖動或時間間隔誤差(TIE),。

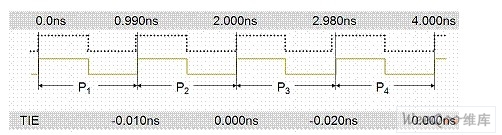

TIE抖動是相對已知或已恢復(fù)時鐘測量出的信號定時誤差。在串行數(shù)據(jù)的應(yīng)用中,,TIE通常被稱為抖動,。TIE很重要,,因為其甚至能顯示一段時間內(nèi)少量抖動的累積效應(yīng),。以圖2為例,每毫微秒時鐘邊沿的TIE標準偏差是9.6ps,。

圖1: 串行數(shù)據(jù)中的抖動,,每個時鐘的數(shù)據(jù)級、上升沿和下降沿都在D處表示出來,。

數(shù)據(jù)鎖存是數(shù)據(jù)通信的關(guān)鍵環(huán)節(jié),,在示波器上以眼圖形式顯示,。

圖2: TIE抖動測量有其他方法測量單波形抖動,,包括周期性抖動和cycle-to-cycle抖動。

然而,,測量信號波形上抖動的方法還包括測量周期抖動(period jitter)和相鄰周期間抖動(cycle-to-cycle jitter)。周期抖動是對信號的測量,,通常針對從一個沿到另一相似沿的重復(fù)信號。常見的周期測量工具,,會測量某一信號的上升沿到下一上升沿之間的數(shù)值,。采用數(shù)據(jù)傳輸方式(如DDR內(nèi)存),同時利用上升沿和下降沿來記時數(shù)據(jù)比特,,這時測量周期僅為半個周期,。在采集周期測量值的有效樣值后,可分辨標準偏差和峰值,。該統(tǒng)計數(shù)據(jù)即信號中的周期性抖動,。

對于相鄰周期間抖動,通過應(yīng)用簡單算法計算剛剛獲取的周期測量值,。如果已知兩個相鄰周期的定時信息,,其差值便是相鄰周期間變化:周期1減去周期2。此外,,對周期進行有效采樣,,并測量周期間的差值后,即可得出標準偏差和峰值,。統(tǒng)計出的數(shù)據(jù)即相鄰周期間抖動,。

抖動分量

將抖動按組成進行拆分,可提高精度并看清BER性能的根源,。最常用的抖動模型基于圖3所示的分級結(jié)構(gòu),。雖然也有分析抖動的其他方法,但這種方法是T11 FC-MJSQ所認可,,且目前最為常用的,,因為它直接顯示與BER性能相關(guān)的分量。

圖3: 按抖動類型進行的抖動分析

在這種分級結(jié)構(gòu)中,,首先將總抖動分為兩類:隨機抖動和確定性抖動(Dj),,然后再將確定性抖動分為若干類:周期抖動(Pj,,有時也稱正弦波抖動或Sj )、占空比抖動(DCD)以及數(shù)據(jù)相關(guān)抖動(DDj,,也稱符號間干擾ISI),。有時也會加入另外一個類別,即有界不相關(guān)抖動BUj,。

如果要測量在高信號速率時構(gòu)成Tj的各分量,,應(yīng)采用本底噪聲低,、頻率響應(yīng)平穩(wěn),、抖動測量底限低和觸發(fā)抖動小的儀器。例如,,ON Semiconductor發(fā)現(xiàn)在檢定其高速ECL器件時,,需采用系統(tǒng)抖動<200fs RMS而且?guī)捿^寬的儀器。芯片設(shè)計者發(fā)現(xiàn)幾個ps的信號移位,,甚至是在fs范圍內(nèi)的移位,,也可能干擾發(fā)送(TX)和接收(RX)性能。

值得注意的是,,盡管大多數(shù)串行通信標準都對抖動容差或抖動限值做出規(guī)定,,但其中所采用的技術(shù)參數(shù)較為模糊,或者在分析抖動時采用了不同的基本原理,。標準文件傾向于概述可量化的抖動限值,,但并沒有提出多少指導(dǎo)意見來幫助確定在特定應(yīng)用時哪一種限值更為重要。各種形式的抖動都有可能干擾系統(tǒng)BER,,不同的工具在檢測抖動時有不同的優(yōu)勢,。

解決具有挑戰(zhàn)性的抖動測量問題

最常見的抖動捕捉分析儀器是實時示波器。現(xiàn)代數(shù)字化儀表緊緊跟隨逐漸提升的數(shù)據(jù)率步伐,,可配置對抖動及其分量進行詳細分析的集成應(yīng)用軟件,。不過,選擇范圍并不局限于DSA和DPO,。其他完全不同的工具也有自己的優(yōu)勢,,其測量能力會出現(xiàn)部分重疊。這些工具包括誤碼率測試儀(BERT),、抖動分析儀,、計數(shù)器/定時器和頻譜分析儀。

實時示波器是電子研發(fā)和設(shè)計中最常用的測量工具之一,,因此當(dāng)需要分析研究抖動問題時,,它很可能成為第一道“防線”。DSA/DPO可在其帶寬和分辨率范圍內(nèi)進行幾乎所有類型的抖動測量,。

DSA/DPO具有抖動測量多功能性的原因在于:它可在多個DUT工作周期內(nèi)捕捉很長的時間窗,。由于示波器的采樣存儲器中保存著過去很長時間波形活動的歷史記錄,,因此我們能對隨著上升時間、脈沖寬度和各種抖動變化而變化的屬性進行研究,。

能處理10Gbps數(shù)據(jù)率的高端示波器的適用特性如下:

* 20 GHz帶寬,;

* 抖動本底噪聲低,大約300fs(300 x 10-15s),,能夠最小化DUT抖動測量對示波器的依賴性,。

* 8位捕捉,提供了足以應(yīng)對最新串行標準的動態(tài)范圍,,適合16級調(diào)制方案,。

方程式的重要部分是能提供使抖動測量和分析自動完成的工具集。抖動測量屬于一個精細學(xué)科,,但也有助于提供專用的軟件解決方案(假設(shè)示波器平臺支持這種功能),。

有些應(yīng)用的要求超過了實時DSA/DPO示波器的能力。這些儀器的實時帶寬和分辨率必須與DUT的數(shù)據(jù)率及其諧波相當(dāng),。此外,,部分形式的多級調(diào)制對儀器區(qū)分不同級別的能力有苛刻的要求,。這種情況下,,采用另一種抖動測量工具將更為合適。

采樣示波器

取樣示波器給抖動測量提供了較寬的帶寬,。取樣示波器可能是觀察數(shù)據(jù)率高達60Gbps信號的唯一有效工具,。而且,當(dāng)需要捕捉相對較“慢”的信號諧波時,,也適合采用取樣示波器,。

取樣示波器根據(jù)重復(fù)性輸入樣本來構(gòu)建波形采集,波形樣本來源于無數(shù)個周期,。許多類型的串行設(shè)備都能提供產(chǎn)生這種重復(fù)波形流的診斷回路,,或者利用外部數(shù)據(jù)生成器作為驅(qū)動源。

取樣示波器可配置應(yīng)用特有的抖動/噪音分析軟件包,,以提供抖動分離,、噪聲分離和BER目測等抖動分析功能。

影響抖動測量的示波器特性

定時精度是單次定時測量最重要的技術(shù)要求,,因為它決定著測量值有多接近實際值,。它既考慮了可重復(fù)性,也考慮了分辨率,。定時精度由許多因素決定,,包括采樣間隔、時基準確度,、量化誤差,、內(nèi)插誤差,、放大器垂直噪聲和取樣時鐘抖動。其中任何一種因素都會造成定時誤差,,而所有因素共同作用構(gòu)成增量時間精度(DTA),。高端示波器的DTA近似等于:

式中: A = 輸入信號幅度(V)

trm =10~90%被測量的上升時間(s)

N=輸入?yún)⒖荚肼?VRMS)

tj=中/短期孔徑不確定性(sRMS)

TBA =時基準確度(2ppm)

持續(xù)時間(duration)=增量時間測量值(sec)

所有這些都假設(shè)是采用高斯濾波器響應(yīng)產(chǎn)生的邊沿波形。

特定儀器的特殊DTA信息可以通過查閱其手冊找到,。通常情況下,,規(guī)范意味著對任何邊-邊的定時測量都可確定結(jié)果精度,對NIST是有保障并可追溯的,。上面的方程式中含有標度,、信號幅度、輸入噪聲和其他影響因素,。DTA這個話題太復(fù)雜,,無法在本文中進行全面的解釋。不過,,如果試圖按飛秒級來檢定定時系統(tǒng),,則應(yīng)考慮DTA。

測量分辨率

測量分辨率定義了可靠檢測測量變化的能力,,不要把它和測量精度,,甚至是測量重復(fù)性相混淆。在定時測量中,,分辨率是辨別信號定時中細微變化的能力,,而不管變化是有目的的,還是由噪音引起的,。硬件計數(shù)器的位寬度,、甚至計數(shù)器的電頻寬等基本因素,都會限制定時分辨率,。某些隱性的因素,,如執(zhí)行算術(shù)平均運算的軟件等,也會對定時分辨率構(gòu)成限制,。

硬件定時器中,,如像典型時間間隔分析器(TIA、SIA)等,,其定時分辨率的硬件限制在數(shù)百飛秒,。如果硬件計數(shù)器或等效電路的時鐘定在5GHz,那它就無法檢測到小于0.2ps的任何變化,。這是器件的物理局限,。

實時示波器的定時分辨率則受到采樣率、內(nèi)插精度和基于軟件的數(shù)學(xué)運算庫的限制,。在使用50Gsps采樣率和SIN(X)/X內(nèi)插時,,分辨率可能會達到幾十飛秒,。因為在這種情況下分辨率是基于數(shù)學(xué)運算庫的,因此實際分辨率低于一飛秒(0.0001ps),。

分辨率體現(xiàn)著測量定時中極細微變化的能力,,但這可能并不一定反映真實情況。想想,,當(dāng)測量變化小于儀器內(nèi)的固有噪聲時,,會發(fā)生什么情況?因此,,在測量小幅噪聲或抖動時,,必須考慮示波器系統(tǒng)的抖動本底噪聲。只是簡單地知道系統(tǒng)分辨率,,對理解精度或示波器的整體能力的實際極限并沒有什么幫助,。

抖動本底噪聲(JNF)

抖動本底噪聲(JNF)是抖動測量時儀器固有的噪聲。在示波器中JNF決定著可以檢測到的抖動底限,。JNF附近的抖動幅度客觀上是無法觀察到的,。驗證JNF的方法之一,便是測量沒有噪聲的,、完美定好的信號,。盡管理想的信號非常少見,不過可用來表征抖動本底噪聲的適合信號源還是存在的,。對于這種測試,,我們推薦采用的常用儀器為低相位噪聲的高精度射頻發(fā)生器,。還可采用反射脈沖不變的短接傳輸線,,來測量反射脈沖寬度。

高端示波器的JNF方程式如下:

式中FSj =最大輸入范圍,,所有這些都假設(shè)是采用高斯濾波器響應(yīng)產(chǎn)生的邊沿波形,。

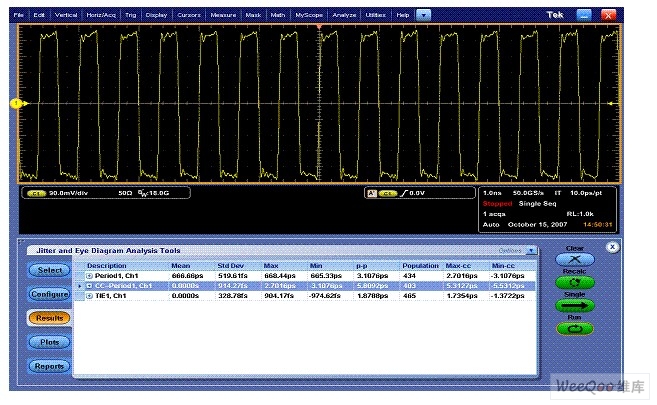

TIE用于測量JNF,因為它包括信號中的任意相位誤差,,無論高頻,、低頻、單事件或累積誤差,。此外,,采用實時儀器,TIE方法的基準可成為一個經(jīng)過計算的理想時鐘,。如圖4所示,,采用DPO/DSA實時示波器時,振蕩器上的TIE極小,,僅為328fs RMS,。

圖4: 實時示波器抖動本底噪聲的測量,,TIE為328 fs RMS。

影響JNF的另一因素,,是抖動噪聲的頻帶將含在結(jié)果中,。包括抖動在內(nèi)的所有噪聲都有頻率分量,波長從幾千米到幾埃,。當(dāng)測量JNF時,,還應(yīng)考慮所涉及頻帶上的限制。通常來說,,這些值表示最長記錄長度和最大取樣率上的JNF,。

目前市面上性能最好的一款FPGA是數(shù)據(jù)率為11.3 Gbps的Altera Stratix IV。圖5所示的測試報告,,根據(jù)高性能采樣示波器采集的數(shù)據(jù)生成,,當(dāng)Tj為22.18 ps時Rj僅395 fs。

圖5: Altera Stratix IV FPGA的抖動分析顯示圖( <400 fs Rj)