傳統(tǒng)的數(shù)字鎖相環(huán)設(shè)計(jì)在結(jié)構(gòu)上希望通過采用具有低通特性的環(huán)路濾波,從而獲得穩(wěn)定的振蕩控制數(shù)據(jù)。但是,在基于數(shù)字邏輯電路設(shè)計(jì)的數(shù)字鎖相環(huán)系統(tǒng)中,利用邏輯算法實(shí)現(xiàn)低通濾波是比較困難的。于是,出現(xiàn)了一些脈沖序列低通濾波計(jì)數(shù)電路,其中最為常見的是“N先于M”環(huán)路濾波器。這些電路通過對(duì)鑒相模塊產(chǎn)生的相位誤差脈沖進(jìn)行計(jì)數(shù)運(yùn)算,獲得可控振蕩器模塊的振蕩控制參數(shù)。脈沖序列低通濾波計(jì)數(shù)方法是一個(gè)比較復(fù)雜的非線性處理過程,難以進(jìn)行線性近似,所以無法采用系統(tǒng)傳遞函數(shù)分析方法確定鎖相環(huán)中的設(shè)計(jì)參數(shù),以及進(jìn)一步分析鎖相性能。在設(shè)計(jì)方法上多采用VHDL語言或者Verilog HDL語言編程完成系統(tǒng)設(shè)計(jì),并利用EDA軟件對(duì)系統(tǒng)進(jìn)行時(shí)序仿真,以驗(yàn)證設(shè)計(jì)的正確性。該種設(shè)計(jì)方法就要求設(shè)計(jì)者對(duì)FPGA硬件有一定的了解,并且具有扎實(shí)的硬件描述語言編程基礎(chǔ)。

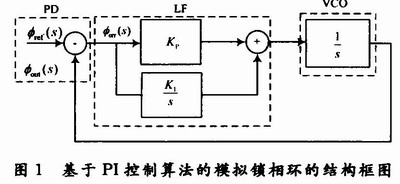

本文采用一種基于比例積分(PI)控制算法的環(huán)路濾波器應(yīng)用于帶寬自適應(yīng)的全數(shù)字鎖相環(huán),建立了該鎖相環(huán)的數(shù)學(xué)模型,并分析該鎖相環(huán)的各項(xiàng)性能指標(biāo)和設(shè)計(jì)參數(shù)之間的關(guān)系。利用DSP Builder直接對(duì)得到的鎖相環(huán)數(shù)學(xué)模型在Matlab/Simulink環(huán)境下進(jìn)行系統(tǒng)級(jí)的建模,并進(jìn)行計(jì)算機(jī)仿真,同時(shí)將建立的模型文件轉(zhuǎn)換成VHDL程序代碼,在QuartusⅡ軟件中進(jìn)行仿真驗(yàn)證,并用FPGA予以實(shí)現(xiàn)。

1 帶寬自適應(yīng)全數(shù)字鎖相環(huán)的理論分析

1.1 基于PI控制的模擬鎖相環(huán)的理論分析

鎖相回路是一個(gè)負(fù)反饋系統(tǒng),主要由鑒相器(PD)、環(huán)路濾波器(LF)和壓控振蕩器(VCO)三個(gè)部分組成。鑒相器的作用是計(jì)算輸入信號(hào)和輸出信號(hào)的之間的相位誤差。環(huán)路濾波器的主要作用是抑制噪聲及高頻分量,并且控制著環(huán)路相位校正的速度與精度。為了能夠提高鎖相系統(tǒng)的性能,本文采用基于PI控制算法的一階低通濾波器,即將鑒相模塊鑒別出的相位誤差大小乘以一定的比例系數(shù)而產(chǎn)生一個(gè)比例控制參數(shù),同時(shí)對(duì)相位誤差大小進(jìn)行積分,并在積分系數(shù)的調(diào)節(jié)下產(chǎn)生一個(gè)積分控制參數(shù),最終取比例和積分控制參數(shù)的和作為該環(huán)節(jié)的控制參數(shù)。壓控振蕩器的作用就是利用輸入的電壓值控制輸出信號(hào)的頻率。設(shè)壓控振蕩器的輸入信號(hào)為V0(t),輸出信號(hào)的頻率為ω0+KV0(t),則輸出信號(hào)的相位:

![]()

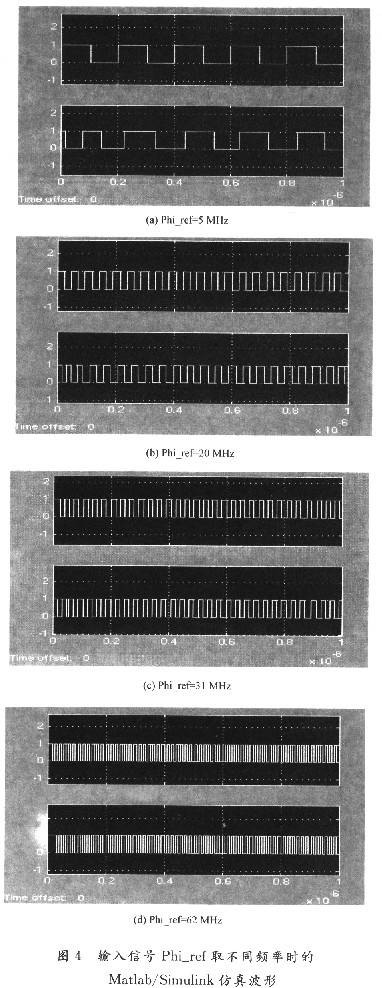

式中:![]() ,則壓控振蕩器的傳遞函數(shù)為:HVCO(s)=θf(s)/V0(t)=K/s,可以看出壓控振蕩器相當(dāng)于一個(gè)固有積分環(huán)節(jié)。在該設(shè)計(jì)中取壓控振蕩器的增益K=1,則通過以上的分析可得基于PI控制算法的模擬鎖相環(huán)結(jié)構(gòu)框圖如圖1所示。

,則壓控振蕩器的傳遞函數(shù)為:HVCO(s)=θf(s)/V0(t)=K/s,可以看出壓控振蕩器相當(dāng)于一個(gè)固有積分環(huán)節(jié)。在該設(shè)計(jì)中取壓控振蕩器的增益K=1,則通過以上的分析可得基于PI控制算法的模擬鎖相環(huán)結(jié)構(gòu)框圖如圖1所示。

由圖1可以得出,該鎖相回路的閉環(huán)傳遞函數(shù)為:

![]()

不難看出該系統(tǒng)是一個(gè)典型的二階系統(tǒng),那么二階模擬鎖相環(huán)的閉環(huán)傳遞函數(shù)可表示為:

式中:Kp和Kl分別為比例系數(shù)和積分系數(shù),取![]() 為系統(tǒng)的自然頻率;ζ為系統(tǒng)的阻尼系數(shù)。

為系統(tǒng)的自然頻率;ζ為系統(tǒng)的阻尼系數(shù)。

1.2 帶寬自適應(yīng)全數(shù)字鎖相環(huán)的理論分析

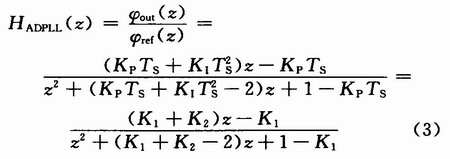

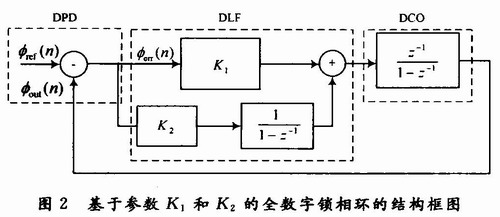

對(duì)上述模擬鎖相環(huán)的s域傳遞函數(shù)進(jìn)行離散化處理,采用脈沖響應(yīng)不變法即可得到全數(shù)字鎖相環(huán)回路的閉環(huán)傳遞函數(shù)為:

于是可以得到基于參數(shù)K1和K2的全數(shù)字鎖相環(huán)的結(jié)構(gòu)圖如圖2所示。

分析式(5)中得到的兩個(gè)參數(shù)K1和K2,若式中c和ζ為常數(shù),則參數(shù)K1和K2的變化只與輸入信號(hào)頻率ωref的變化有關(guān),因此,得到的全數(shù)字鎖相環(huán)模型具有自適應(yīng)的特性,這是傳統(tǒng)的全數(shù)字鎖相環(huán)不具有的新特點(diǎn)。

2 帶寬自適應(yīng)全數(shù)字鎖相環(huán)的DSP Builder建模

2.1 DSP Builder介紹

由于FPGA廣泛應(yīng)用,使得EDA軟件QuartusⅡ在很多領(lǐng)域中顯得尤為重要,目前全數(shù)字鎖相環(huán)的設(shè)計(jì)多是通過EDA技術(shù)完成,使用FPGA予以實(shí)現(xiàn)。這就需要設(shè)計(jì)者對(duì)FPGA硬件電路及硬件描述語言VHDL或者Verilog HDL非常熟悉;同時(shí),由于在QuartusⅡ環(huán)境下使用硬件描述語言進(jìn)行編程設(shè)計(jì)系統(tǒng)模塊時(shí)相當(dāng)繁瑣。而Matlab在搭建系統(tǒng)的數(shù)學(xué)模型方面功能強(qiáng)大,具有專門的建模仿真工具Simulink,可以進(jìn)行圖形化的建模仿真。但是Matlab本身不支持硬件電路,只能完成單純的數(shù)學(xué)模型的建模、仿真。如果把兩者的優(yōu)勢(shì)結(jié)合起來,使二者揚(yáng)長避短,則可以使復(fù)雜的電子系統(tǒng)的設(shè)計(jì)變得相當(dāng)容易且直觀。

DSP Builder是Altera公司推出的一個(gè)面向DSP開發(fā)的系統(tǒng)工具。它是作為Matlab的一個(gè)Simulink工具箱出現(xiàn)的,可以在atlab/Simulink環(huán)境下進(jìn)行圖形化建模仿真。DSP Builder中的模塊是以算法級(jí)的描述給出的,易于用戶從系統(tǒng)或者算法級(jí)進(jìn)行建模,甚至不需要十分了解FPGA本身和硬件描述語言。在DSPBuilder的模塊庫中還提供Matlab和QuartusⅡ的接口模塊Signal Compiler,利用該模塊可以方便地把在Ma-tlab/Simulink環(huán)境下建立的算法或者系統(tǒng)級(jí)模型轉(zhuǎn)化為FPGA可編譯的后綴為.vhd的VHDL語言程序。在QuartusⅡ中打開工程文件,可以對(duì)生成的程序進(jìn)行編譯、時(shí)序仿真,完成后可以結(jié)合FPGA開發(fā)板的引腳情況鎖定引腳,經(jīng)過編譯、適配后即可下載到FPGA開發(fā)板上完成硬件測(cè)試和硬件實(shí)現(xiàn)。

2.2 帶寬自適應(yīng)全數(shù)字鎖相環(huán)的DSP Builder建模

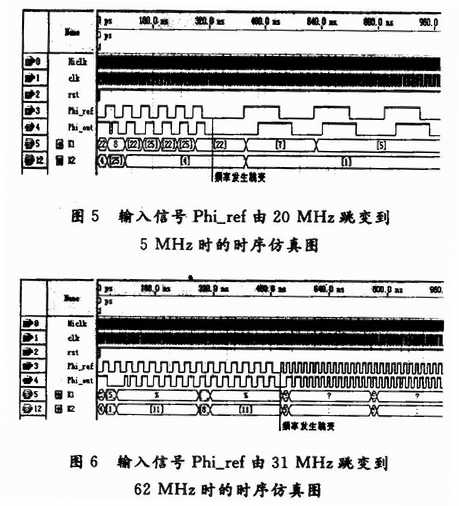

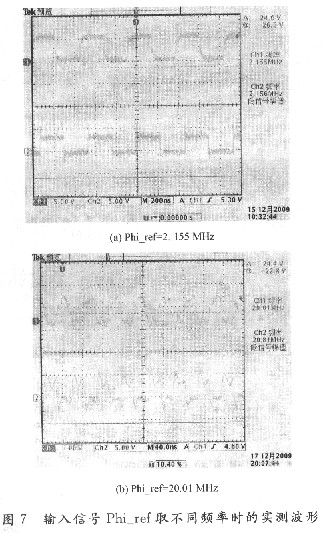

該設(shè)計(jì)方法就是在Matlab/Simulink環(huán)境下借助DSP Builder簡單、方便快速地建立上述分析得到的全數(shù)字鎖相環(huán)的數(shù)學(xué)模型,各個(gè)模塊建模方框圖如圖3所示。按照以上各個(gè)模塊方框圖連接,構(gòu)成整個(gè)系統(tǒng)模型,并加入系統(tǒng)時(shí)鐘Clock模塊和Signal Compiler模塊,即完成整個(gè)系統(tǒng)的。DSP Builder建模。其中輸入信號(hào)K1和K2是由式(5)計(jì)算得到,用6位無符號(hào)整數(shù)表示,K1和K2可以隨著輸入信號(hào)Phi_ref頻率的變化而自適應(yīng)的做出調(diào)整;Phi_ref和Phi_out分別為環(huán)路的輸入和輸出信號(hào),都采用1位無符號(hào)的整數(shù)表示。