1 引言

隨著雷達系統(tǒng)中數(shù)字處理技術的飛速發(fā)展,,需要對雷達回波信號進行高速數(shù)據(jù)采集,。在嵌入式條件下,,要求獲取數(shù)據(jù)的速度越來越快。精度越來越高,,以致數(shù)據(jù)量及處理速度要求大增,。為避免數(shù)據(jù)處理不及時,發(fā)生數(shù)據(jù)丟失,,影響系統(tǒng)可靠性,,要進一步提高系統(tǒng)實時性,必須研究開發(fā)高速嵌入式雷達信號采集系統(tǒng),。這里結合高速嵌入式數(shù)據(jù)采集系統(tǒng),,提出一種基于CvcloneⅢ FPGA實現(xiàn)的異步FIFO和鎖相環(huán)(PLL)結構來實現(xiàn)高速緩存,該結構可成倍提高數(shù)據(jù)流通速率,,增加數(shù)據(jù)采集系統(tǒng)的實時性,。采用FPGA設計高速緩存,,能針對外部硬件系統(tǒng)的改變,,通過修改片內(nèi)程序以應用于不同的硬件環(huán)境。由于FPGA可重配置,,可通過對其編程修改其電路功能,,方便后續(xù)的系統(tǒng)升級,。

2 高速雷達數(shù)據(jù)采集系統(tǒng)結構

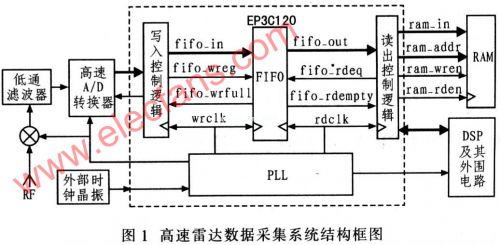

圖1為高速雷達數(shù)據(jù)采集系統(tǒng)結構框。

通過下變頻將接收的射頻信號變換為適合A/D采樣的中頻信號,。再經(jīng)A/D轉(zhuǎn)換器轉(zhuǎn)換為數(shù)字信號,,然后FPGA中異步FIFO構成的高速緩存將中頻采樣數(shù)據(jù)變換為與存儲器寫時間相匹配的低速數(shù)據(jù)并存儲到RAM中。DSP及其他數(shù)據(jù)處理器通過與RAM或FIFO間進行數(shù)據(jù)傳遞,,分析處理雷達回波信號,,就可獲取信號的特征和特征參數(shù)。如果DSP不通過緩存而直接與A/D相連,,在采樣過程中,,若A/D連續(xù)采樣數(shù)據(jù),DSP一直處于連續(xù)的間隔讀數(shù)狀態(tài),,這將占用DSP大部分處理時間,,導致DSP不能進行其他工作。也可能出現(xiàn)上一次的數(shù)據(jù)還沒被DSP處理完,,下一次采集過程就開始的情況,。如果選取更高速的A/D轉(zhuǎn)換器,甚至會發(fā)生數(shù)據(jù)丟失,,破壞系統(tǒng)的可靠性,。同時由于DSP不直接與A/D轉(zhuǎn)換器相連,所以A/D轉(zhuǎn)換器的升級或替代都不會影響原來的數(shù)據(jù)采集系統(tǒng),,且使用高速緩存后數(shù)據(jù)采集速率可達所采用的A/D轉(zhuǎn)換器輸出的最高速率,,能充分發(fā)揮DSP算法處理功能強大、速度高的優(yōu)勢,。而采用CycloneⅢFPGA設計高速緩存,,設計靈活、通用性強,。整個系統(tǒng)具有實時性高,、體積小、開發(fā)周期短,、易于維護和擴展,、適于實時信號處理等多個優(yōu)點。高速雷達數(shù)據(jù)采集系統(tǒng)的設計主要包括高速A/D轉(zhuǎn)換電路,、讀寫控制邏輯電路,、由雙時鐘FIFO構成的高速緩存電路、鎖相環(huán),、外部有源品振等,,盡量選用高速器件以提高數(shù)據(jù)采集系統(tǒng)的瞬時帶寬和存儲深度。

高速A/D轉(zhuǎn)換器采用MAX101A,其最高采樣速率可達到500 Ms/s,,采樣精度為8 bit,,該器件屬于直接轉(zhuǎn)換式模數(shù)轉(zhuǎn)換器即Flash A/D轉(zhuǎn)換器,其特點是速度快,,內(nèi)置1.2 GHz帶寬的采樣保持放大器,,特有的量化設計使其具有較好的動態(tài)特性。如果采集系統(tǒng)需更高的采樣速率,,可使用多片A/D交替采樣,。FPGA采用EP3C120,EP3C120利用65 nm低功耗工藝,,不但實現(xiàn)低功耗,,還具有豐富的邏輯(120 KB邏輯單元)、存儲器(高達4 Mbit),,及數(shù)字信號處理資源(288個DSP乘法器),。EP3C120的低功耗特性和其大容量的存儲器使其非常適合嵌入式高速雷達數(shù)據(jù)采集系統(tǒng)設計。采用異步FIFO構成的高速緩存即是使用FPGA巾高達4 Mbit容量的存儲器,。由于該器件具有乘法器,,可輔助DSP器件完成一些計算密集型的算法。

由于一般采用品振作為時鐘源,,通過上下變頻得到各個單元需要的時鐘,,但這又提高了系統(tǒng)的復雜度。這里采用CycloneⅢ系列FPGA可方便地解決此問題.EP3C120內(nèi)部集成有4個PLL單元,,各個PLL可為不同模塊提供不同的時鐘,,只需為系統(tǒng)提供一個高穩(wěn)定的晶振,通過PLL單元進行時鐘上下變頻即可,。

3 基于FPGA實現(xiàn)異步FIFO設計

異步FIFO是在兩個相互獨立的時鐘域下,,數(shù)據(jù)在一個時鐘域?qū)懭隖IFO而在另一個時鐘域又從該FIFO中將數(shù)據(jù)讀出。異步FIFO通常被用來將數(shù)據(jù)從一個時鐘域安全地傳送到另一個時鐘域,。FIFO可作為A/D轉(zhuǎn)換器件和DSP間的橋梁,。使用FIFO作為輸入緩沖,由A/D轉(zhuǎn)換器件把采樣轉(zhuǎn)換的值同步寫入FIFO,,每寫入一塊數(shù)據(jù)便向DSP發(fā)出一個信號,,以提醒DSP從FIFO中讀取數(shù)據(jù)塊。這樣比單次讀的效率要高的多,,不會有數(shù)據(jù)丟失,,且僅占用少量的系統(tǒng)資源。設計一個異步FIFO,,讀寫使能由不同的時鐘激勵控制輸入和輸出數(shù)據(jù),,空/滿標志既用來防止數(shù)據(jù)的上溢和下溢,,也作為寫入/讀出控制邏輯的輸入信號,用來控制A/D數(shù)據(jù)采樣過程和對DSP數(shù)據(jù)的傳輸,。當FIFO輸出滿標志時,寫入控制邏輯停止A/D采樣,,等待滿標志無效時恢復數(shù)據(jù)采樣,。從而防止數(shù)據(jù)丟失。當FIFO輸出空標志時,,讀出控制邏輯停止DSP的數(shù)據(jù)讀取,,等待空標志無效時恢復數(shù)據(jù)讀取。圖1中FPGA內(nèi)的寫入/讀出控制邏輯使用有限狀態(tài)機設計,,有限狀態(tài)機能有效的進行讀寫時序控制,,根據(jù)A/D和處理器的時序控制原理畫出狀態(tài)轉(zhuǎn)移圖,進行編程設定,。

FIFO的參數(shù)指標直接影響數(shù)據(jù)采集速度,。首先,F(xiàn)IFO的讀寫速度要足夠快,,其工作頻率至少要大于等于A/D轉(zhuǎn)換器件的采樣率,,才能充分發(fā)揮A/D轉(zhuǎn)換器件的高采樣率并保證無數(shù)據(jù)丟失。其次,,F(xiàn)IFO的存儲容量要適宜,,容量過大會造成資源浪費,容量過小會造成溢出或數(shù)據(jù)采集速度過慢,。系統(tǒng)FIFO采用EP3C120實現(xiàn),。由FPGA實現(xiàn)異步FIFO時,可方便的根據(jù)A/D轉(zhuǎn)換器的采樣精度和DSP數(shù)據(jù)寬度設計FIFO的輸人數(shù)據(jù)寬度和輸出數(shù)據(jù)寬度,,且采用PLL設計后,,可方便的調(diào)整FIFO寫入端和讀出端的時鐘頻率,使FIFO設計的高速緩存具有一定的通用性,。異步FIFO是在QuartusⅡ開發(fā)環(huán)境下利用其IP核設計的,,該設計的異步FIFO可支持高達256位的數(shù)據(jù)寬度;支持存儲的最大深度可達131 072words,同時支持空滿標志位,。表1給出系統(tǒng)在不同存儲深度時消耗FPGA片內(nèi)資源的情況,。可見,,針對不同的數(shù)據(jù)采集需求,,可利用Ahera公司提供的參數(shù)化的IP核方便的選擇FIFO的數(shù)據(jù)位寬度及存儲深度,避免資源浪費,。

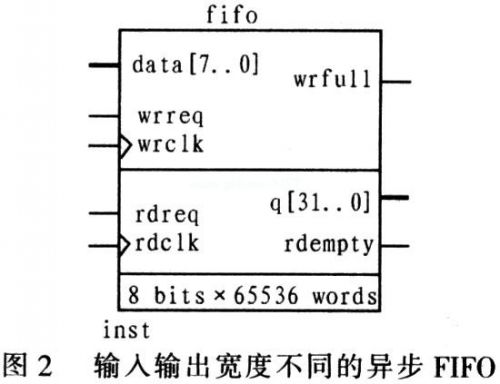

考慮到前端A/D轉(zhuǎn)換速度快,,精度為8位,,后端DSP的處理位數(shù)一般可做到32位,為提高系統(tǒng)實時性,,采用輸入數(shù)據(jù)寬度為8位,,輸出寬度為32位的雙時鐘FIFO,如圖2所示,。

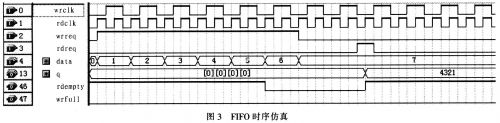

圖3為對FIFO仿真的結果,。雙時鐘FIFO輸入為8位、輸出為32位,,且FIFO兩端的讀寫時鐘頻率不同,。

分析系統(tǒng)的吞吐率:由于A/D數(shù)據(jù)輸入端口的速度固定,數(shù)據(jù)按采樣頻率輸入FIFO,,因此輸入數(shù)據(jù)的時間是不變的,,而DSP一次訪問可取走4個有效數(shù)據(jù),大大增加DSP讀取數(shù)據(jù)的吞吐率,,提高系統(tǒng)實時處理能力,。

4 基于FPGA的PLL設計

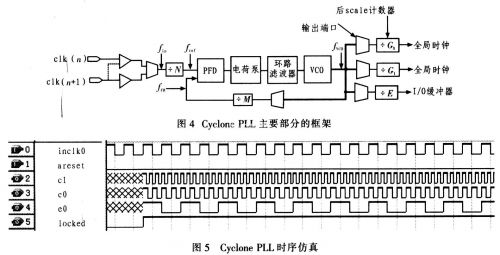

Cyclone FPGA具有鎖相環(huán)(PLL)和全局時鐘網(wǎng)絡,提供完整的時鐘管理方案,。Cyclone PLL具有時鐘倍頻和分頻,、相位偏移、可編程占空比和外部時鐘輸出,,進行系統(tǒng)級的時鐘管理和偏移控制,。Altera Quattus II軟件無需任何外部器件,就可啟用Cyclone PLL和相關功能,。PLL常用于同步內(nèi)部器件時鐘和外部時鐘,,使內(nèi)部工作的時鐘頻率比外部時鐘更高,時鐘延遲和時鐘偏移最小,,減小或調(diào)整時鐘到輸出(TCO)和建立(TSU)時間,。PLL主要部分的框架如圖4所示。

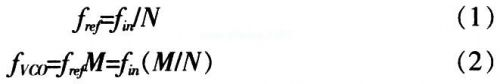

PLL模塊接收來自全局時鐘輸入引腳的時鐘信號,,經(jīng)鎖相環(huán)分/倍頻后作為異步FIFO的讀寫時鐘,,也可以作為外部A/D轉(zhuǎn)換器采樣時鐘。Cyclone PLL中包含一個前置分頻器N和一個倍頻器M,,設定范圍為1~32,。輸入時鐘fin經(jīng)預分頻N后得到參考時鐘fref:

通過設置后置分頻器的G0、G1和E值實現(xiàn)分頻和倍頻,。輸出的頻率為:

式中,fc0和fc1是全局時鐘,,為邏輯陣列塊(LAB)提供時鐘;fE則通過I/O單元輸出。

圖5為對PLL模塊仿真結果,。外部晶振輸入高穩(wěn)定時鐘到inclk0引腳,,經(jīng)PLL產(chǎn)生2倍頻時鐘c0,、3倍頻時鐘cl及經(jīng)分頻的時鐘e0。

可見使用FPGA內(nèi)部鎖相環(huán)能為高速雷達數(shù)據(jù)采集系統(tǒng)各部分產(chǎn)生時鐘源,,也使作為高速緩存的雙時鐘FIF0可應用于各種時鐘域場合,。

5 結論

本文在CycloneⅢFPGA中實現(xiàn)異步FIFO和鎖相環(huán)(PLL)結構的設計,避免復雜的時鐘管理,,簡化電路設計,,方便采集系統(tǒng)進行升級維護。高速緩存的設計使采集數(shù)據(jù)能的安全地實現(xiàn)數(shù)據(jù)跨時鐘域的傳遞,,提高了數(shù)據(jù)采集系統(tǒng)的可靠性。

本文來源于與非網(wǎng) http://www.eefocus.com

原文地址:http://www.eefocus.com/article/10-10/2075521287628827.html