摘? 要: 以磁懸浮列車速度控制系統(tǒng)" title="控制系統(tǒng)">控制系統(tǒng)為課題背景,介紹了以TMS320VC33為核心處理器的硬件平臺的組織結(jié)構(gòu)及設計過程。

關(guān)鍵詞: 速度控制? DSP? 硬件設計

?

長沙國防科大磁懸浮中心的磁懸浮鐵路試驗線是我國首條通過中試評審的磁懸浮線路,擁有自主的知識產(chǎn)權(quán)。列車的駕駛系統(tǒng)由S7_300系列PLC組網(wǎng)而成,主控PLC處理來自駕駛臺的控制命令,將處理后的控制信息通過FDL網(wǎng)傳給底層控制PLC,底層控制PLC根據(jù)網(wǎng)絡傳輸過來的命令控制車輛設備。駕駛臺上有一個12級位的控制手柄,列車的運行狀態(tài)由它來控制,通過調(diào)節(jié)級位間接改變牽引力的大小來控制列車運行速度。列車的駕駛主要依賴于駕駛員的經(jīng)驗,增加了駕駛員的負擔,在短途往返運行線路上極易疲勞。

基于DSP的磁懸浮列車速控系統(tǒng)就是在上述背景下提出的,采用速度控制系統(tǒng)后,駕駛臺給出的不再是控制力的大小,而是速度大小,由速度控制平臺根據(jù)算法動態(tài)改變列車牽引力。司機只需要改變級位,其它工作都由速控系統(tǒng)來完成。這樣既減輕了司機的工作負擔,同時又有助于提高列車的駕駛質(zhì)量。考慮到主控PLC并不適合進行數(shù)學運算,我們?yōu)樗倏叵到y(tǒng)專門設計了硬件平臺,它以TMS320VC33[以下簡稱VC33)DSP為核心,配以相應的接口,實現(xiàn)速度控制。

1 速控系統(tǒng)總體結(jié)構(gòu)

磁懸浮列車的運行速度很高,因此要求速度控制系統(tǒng)具有極高的實時處理速度。VC33 DSP是一種32位浮點處理器,它采用0.18微米制造工藝,是C3X家族的最新一代產(chǎn)品。VC33的功能結(jié)構(gòu)與C31相似,但由于在時鐘、電源、存儲區(qū)設計上做了優(yōu)化,其工作速度更快(每條指令執(zhí)行只需13ns)、功耗更小,并集成了較大的片內(nèi)存儲區(qū)。

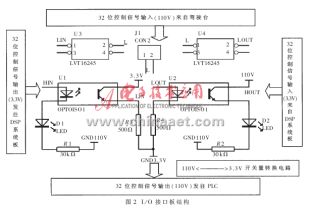

圖1虛線框中是速度控制系統(tǒng)的硬件平臺。它分為三部分:與駕駛臺的接口、DSP處理器、與PLC的接口。駕駛臺和PLC都是對數(shù)字I/O" title="I/O">I/O量進行操作,I/O量使用的是110V電源電壓,而DSP平臺的數(shù)字I/O量都為3.3V~5V,因此必須在I/O接口實現(xiàn)110V I/O量與3.3V I/O量之間的轉(zhuǎn)換。檢測系統(tǒng)測量并通過CAN總線上傳列車的速度與位置信息,主控PLC和DSP使用RS485接口接收。

?

?

2 數(shù)字I/O量接口板" title="接口板">接口板的設計

I/O接口板(見圖2)用光耦芯片TLP521-4實現(xiàn)110V開關(guān)量與3.3V開關(guān)量之間的電平轉(zhuǎn)換。用LVT16245作為DSP目標板與數(shù)字I/O轉(zhuǎn)換接口之間的鎖存器,控制數(shù)據(jù)流的方向,同時用作數(shù)據(jù)驅(qū)動器。它為三態(tài)輸出,未被選通時呈現(xiàn)高阻狀態(tài)。指示燈指示開關(guān)量信息。需要注意,R1、R2是限流電阻,考慮到功耗的關(guān)系,應選用大功率電阻(如2W)。

?

?

3 DSP控制面板的設計

3.1 電源時鐘電路

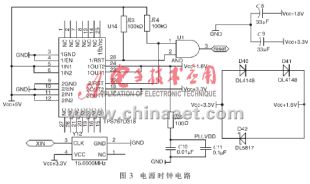

不同于C3X家族的其它成員,VC33使用兩種電源供電,3.3V作為芯片的工作電壓,1.8V作為芯片核心的工作電壓。采用兩種供電電壓既可以保證芯片對外圍電路的驅(qū)動能力,又可以有效地降低芯片功耗,減小發(fā)熱量。通常的電源僅提供5V的標準電源電壓,因此使用TPS767D318進行5V到3.3V和1.8V的電壓轉(zhuǎn)換,它可同時輸出3.3V和1.8V兩種電壓,最大可提供1A的電流。電源時鐘電路" title="時鐘電路">時鐘電路如圖3所示,圖中的二極管起保持輸出端電壓差的作用。

?

?

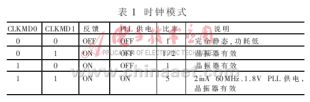

VC33 DSP強化了時鐘電路的作用,共有5個引腳作為時鐘電路的接入引腳。EXTCLK接外部時鐘源,此時DSP使用外部時鐘作為系統(tǒng)時鐘,不用時該引腳接地;XIN、XOUT接外部晶體振蕩器,作為DSP的基準時鐘源;CLKMD0、CLKMD1為時鐘模式選擇引腳,可基于基準時鐘源調(diào)整DSP的運行頻率,可選時鐘模式見表1。

?

?

3.2 存儲區(qū)電路設計

加大了片載存儲區(qū)容量是VC33明顯優(yōu)于C3x家族其它成員的地方。VC33共有34K32位存儲區(qū),24位地址線最大可訪問16M存儲空間。微處理器模式和微計算機模式分別定義了不同的存儲空間分配方式。處于微處理器模式時,DSP在仿真器監(jiān)控的條件下運行經(jīng)仿真器下載到SRAM存儲區(qū)中的程序;當處于微計算機模式時,DSP中的BOOTLOADER將存儲在ROM或FLASH中的程序下載至SRAM區(qū)并開始運行,此時仿真器不起作用。

VC33的片內(nèi)存儲區(qū)在實際應用中難以滿足運行程序與存儲數(shù)據(jù)的需要,因此必須為系統(tǒng)擴展外部存儲區(qū),包括靜態(tài)SRAM區(qū)和永久ROM區(qū)。SRAM區(qū)在系統(tǒng)工作時與VC33內(nèi)部存儲區(qū)結(jié)合使用,作為系統(tǒng)的工作區(qū),ROM區(qū)則永久保存運行程序和特定參數(shù),系統(tǒng)上電時由引導程序?qū)OM區(qū)中的程序和數(shù)據(jù)讀至SRAM區(qū)中。

VC33的高速特點要求擴展的SRAM必須有極高的存取速度,這里選用兩片64K×16bit的IDT71V016 SRAM組成64K×32bit片外存儲區(qū),其地址訪問時間僅為12ns,能夠滿足存取速度的要求。

由于系統(tǒng)只在上電和復位時訪問永久ROM,對它的存取時間要求不太高,采用一片512K×16bit的am29lv800b FLASH ROM,其訪問時間為60~120ns。FLASHROM可多次重復擦拭,數(shù)據(jù)保存時間長,寫入程序不需要額外的工具。瑞泰創(chuàng)新公司提供了專用的FLASH寫入程序,也可根據(jù)實際情況自己編寫,靈活性很好。

圖4是電路設計原理圖,用G20V8B進行地址選通,后面還會詳細介紹DSP板的地址選通邏輯。圖中CLKR0是串口" title="串口">串口式時鐘引腳,這里作I/O端口(可通過設置串口控制寄存器實現(xiàn)),接收FLASH狀態(tài)信號。

?

?

3.3 數(shù)字I/O接口設計

數(shù)字I/O接口用來與I/O接口板相連,發(fā)送和接收32位開關(guān)量控制信息。LVT16245用作32位數(shù)據(jù)線的總線驅(qū)動與數(shù)據(jù)鎖存器,保證信號的傳輸質(zhì)量。32位信號經(jīng)32位數(shù)據(jù)總線發(fā)送和接收,由相應的地址選通邏輯控制信號的讀取方向。因為DSP從駕駛臺讀取數(shù)據(jù),然后將數(shù)據(jù)發(fā)送至PLC,地址選通邏輯在控制LVT16245的數(shù)據(jù)方向的同時,還必須兼顧I/O接口板的數(shù)據(jù)流方向。

3.4 串口設計

DSP系統(tǒng)板需要采集來自RS485端口的速度位置信息。DSP自身帶有串口引腳,但其傳輸為同步方式,無法與異步方式的RS485接口相連。因此選用有自動流控功能的異步通信芯片TL16C550C實現(xiàn)DSP的串口通信(見圖5)。

?

?

??? TL16C550C(ACE)在從外設或Modem接收數(shù)據(jù)時實現(xiàn)從串口到并口的轉(zhuǎn)換,當從CPU接收數(shù)據(jù)時實現(xiàn)并口到串口的轉(zhuǎn)換,CPU可在任何時候讀取芯片的狀態(tài)。ACE包含完全的Modem控制能力和處理器中斷系統(tǒng),可配合來最小化通信連接軟件管理。

ACE包含波特率發(fā)生器,可對輸入時鐘分頻和倍頻,規(guī)則包含了接收器的16倍頻時鐘,ACE有1M波特的串口傳輸率,因此每一位耗時1μs,一個字節(jié)耗時10μs。

ACE包含了12個完全可訪問的寄存器,DSP可通過對這些寄存器的讀寫操作控制ACE的工作狀態(tài)。用A0~A2選擇寄存器地址,D0~D7讀寫寄存器內(nèi)容。

ACE可直接進行9線模式的串口通信。為提高串口的驅(qū)動能力,適應RS232和RS485標準,額外為其增加了兩片串口芯片MAX232、MAX485,使DSP板通過串口傳遞信息時不再需要額外的設備。通過跳線進行不同串口通信模式的轉(zhuǎn)換。

3.5 地址的分配與選通

上面介紹的存儲區(qū)、數(shù)字I/O端口、串口都需要占用DSP的16M地址空間,合理分配地址和選通引腳成為關(guān)鍵。VC33提供了一個專用的地址選通引腳 ,它與預解碼引腳

,它與預解碼引腳 配合使用,能夠快速訪問特定地址。本系統(tǒng)的地址分布比較復雜,使用GAL20V8B進行邏輯運算。表2是地址空間分配表。

配合使用,能夠快速訪問特定地址。本系統(tǒng)的地址分布比較復雜,使用GAL20V8B進行邏輯運算。表2是地址空間分配表。

?

?

參考文獻

1 TMS320VC3X User′s Guide. Texas Instruments, 1997

2 TMS320C3X General-Purpose Application User′s Guide.Texas Instruments,1998

3 陳 新,謝少軍.TMS320C32在開關(guān)預置SPWM控制中的應用.電氣自動化,2000[3]

4 彭啟宗,李玉柏. DSP技術(shù).成都:電子科技大學出版社,1997

5 王念旭. DSP基礎(chǔ)與應用系統(tǒng)設計.北京:北京航空航天大學出版社,2001

6 李廣軍,王厚軍.實用接口技術(shù).成都:電子科技大學出版社,1998