在無線電接收機" title="無線電接收機">無線電接收機系統(tǒng)中,由于會受到發(fā)射機運動、接收機運動和標準頻率隨時間動態(tài)變化等因素的影響,其接收機接收信號往往會發(fā)生頻率偏移,因而需要進行頻偏校正" title="頻偏校正">頻偏校正。在擴頻通信系統(tǒng)中,頻偏校正電路能消除中頻偏移對接收機擴頻碼的捕獲以及數(shù)據(jù)解調(diào)性能的影響,從而提高接收機的性能。

頻偏校正電路中通常需要根據(jù)給定相位產(chǎn)生余弦信號和正弦信號,其中最重要的實現(xiàn)技術(shù)是CORDIC" title="CORDIC">CORDIC (Coordinate Rotation Digital Computer,坐標旋轉(zhuǎn)數(shù)字計算機)算法。本文將詳細分析CORDIC算法的原理及其FPGA" title="FPGA">FPGA實現(xiàn)方法。

1 CORDIC算法的基本原理

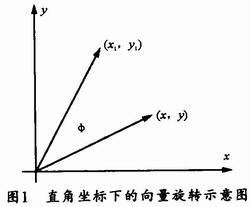

在直角坐標系統(tǒng)中,假設(shè)有一向量(x,y),按逆時針方向旋轉(zhuǎn)φ度得到向量(x1,y1),則兩向量的代數(shù)關(guān)系為:

在式(1)中,如果讓旋轉(zhuǎn)的角度φ滿足條件:tanφ=±2-i,則式(1)中的乘法操作就可以轉(zhuǎn)換為移位操作,從而很容易在FPGA中實現(xiàn)。圖l所示是直角坐標下的向量旋轉(zhuǎn)示意圖。若需要旋轉(zhuǎn)的角度為θ,那么就可以通過n次旋轉(zhuǎn)一系列預定角度αi來完成。

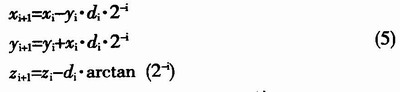

(2)式中,di表示每次旋轉(zhuǎn)的方向為αi。由于每次旋轉(zhuǎn)都為預定角度值,所以cosαi為常數(shù),而n次旋轉(zhuǎn)中每次迭代的處理可表示為:

![]()

關(guān)鍵字:FPGA 數(shù)頻率校正" title="數(shù)頻率校正">數(shù)頻率校正 CORDIC 無線電接收機 頻偏校正

一般情況下,當旋轉(zhuǎn)的次數(shù)足夠大時,Ki一般為常數(shù)。由于在實現(xiàn)時,可在最終的計算結(jié)果中再乘以這一常數(shù),所以,可以去掉式(3)中的Ki,這樣,迭代方程就僅含移位和加法運算,從而大大的簡化了FPGA的實現(xiàn)復雜性。由于還需要一個方程決定di的符號,引入變量zi表示每次旋轉(zhuǎn)預定角度的累加值:

![]()

這樣,CORDIC算法的迭代方程可表示為:

其最終結(jié)果為:

在頻偏校正電路中,通常需要根據(jù)給定相位θ產(chǎn)生余弦信號cosθ和正弦信號sinθ。為了產(chǎn)生標準且無放大的正弦和余弦信號,可令輸入向量的y分量(即yo)為0,x分量(即xo)為1/An,這樣,式(6)就可簡化為:

可見,經(jīng)過上述處理就可將輸入相位zo轉(zhuǎn)換為標準的正弦和余弦信號。

2 CORDIC算法的FPGA實現(xiàn)

用FPGA實現(xiàn)CORDIC算法,最常用的方法有迭代算法和基于流水線的算法。CORDIC迭代算法只有一級迭代單元,在系統(tǒng)時鐘的驅(qū)動下,可將迭代單元的輸出作為本級的輸入,并通過同一級迭代完成計算。迭代算法的硬件開銷很小,但完成一次CORDIC運算需要多個時鐘周期,其運算速度相對較慢。

在CORDIC流水線結(jié)構(gòu)算法中,每一級CORDIC迭代運算都使用單獨的運算單元,當流水線填滿之后,每個時鐘周期都馬上會計算出一組結(jié)果,所以計算速度很快。

雖然流水線結(jié)構(gòu)算法的計算速度很快,但其精度會受到流水線級數(shù)的限制。而要提高精度,就必須增加流水線級數(shù),從而增大硬件開銷,因此,流水線級數(shù)的選擇要兼顧速度和精度的要求。

關(guān)鍵字:FPGA 數(shù)頻率校正 CORDIC 無線電接收機 頻偏校正

3 實現(xiàn)方案與仿真結(jié)果

3.1 實現(xiàn)方案

CORDIC算法的流水線流程圖如圖2所示,該方法采用7級流水線,故可大大提高計算速度。

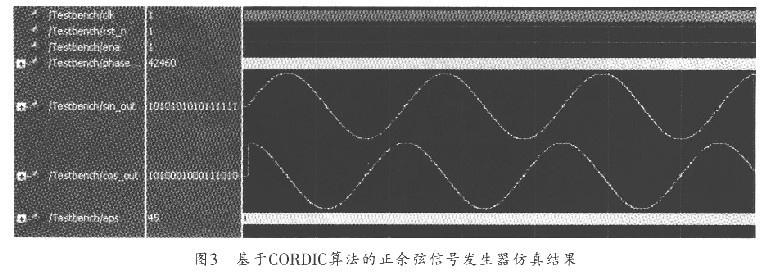

3.2 仿真結(jié)果

基于CORDIC算法的正余弦信號發(fā)生器的仿真結(jié)果如圖3所示,由圖3可見,該算法可以實現(xiàn)標準的正弦波和余弦波,并可直接作為頻偏校正單元。

4 結(jié)束語

本文通過對CORDIC算法的工作原理進行分析,給出了基于CORDIC算法和FPGA實現(xiàn)數(shù)字頻率校正的實現(xiàn)方案。仿真結(jié)果證明,該方法可以實現(xiàn)標準的正弦波和余弦波信號,可以直接作為頻偏校正單元來對數(shù)字頻率信號進行校正。