目前的衛(wèi)星遙感圖像壓縮系統(tǒng)硬件方案大多基于高性能可編程邏輯器件FPGA[2-4]。但這種方案整系統(tǒng)成本居高不下,且FPGA存在單粒子翻轉(zhuǎn)效應(yīng)。因此,筆者提出一種多DSP+FPGA的硬件設(shè)計結(jié)構(gòu),使用DSP取代FPGA完成核心算法,而僅用一個FPGA進(jìn)行管理和控制。該硬件設(shè)計成本較低。

1 基于雙正交疊式變換的低復(fù)雜度圖像壓縮方法

1.1 雙正交重疊變換的快速整數(shù)實現(xiàn)

在有損壓縮中,通常先對圖像矩陣進(jìn)行正交/雙正交變換,使能量分布集中,表示更為稀疏。離散余弦變換(DCT)由于具有良好的去相關(guān)效果,并且存在相應(yīng)的快速算法,應(yīng)用廣泛。雙正交重疊變換繼承了DCT 計算簡便、存儲要求低的特點(diǎn),同時克服了DCT的塊效應(yīng)。這里以LBT為藍(lán)本提出雙正交重疊變換的快速整數(shù)實現(xiàn)算法,所有系數(shù)均采用分母為2的冪、分子為整數(shù)的分?jǐn)?shù)近似,從而使整個變換過程只需要整數(shù)加法和位移運(yùn)算。圖1給出了一維binLBT的實現(xiàn)流程,二維變換按先行后列的順序分別進(jìn)行一維變換。

1.2 零樹編碼的簡化與改進(jìn)

SPIHT作為一種高效零樹編碼方法,對位平面進(jìn)行了集合劃分,將大量的非重要位0集中到幾個具有特定模式的集合里面,并對含有重要位的此類集合進(jìn)行劃分,直至將集合劃分為具體的元素。LBT系數(shù)塊中存在著類似零樹結(jié)構(gòu)。圖2中給出了模仿小波變換中樹結(jié)構(gòu)的LBT塊變換中的零樹劃分方法,其中每一個線框?qū)?yīng)著一個系數(shù),實線則將64個系數(shù)分為10個子帶。由于塊變換具有集中能量的作用,系數(shù)的能量由左上到右下逐漸減少。

在每一子帶中,首先使用Golomb方法編碼,再將其輸出碼流輸入到MQ編碼器,進(jìn)行下一步的編碼。零樹編碼過程應(yīng)用了零樹結(jié)構(gòu)中父子節(jié)點(diǎn)間的相關(guān)性,需要在已知父節(jié)點(diǎn)的情況下定位它的子節(jié)點(diǎn)。因此,在LBT系數(shù)輸出后進(jìn)入編碼器前,利用線性索引的方法對LBT系數(shù)重新排序,將其放置在一維數(shù)組里。

2 并行多DSP+FPGA的硬件設(shè)計方案

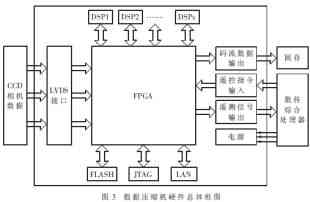

2.1 系統(tǒng)硬件整體框圖

數(shù)據(jù)壓縮系統(tǒng)硬件總體框圖如圖3所示。2x-1路串行CCD數(shù)據(jù)通過LVDS接口多路并行進(jìn)入FPGA進(jìn)行時序轉(zhuǎn)換,每個DSP通過兩個串口以EDMA方式從FPGA讀取兩路相機(jī)數(shù)據(jù)并緩存、壓縮編碼,整個數(shù)據(jù)壓縮系統(tǒng)需要x個DSP并行處理。壓縮后碼流數(shù)據(jù)通過串口輸出到FPGA,F(xiàn)PGA重新緩存、組幀、時序轉(zhuǎn)換后輸出到固存設(shè)備。碼流數(shù)據(jù)輸出、遙控指令輸入、遙測信號輸出和電源的接口均通過底板總線和數(shù)傳綜合處理器連接。

2.2 器件選擇

DSP選擇TMS320C6416,它是TI公司于2000年推出的一款具有C64XX系列新內(nèi)核的高性能DSPs芯片。TMS320C6416采用一種高性能的先進(jìn)的VLIW(非常長指令字)結(jié)構(gòu),其內(nèi)部具有8個并行處理單元。因單指令字長為32位,8個指令可組成長達(dá)256位的指令包,由內(nèi)部專門的指令分配模塊同時分配到8個處理單元同時運(yùn)行。因此在600MHz主頻時,TMS320C6416的最大處理能力高達(dá)4800MIPS(百萬條指令/秒)。TMS320C6416核心電壓為1.2V,外圍電壓為3.3V,主頻為400MHz"1GHz,并且在600MHz主頻下,能夠提供833B級器件。

FPGA選用X2V3000-5FG676C,該型號屬于Xlinix公司的Virtex-II系列,300萬門,676個管腳中包括484個I/O管腳。Xlinix FPGA的基本特點(diǎn)是由可配置邏輯塊(CLB)、輸入/輸出塊(IOB)以及可編程互連資源組成,另外還包括三態(tài)緩沖器、全局時鐘緩沖器和邊界掃描邏輯。CLB中包含有查找表(LUT)、寄存器和進(jìn)位邏輯,IOB中包含DDR寄存器。存儲器資源主要包括分布式SelectRAM/ROM以及18KB的塊狀SelectRAM。

2.3 接口設(shè)計

線陣CCD相機(jī)圖像灰度數(shù)據(jù)以串行方式及LVDS信號電平輸出。為了便于DSP串口接收,由FPGA進(jìn)行電平轉(zhuǎn)換,并依據(jù)相關(guān)串行協(xié)議進(jìn)行時序轉(zhuǎn)換。而壓縮圖像編碼則經(jīng)DSP串口輸出,由FPGA進(jìn)行電平轉(zhuǎn)換,并依據(jù)壓縮機(jī)輸出接口時序進(jìn)行相應(yīng)的轉(zhuǎn)換。

遙控機(jī)輸出線有指令線、地線,在使用端上拉。指令整形輸出后如需要負(fù)脈沖可再外加一級反相器或在FPGA內(nèi)部實現(xiàn)。遙測接口分為模擬遙測、數(shù)字遙測和數(shù)據(jù)遙測三部分,模擬遙測主要針對電源(5V、1.5V、1.4V等)進(jìn)行遙測,遙測輸出電平為0~5V;數(shù)字遙測主要對分機(jī)中關(guān)鍵器件工作狀態(tài)進(jìn)行遙測,遙測輸出電平為TTL電平;數(shù)據(jù)遙測主要對內(nèi)部運(yùn)行狀態(tài)進(jìn)行遙測。

3 壓縮算法在DSP實現(xiàn)中的關(guān)鍵技術(shù)及并行處理

3.1 C6000系列CPU結(jié)構(gòu)與流水線

C6000系列CPU采用哈佛結(jié)構(gòu),指令取指與執(zhí)行可以并行運(yùn)行。程序總線寬度為256bit,每一次取指操作都是取8條指令,成為一個取指包。取指、指令分配和指令譯碼都具備每周期讀取并傳遞8條32位指令的能力。C64xx系列CPU有兩個數(shù)據(jù)通路A和B,每個通路有4個功能單元(.L、.S、.M和.D),不同的8個功能單元中的指令均可并行執(zhí)行。

現(xiàn)代微處理器把指令分成幾個子操作,每個子操作在微處理器內(nèi)部可由不同的部件來完成。在同一時間內(nèi),可有多條指令交迭地在不同部件內(nèi)處理,這種工作方式就是“流水線”(pipeline)工作方式。TMS320C6000的特殊結(jié)構(gòu)可使多個指令包(每包最多8條指令)交迭地在不同部件內(nèi)處理,大大提高了微處理器的吞吐量。

3.2 數(shù)據(jù)類型轉(zhuǎn)換與數(shù)據(jù)溢出問題

TMS320C6000系列DSP的數(shù)據(jù)打包處理技術(shù),可以使用寬長度的存儲器對短字長的數(shù)據(jù)訪問,這樣可使編譯出的代碼性能顯著提高。壓縮算法在DSP實現(xiàn)中,采用short代替int來存儲圖像像素值和變換后的系數(shù),并確保不會產(chǎn)生數(shù)據(jù)溢出。

對|T|的每一行求和,最大為2.8284。進(jìn)行行列兩次變換,最終變換系數(shù)最大為圖像像素值的8倍。當(dāng)圖像像素占8位或10位時,包括符號位1位,16位存儲變換系數(shù)不會溢出。

3.3 并行計算

壓縮算法核心軟件結(jié)構(gòu)如圖4所示。

各子函數(shù)采用匯編語言編寫,在C6000系列DSP中優(yōu)化代碼的關(guān)鍵是如何實現(xiàn)代碼的并行。針對C64XX系列處理器的指令特點(diǎn),采取以下并行處理措施:

(1)雙通路。處理系數(shù)平均安排,分別分布在A、B兩通路;

(2)數(shù)據(jù)打包處理技術(shù)。用LDW和STW一次讀取和存儲兩個16位系數(shù);

(3)半字操作指令。每條指令處理兩個16位系數(shù);

(4)多功能單元。兩通路內(nèi)各8個系數(shù)的計算充分利用L、S、M和D四個功能單元。

4 實驗結(jié)果與結(jié)論

以一組40幅中科院遙感所提供的1024×1024×8圖像為樣本,用4:1和8:1兩種壓縮比,對遙感圖像壓縮系統(tǒng)樣機(jī)進(jìn)行測試。測試結(jié)果如下:

(1)壓縮比為4:1時,PSNR平均40dB以上,最低38dB;壓縮比為8:1時,PSNR平均35dB以上,最低32dB。

(2)對1024×1024×8圖像,壓縮比為4:1時,單DSP處理時間在64ms以下;壓縮比為8:1時,單DSP處理時間在48ms以下,為優(yōu)化前時間的1/30。

(3)單DSP內(nèi)部RAM能滿足2路相機(jī)數(shù)據(jù)及中間系數(shù)緩存要求;

(4)單路功耗在0.5W以下,整機(jī)功耗不足15W。

結(jié)果表明,數(shù)據(jù)壓縮系統(tǒng)設(shè)計合理,實際工作能滿足圖像質(zhì)量和高速實時處理要求。但從人工判圖的結(jié)果看,8:1壓縮時,算法小目標(biāo)保持情況不如JPEG2000。系統(tǒng)目前已進(jìn)入初樣階段,希望在算法尤其是編碼算法上繼續(xù)研究并優(yōu)化,進(jìn)一步提高圖像質(zhì)量。