摘要:利用鎖相環(huán)" title="鎖相環(huán)">鎖相環(huán)進(jìn)行載波跟蹤是獲取本地載波的一種重要方法,,針對鎖相環(huán)的噪聲性能和跟蹤速度不能同時(shí)達(dá)到最優(yōu)的限制,,在鎖相環(huán)PLL中引入自適應(yīng)模塊,,根據(jù)環(huán)路所處的環(huán)境自適應(yīng)對PLL環(huán)路參數(shù)做出調(diào)整。設(shè)計(jì)中利用仿真軟件MATLAB對自適應(yīng)鎖相環(huán)進(jìn)行仿真,,并在FPGA" title="FPGA">FPGA硬件板上利用 VHDL編程實(shí)現(xiàn),。在栽波信號為10 MHz、采樣率為80 MHz的條件下,,設(shè)計(jì)的自適應(yīng)鎖相環(huán)在噪聲水平較小時(shí)跟蹤速度提高了0.5μs左右,,在噪聲水平較高時(shí)相位抖動降低了0.01 rad左右。

關(guān)鍵詞:相干解調(diào),;PLL,;FPGA;EP3C10F256C8

對于相位調(diào)制信號,,相干解調(diào)為平均誤碼率最小的信號接收方式,。相干解調(diào)需要在本地產(chǎn)生與接收載波信號同頻同相的載波副本,鎖相環(huán)是相干解調(diào)系統(tǒng)中獲取本地載波副本時(shí)常用的方法,。對于鎖相環(huán),,噪聲水平和跟蹤速度是兩個(gè)非常重要的性能參數(shù),二者均取決于環(huán)路帶寬但是不能同時(shí)達(dá)到最優(yōu),。傳統(tǒng)鎖相環(huán)往往根據(jù)估算預(yù)先確定一個(gè)帶寬值,因而當(dāng)噪聲環(huán)境發(fā)生變化時(shí),,該值可能不是最優(yōu)值,,甚至不適

合當(dāng)前環(huán)境,。在傳統(tǒng)鎖相環(huán)的基礎(chǔ)上引入了自適應(yīng)調(diào)整模塊,根據(jù)當(dāng)前環(huán)境自適應(yīng)調(diào)整帶寬值,,確保無論鎖相環(huán)處于固定或變化的噪聲環(huán)境中均能工作在比較合適的帶寬下,,獲取較好的跟蹤效果。

1 同相正交環(huán)結(jié)構(gòu)

平方環(huán)和同相正交環(huán)都是解調(diào)系統(tǒng)中常用的跟蹤環(huán)路,,平方環(huán)的工作頻率較高,,對器件的性能要求較高,且平方環(huán)可能存在“理想平方器”的問題,。如果同相正交環(huán)中的環(huán)路濾波器與平方環(huán)中的環(huán)路濾波器相同,,則二者是等效的,同相正交環(huán)的環(huán)路中信號頻率較低,,對器件的性能要求較低,,因此設(shè)計(jì)中選用同相正交環(huán)。同相正交環(huán)主要由誤差提取模塊,、數(shù)控振蕩器(NCO)和環(huán)路濾波器組成,,如圖l所示。圖中虛線框?yàn)檎`差提取模塊,,用來鑒別本地振蕩信號與接收信號的載波分量之間的相位差,。環(huán)路根據(jù)提取出的相位差信號,不斷調(diào)整本地NCO,,最終使本地NCO和輸入信號的載波分量同頻同相,,并在此基礎(chǔ)上對接收信號進(jìn)行有效地相干解調(diào)。

2 NCO實(shí)現(xiàn)及性能分析

NCO常用在直接數(shù)字合成器(DDS)中作為其數(shù)字實(shí)現(xiàn)部分,。由此方法設(shè)計(jì)的DDS具有轉(zhuǎn)換時(shí)間短,、分辨率高、低相噪和輸出相位連續(xù)等特點(diǎn),。在鎖相環(huán)中,,NCO用于產(chǎn)生本地振蕩信號,由NCO同時(shí)產(chǎn)生本地的正弦及余弦信號,。該模塊由頻率控制加法器,、頻率控制累加寄存器和波形存儲器組成。輸入的頻率控制字在時(shí)鐘信號的驅(qū)動下進(jìn)行累加,,利用累加結(jié)果作為地址在波形存儲器中讀取預(yù)先存儲的正弦波數(shù)據(jù),。模擬鎖相環(huán)中,由模擬壓控振蕩器產(chǎn)生的本地正弦信號和余弦信號往往不能嚴(yán)格正交,,利用數(shù)字方法實(shí)現(xiàn)的NCO時(shí)可以較好地解決這一問題,,只需正確設(shè)置正弦信號和余弦信號對應(yīng)的初始地址即可。頻率控制字f_con與輸出f_out的關(guān)系為,其中fs表示采樣頻率,,系統(tǒng)中為80MHz,,2N為波形存儲器的容量,N對應(yīng)著該存儲器的輸入地址線的位數(shù),。

對于NCO,,其性能主要體現(xiàn)在最小相位誤差和最小頻率分辨率上。波形存儲器中通常存儲一個(gè)周期的正弦波,,因而最小相位誤差為:,。通過該式可以看出,N值取得越大,,最小相位誤差越小,。然而N越大,對應(yīng)的存儲器容量越大,,必然占用更多的邏輯資源,,因而不能無限制地增加N值。設(shè)計(jì)中N取12,,對應(yīng)最小相位誤差為0.0015 rad,。NCO的最小頻率分辨率為,其大小取決于頻率控制字的位數(shù),,為了有效增加頻率分辨率,,取NCO的頻率控制字位數(shù)M稍大于N,設(shè)計(jì)中取M為16,。

3 鑒相方法及性能分析

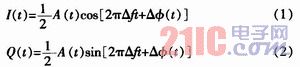

如圖l所示,,鑒相模塊是鎖相環(huán)的核心模塊之一,其精度和鑒別范圍直接影響鎖相環(huán)的性能,。系統(tǒng)接收信號為雙相移相鍵控(BPSK)信號,,設(shè)輸入信號為s(t)=A(t)cos(2πfct+φc(t)),本地載波信號為,。將輸入的BPSK調(diào)制信號與NCO產(chǎn)生的2路本地載波信號分別進(jìn)行相乘處理,,對產(chǎn)生的乘積信號分別進(jìn)行低通濾波,去除高頻信號,。為保持信號的線性相位及系統(tǒng)的穩(wěn)定性,,可采用有限沖激響應(yīng)(FIR)濾波器完成低通濾波處理。通過低通濾波處理去除高頻分量后,,得到

式中,,Q(t)、I(t)分別為鎖相環(huán)環(huán)路的同相信號和正交相信號,,其中,。

鑒相處理即是對上述信號進(jìn)行相應(yīng)處理以得到對應(yīng)的相差信號,。常用的鑒相方法有正弦鑒相法,2倍角正弦鑒相法,,正切鑒相法和反正切鑒相法,。其數(shù)學(xué)表達(dá)式分別對應(yīng)為:sign(I(t))·Q(t),I(t)·Q(t),,Q(t)/I(t)和arctan[Q(t)/I(t)]。鑒相法的線性度越好,、鑒相范圍越廣,,則相應(yīng)的鎖相環(huán)可跟蹤的頻率范圍越大。利用仿真軟件MATLAB對上述4種鑒相法對應(yīng)的鎖相環(huán)進(jìn)行仿真,。仿真參數(shù)對應(yīng)實(shí)際系統(tǒng)中設(shè)置的參數(shù),,即采樣速率為80 MHz,接收信號中載波分量的頻率為lO MHz,。多次實(shí)驗(yàn)結(jié)果顯示:隨著起始頻差的不斷增加,,2倍角正弦鑒相法對應(yīng)的鎖相環(huán)最先出現(xiàn)跟蹤不上的情況,隨后是正弦鑒相法對應(yīng)的鎖相環(huán),,最后是正切鑒相法和反正切鑒相法對應(yīng)的鎖相環(huán),。

用FPGA實(shí)現(xiàn)上述4種鑒相器時(shí),正弦鑒相法使用少量的邏輯語句即可實(shí)現(xiàn),,占用的邏輯資源較少,;2倍角鑒相法需要使用一個(gè)乘法器模塊,在邏輯資源的占用上比正弦鑒相法稍多一些,;正切鑒相法可選用查表法或者坐標(biāo)旋轉(zhuǎn)數(shù)字計(jì)算機(jī)CORDIC方法,,占用的邏輯資源較多;反正切鑒相法可使用CORDIC方法實(shí)現(xiàn),,占用的邏輯資源也比較多,。設(shè)計(jì)中可根據(jù)系統(tǒng)的資源情況和性能要求在上述4種鑒相方法中進(jìn)行選擇。本文中設(shè)計(jì)的模塊應(yīng)用在基于FPGA的直序擴(kuò)頻接收機(jī)中,,對資源占用具有比較嚴(yán)格的限制,,考慮到正弦鑒相法已經(jīng)能夠滿足當(dāng)前系統(tǒng)的性能要求,因此選用正弦鑒相法,。

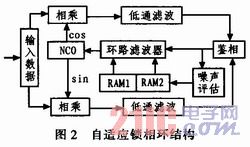

4 自適應(yīng)鎖相環(huán)

噪聲水平和跟蹤性能是鎖相環(huán)的兩個(gè)重要性能參數(shù),,但是二者是相互對立的,鎖相環(huán)處于噪聲環(huán)境中時(shí),,環(huán)路帶寬越大,,跟蹤速度越快,同時(shí)引入的噪聲越多,;環(huán)路帶寬越小,,引入的噪聲越少,,同時(shí)跟蹤速度越慢。通過對鎖相環(huán)的傳遞函數(shù)進(jìn)行分析得出,,鎖相環(huán)的環(huán)路帶寬取決于鎖相環(huán)中環(huán)路濾波器的帶寬,,對環(huán)路濾波器的帶寬進(jìn)行調(diào)整即是對鎖相環(huán)的帶寬進(jìn)行調(diào)整。實(shí)際應(yīng)用中,,鎖相環(huán)處于噪聲水平較低的環(huán)境中時(shí),,其參數(shù)跟蹤速度更為重要,此時(shí)應(yīng)盡可能增加環(huán)路帶寬,,相反,,噪聲水平較高時(shí),獲取較小的相位抖動更重要,,此時(shí)應(yīng)盡可能減小環(huán)路帶寬,,抑制噪聲信號。設(shè)計(jì)中按照這一思路,,引入噪聲評估模塊,,根據(jù)當(dāng)前環(huán)境中噪聲的大小對環(huán)路濾波器的帶寬進(jìn)行自適應(yīng)調(diào)整。自適應(yīng)鎖相環(huán)結(jié)構(gòu)如圖2所示,,自適應(yīng)鎖相環(huán)在傳統(tǒng)鎖相環(huán)的基礎(chǔ)上引入了噪聲評估模塊和系數(shù)調(diào)整模塊,。

4.1 環(huán)路濾波器

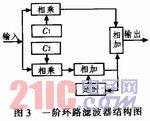

鎖相環(huán)中的環(huán)路濾波器是一個(gè)線性低通濾波器,它主要有2個(gè)功能:1)濾除誤差信號中的高頻分量,;2)為鎖相環(huán)路提供一個(gè)短期的記憶,,對環(huán)路的校正速度起到調(diào)節(jié)作用。模擬鎖相環(huán)中的環(huán)路濾波器由電阻,、電容和運(yùn)算放大器等線性元件組成,,如RC積分濾波器、無源比例積分濾波器,、有源比例積分濾波器等等,,數(shù)字環(huán)路中的環(huán)路濾波器可利用雙線性變換和它們一一對應(yīng)。設(shè)計(jì)中以有源比例積分濾波器為原型,,通過雙線性變換得到,。鎖相環(huán)的階數(shù)比環(huán)路濾波器的階數(shù)大1。環(huán)路濾波器的階數(shù)越高,,對應(yīng)鎖相環(huán)的跟蹤性能越強(qiáng)大,,二階環(huán)路濾波器對應(yīng)的三階鎖相環(huán)具有跟蹤加速度頻率輸入的特性,對于本系統(tǒng),,二階鎖相環(huán)已經(jīng)滿足要求,,因此采用一階環(huán)路濾波器,與之對應(yīng)的環(huán)路濾波器的數(shù)字化結(jié)構(gòu)如圖3所示,。

圖3中C1,、C2為環(huán)路濾波器的系數(shù),,將此濾波器的傳遞函數(shù)引入鎖相環(huán),得出鎖相環(huán)的傳遞函數(shù),,對照標(biāo)準(zhǔn)形式

式中,,ωn、T分別對應(yīng)鎖相環(huán)的自然角頻率和環(huán)路調(diào)整時(shí)間間隔,,可根據(jù)系統(tǒng)要求進(jìn)行取值,,設(shè)計(jì)中取T為采樣時(shí)間間隔,即每個(gè)點(diǎn)調(diào)整一次,,ζ取常用值 0.707,,ko、kd分別對應(yīng)鑒相增益和相位控制靈敏度,,BL表示環(huán)路噪聲等效帶寬。由式(3)~式(5)可知,,噪聲等效噪聲帶寬BL和環(huán)路濾波器系數(shù) C1,、C2一一對應(yīng),因此改變噪聲帶寬即可通過調(diào)整系數(shù)C1,、C2實(shí)現(xiàn),。傳統(tǒng)鎖相環(huán)中,取固定值,,一般選取滿足條件BL≤ O.1Rb的值,,其中Rb為信息數(shù)據(jù)速率。

4.2 系數(shù)調(diào)整

相干解調(diào)系統(tǒng)中,,同步系統(tǒng)的相位誤差直接影響著系統(tǒng)的誤碼性能,,其對應(yīng)關(guān)系為:,其中ψ為相位誤差,。因此噪聲水平較高時(shí),,應(yīng)該盡可能減小噪聲帶寬,近而減小ψ值,,噪聲水平較低時(shí),,適當(dāng)增加噪聲帶寬,加快跟蹤速度,。

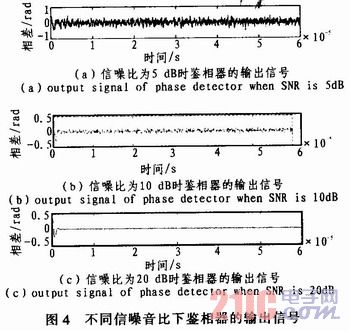

利用仿真軟件MATLAB對3種噪聲水平下的輸入信號進(jìn)行相位跟蹤仿真,,3種情況下,鎖相環(huán)參數(shù)相同,,輸入的調(diào)制信號相同,,不同的是對信號疊加3種功率不同的噪聲。結(jié)果顯示,,鎖相環(huán)中引入的噪聲越大,,則鑒相器模塊輸出信號的抖動越大,。輸入信號的信噪比為5、10和20 dB時(shí),,鑒相器模塊的輸出信號如圖4所示,。

由圖4可以看出,噪聲水平越高,,則鑒相器的輸出信號抖動越厲害,,于是設(shè)計(jì)中利用鑒相器輸出信號的抖動狀況來判斷鎖相環(huán)中的噪聲水平,并根據(jù)噪聲水平來調(diào)整 C1,、C2值,。MATLAB仿真結(jié)果顯示,鑒相器的輸出值是在0值上下浮動,,因此利用FPGA實(shí)現(xiàn)此功能時(shí),,可利用鑒相器輸出值的絕對值或平方值判斷噪聲大小,浮動越大則噪聲水平越高,。利用單個(gè)點(diǎn)的抖動來判斷時(shí),,具有一定的偶然性,結(jié)果不準(zhǔn)確,,容易產(chǎn)生誤判,,因此,在FPGA硬件板上利用VHDL編程實(shí)現(xiàn)時(shí),,對鑒相器的輸出數(shù)據(jù)取絕對值或進(jìn)行平方處理,,并對連續(xù)15個(gè)點(diǎn)的絕對值或平方值進(jìn)行累加運(yùn)算,利用累加的結(jié)果來判斷相位抖動的大小,。對15個(gè)點(diǎn)取和時(shí),,利用樹形加法結(jié)構(gòu),引入流水線設(shè)計(jì)方法,,使各個(gè)加法器并行工作,,確保輸出結(jié)果的速率和輸入數(shù)據(jù)的速率相等。計(jì)算過程中使用絕對值代替平方值,,能獲取與平方值相似的結(jié)果,,有效降低運(yùn)算量。進(jìn)行帶寬調(diào)整時(shí),,可以利用當(dāng)前應(yīng)該設(shè)置的BL值計(jì)算出與之對應(yīng)的環(huán)路濾波器系數(shù)C1,、C2由式(3)~式(5)可以看出,通過BL計(jì)算C1,、C2時(shí)比較復(fù)雜,,涉及多次除法運(yùn)算、乘法運(yùn)算以及加法運(yùn)算,,在FPGA中,,實(shí)現(xiàn)除法器,、乘法器都是比較占用邏輯資源的,因此設(shè)計(jì)中不采用直接計(jì)算的方法,,而是利用查找表法來實(shí)現(xiàn),,首先訂制2個(gè)容量為256的ROM,將可取的帶寬值平均劃分為256等分,,對每個(gè)帶寬值對應(yīng)的C1,、C2 值預(yù)先進(jìn)行計(jì)算,計(jì)算結(jié)果經(jīng)量化處理后,,以MIF文件的形式分別加載到ROM1,、ROM2。ROM1,、ROM2的地址線均為8位設(shè)計(jì)中連接到同一信號,,對應(yīng)地址范圍為0x00到OxFF,由圖2中的噪聲評估模塊產(chǎn)生,。噪聲評估模塊輸出的初始值設(shè)置為0x7F,,即初始帶寬值設(shè)置為可取范圍段的中間值,之后根據(jù)噪聲評估模塊的結(jié)果,,與提前設(shè)定的上限值、下限值進(jìn)行比較,,并根據(jù)比較結(jié)果調(diào)整帶寬值,,其中上限值、下限值通過仿真得出,,這兩個(gè)域值與FPGA實(shí)現(xiàn)時(shí)采用的位寬,、位截短處理、濾波處理等有關(guān),。為防止過于頻繁地進(jìn)行調(diào)整,,程序中設(shè)定,如果連續(xù)3次的抖動高于上限值且當(dāng)前地址值大于Ox00,,則減小帶寬值 (即地址減1),,相反,若連續(xù)3次的抖動低于下限值且當(dāng)前地址值小于0xFF,,則增加帶寬值(即地址加1),。

鎖相環(huán)啟動工作時(shí),不論噪聲水平高低,,鑒相器輸出信號的抖動都比較大,,連續(xù)3次抖動高于上限值是比較正常的,這時(shí)若將帶寬值減小,,會降低跟蹤速度,。因此設(shè)計(jì)中限定,,只有本振信號的相位和接收載波信號的相位大致相符后,才允許減小帶寬值,。因此環(huán)路設(shè)計(jì)中需要判斷相位是否大致相符,。

參看結(jié)構(gòu)圖l,經(jīng)低通濾波后的同相和正交支路的信號分別為:,。相位大致相符時(shí),,取值較小,I(t)2應(yīng)大于Q(t)2,。設(shè)計(jì)中利用條件判斷是否已滿足相位大致相符的條件,。二者之差的下限值c同樣與系統(tǒng)中的輸入數(shù)據(jù)位數(shù)、濾波器等模塊有關(guān)系,,可在Modelsim或Quartus下通過測試獲得,。為了增加判斷的準(zhǔn)確性,設(shè)計(jì)中同樣做出限定,,連續(xù)3次滿足條件時(shí),,才判定相位已大致相符。

5 實(shí)驗(yàn)結(jié)果及分析

設(shè)置中頻載波信號為10 MHz,,采樣頻率為80 MHz,,本地初始中心頻率為9.9 MHz。在信噪比固定為25 dB和信噪比變化的情況下,,分別利用傳統(tǒng)的鎖相環(huán)和圖2所示的自適應(yīng)鎖相環(huán)進(jìn)行相位跟蹤,,得到的相差結(jié)果如圖5所示。

通過仿真結(jié)果(圖5)可以看出,,與傳統(tǒng)鎖相環(huán)相比,,自適應(yīng)鎖相環(huán)能夠根據(jù)當(dāng)前環(huán)境自適應(yīng)對環(huán)路帶寬作出調(diào)整,對環(huán)境的適應(yīng)性更強(qiáng),。噪聲水平較低時(shí),,跟蹤速度是關(guān)鍵性能參數(shù)。在噪聲水平較低的情況下(對應(yīng)25 dB),,自適應(yīng)跟蹤具有更快的跟蹤速度,。噪聲水平較高時(shí),相位抖動是關(guān)鍵參數(shù),,結(jié)果顯示,,在噪聲水平較高的情況下,自適應(yīng)鎖相環(huán)具有較小的抖動,。

在此基礎(chǔ)上,,在多種信噪比環(huán)境下進(jìn)行實(shí)驗(yàn)。信噪比較大即噪聲水平較低時(shí),傳統(tǒng)鎖相環(huán)的自適應(yīng)跟蹤的跟蹤速度結(jié)果如表1所示,。信噪比較小即噪聲水平較高時(shí),,傳統(tǒng)鎖相環(huán)的自適應(yīng)跟蹤的跟蹤速度結(jié)果如表2所示。

上述結(jié)果顯示,,與傳統(tǒng)鎖相環(huán)相比,,自適應(yīng)鎖相環(huán)在噪聲水平較高時(shí),具有更快的跟蹤速度,,在噪聲水平較低時(shí),,最有更小的相位抖動,起到了根據(jù)環(huán)境作出自適應(yīng)調(diào)整的作用,。

系統(tǒng)設(shè)計(jì)中使用的FPGA是EP3CIOF256C8,。將調(diào)試好的程序下載到FPGA硬件板,通過QUARTUSⅡ軟件中自帶的SIGNALTAP工具對輸入和輸出信號進(jìn)行實(shí)時(shí)觀察,,結(jié)果顯示,,設(shè)計(jì)的自適應(yīng)鎖相環(huán)能夠進(jìn)行正確穩(wěn)定的跟蹤,正確解調(diào)出數(shù)據(jù)信號,。該模塊目前已應(yīng)用在基于數(shù)字中頻方案的擴(kuò)頻接收機(jī)中,。

6 結(jié)論

在傳統(tǒng)鎖相環(huán)的基礎(chǔ)上,引入自適應(yīng)參數(shù)調(diào)整模塊,,能夠根據(jù)鎖相環(huán)所處環(huán)境的噪聲情況,,自適應(yīng)地對環(huán)路帶寬進(jìn)行調(diào)整,由于調(diào)整過程中步長取值較小,,具有一定的連續(xù)性,,因此,調(diào)整過程中仍能正常進(jìn)行數(shù)據(jù)解調(diào),,不會引起突變,能夠有效地在噪聲性能和跟蹤速度間進(jìn)行平衡,。