RapidIO總線的出現(xiàn)及其體系結(jié)構(gòu)和應(yīng)用

傳統(tǒng)總線多采用并線總線的工作方式,這類總線一般分為三組:數(shù)據(jù)線,地址線和控制線。實(shí)現(xiàn)此類總線互連的器件所需引腳數(shù)較多,例如對于64位數(shù)據(jù)寬的總線,一般由64根數(shù)據(jù)線,32-40根地址線以及30根左右的控制線,另外由于半導(dǎo)體制造工藝的限制還要加上一定數(shù)量的電源引線和地線,總共會(huì)有約200根左右的引線,這給器件封裝、測試、焊接都帶來了一些問題,如果要將這種總線用于系統(tǒng)之間的通過背板的互連,由此帶來的困難就可想而知。并線總線的另一個(gè)問題是時(shí)鐘與信號的偏移容限的問題,對于這樣一組并行信號線的集合,信號的采樣是取決于時(shí)鐘信號的上升沿或是下降沿,這樣對于信號的跳變和時(shí)鐘的跳變時(shí)刻的時(shí)間差就有一個(gè)上限值,隨著速率的升高,布線長度、器件門電路自身的翻轉(zhuǎn)時(shí)間都會(huì)影響總線的速率。

用于處理器之間互連以及背板互連的另一個(gè)主要技術(shù)是以太網(wǎng),近些年來,以太網(wǎng)在存儲(chǔ)、電信、通訊、無線、工業(yè)應(yīng)用以及嵌入式應(yīng)用中得到大量的應(yīng)用,現(xiàn)有的成熟的硬件和協(xié)議棧降低了開發(fā)的復(fù)雜性和產(chǎn)品的開發(fā)成本。但是在局域網(wǎng)和廣域網(wǎng)中得到很好應(yīng)用的以太網(wǎng)用于這種芯片級或是板極的系統(tǒng)互連顯示出了低效率、高延時(shí)的特性,QOS需要高層軟件的參與,造成軟件模塊化結(jié)構(gòu)不清晰。尤其是當(dāng)背板的傳輸速率從1Gbps增加到10Gbps時(shí),增加的處理要求已經(jīng)超出了以太網(wǎng)的能力。

RapidIO技術(shù)最初是由Freescale和Mercury共同研發(fā)的一項(xiàng)互連技術(shù),其研發(fā)初衷是作為處理器的前端總線,用于處理器之間的互連,但在標(biāo)準(zhǔn)制定之初,其創(chuàng)建者就意識到了RapidIO還可以做為系統(tǒng)級互連的高效前端總線而使用。1999年完成第一個(gè)標(biāo)準(zhǔn)的制定,2003年5月,Mercury Computer Systems公司首次推出使用Rapid IO技術(shù)的多處理器系統(tǒng)ImpactRT 3100, 表明RapidIO已由一個(gè)標(biāo)準(zhǔn)制定階段進(jìn)展到產(chǎn)品階段,到目前為止,RapidIO已經(jīng)成為電信,通迅以及嵌入式系統(tǒng)內(nèi)的芯片與芯片之間,板與板之間的背板互連技術(shù)的生力軍。

RapidIO是針對嵌入式系統(tǒng)的獨(dú)特互連需求而提出的,那么我們首先來說明嵌入式系統(tǒng)互連的一些基本需求:嵌入式系統(tǒng)需要的是一種標(biāo)準(zhǔn)化的互連設(shè)計(jì),要滿足以下幾個(gè)基本的特點(diǎn):高效率、低系統(tǒng)成本,點(diǎn)對點(diǎn)或是點(diǎn)對多點(diǎn)的通信,支持DMA操作,支持消息傳遞模式交換數(shù)據(jù),支持分散處理和多主控系統(tǒng),支持多種拓樸結(jié)構(gòu);另外,高穩(wěn)定性和QOS也是選擇嵌入式系統(tǒng)總線的基本原則。而這些恰是RapidIO期望滿足的方向。所以RapidIO在制定之初即確定了以下幾個(gè)基本原則:一是輕量型的傳輸協(xié)議,使協(xié)議盡量簡單;二是對軟件的制約要少,層次結(jié)構(gòu)清晰;三是專注于機(jī)箱內(nèi)部芯片與芯片之間,板與板之間的互連。

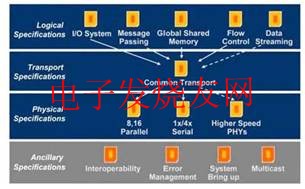

RapidIO采用三層分級的體系結(jié)構(gòu),分級結(jié)構(gòu)圖如下圖所示:

圖1:RapidIO三層分級體系結(jié)構(gòu)圖

由此圖可見,RapidIO協(xié)議由邏輯層、傳輸層和物理層構(gòu)成。最明顯的一個(gè)特點(diǎn)就是RapidIO采用了單一的公用傳輸層規(guī)范來相容、會(huì)聚不同的邏輯層和物理層,單一的邏輯層實(shí)體增強(qiáng)了RapidIO的適應(yīng)性。物理層定義了串行和并行兩個(gè)實(shí)體,得到廣泛應(yīng)用的只有串行方式,尤其是用在背板互連的場合,串行方式可以在兩個(gè)連接器之間允許80-100cm的連線,單鏈路傳輸帶寬可達(dá)10Gbps。目前RapidIO的標(biāo)準(zhǔn)是Version1.3,在未來的Version2.0規(guī)范中定義了更高的傳輸速率,可以得到更高的傳輸帶寬。

目前,RapidIO在無線基站系統(tǒng)中已經(jīng)得到了廣泛的應(yīng)用,同樣在視頻處理,語音處理,高性能計(jì)算機(jī)及存儲(chǔ)領(lǐng)域也會(huì)得到越來越多的應(yīng)用。在實(shí)現(xiàn)芯片到芯片之間、板與板之間的高速互連上,RapidIO所能帶來的好處也越來越直觀,對于簡化系統(tǒng)設(shè)計(jì)、高帶寬、低延時(shí)等特點(diǎn)也被開發(fā)人員廣泛接受。下一代的RapidIO在應(yīng)用上也要向機(jī)箱與機(jī)箱間的高速互連方向上發(fā)展,同時(shí)也會(huì)提供更高的傳輸速率,2.0規(guī)范中已經(jīng)可以實(shí)現(xiàn)40Gbps的帶寬。我們相信,隨著越來越多的處理器支持RapidIO接口,RapidIO的應(yīng)用前景會(huì)越來越光明

RapidIO信號完整性測試及其最必要的波形參數(shù)測試

眾所周知,當(dāng)今世界數(shù)字技術(shù)飛速發(fā)展,無論您是一位從事電信產(chǎn)品或是數(shù)據(jù)通信產(chǎn)品,PC,服務(wù)器及相關(guān)產(chǎn)品,高速半導(dǎo)體集成電路設(shè)計(jì),或是高速光電收發(fā)模塊,高速信號處理,高速互連器件(諸如高速接插件,高速數(shù)字傳輸電纜)等領(lǐng)域的研發(fā)及測試工程師都會(huì)面臨著一個(gè)共同的挑戰(zhàn)——Signal Integrity(SI)——信號完整性。

大概10年前我們所提到的數(shù)字產(chǎn)品,其時(shí)鐘或數(shù)據(jù)頻率大多在幾十兆之內(nèi),信號的上升時(shí)間大多在幾個(gè)納秒,甚至幾十納秒以上。那時(shí)的數(shù)字化產(chǎn)品設(shè)計(jì)工程師進(jìn)行的就是“數(shù)字設(shè)計(jì)”――只要掌握布爾代數(shù)等數(shù)字方面的諸多知識,保證邏輯正確,就能設(shè)計(jì)出其所期望的性能的產(chǎn)品。而現(xiàn)在的數(shù)字技術(shù)已經(jīng)發(fā)展到幾千兆,甚至幾十千兆的傳輸速率,信號的上升時(shí)間大多在一納秒以內(nèi),諸如串?dāng)_,阻抗匹配,EMI(電磁兼容),抖動(dòng)等射頻微波領(lǐng)域才會(huì)遇到的問題,如今變成了高速數(shù)字設(shè)計(jì)必須解決的關(guān)鍵性問題。這就要求我們的工程師不但要具備數(shù)字方面的設(shè)計(jì)知識,同時(shí)也要具備射頻微波方面的設(shè)計(jì)知識;不但要掌握時(shí)域及邏輯域的測量技術(shù),還要掌握頻域的測量技術(shù)。

高速數(shù)字設(shè)計(jì)與測試在歐美,日本等技術(shù)先進(jìn)國家近些年來已成為一個(gè)非常熱門的行業(yè),它是實(shí)現(xiàn)高性能數(shù)字化產(chǎn)品的基礎(chǔ),就如同一個(gè)城市的道路建設(shè),只有路修得好,車才能跑得既穩(wěn)又快。因此,國內(nèi)外很多大公司都相繼成立了高速數(shù)字設(shè)計(jì)與測試(信號完整性分析)的研發(fā)力量。

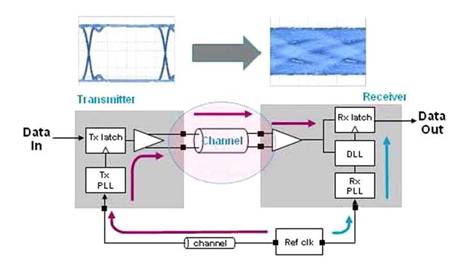

圖2:典型的高速互連系統(tǒng)

圖2是一個(gè)典型的高速互連系統(tǒng),包括:發(fā)送器,傳輸通道和接收器。針對這種高速互

連系統(tǒng)(如RapidIO互連系統(tǒng))的信號完整性測試分析,我們需要考慮三個(gè)方面:

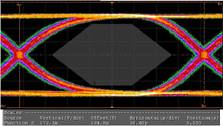

1、 信號波形參數(shù)測試分析:一般用示波器測試分析發(fā)送端的信號或接收端的信號,通

過眼圖/模板、抖動(dòng)等參數(shù)的測試分析決定是否滿足規(guī)范或設(shè)計(jì)要求。

2、 互連測試分析:這是從引發(fā)波形失真的源頭去測試,測試通道的差分阻抗,衰減等

參數(shù),分析是否會(huì)引發(fā)信號完整性問題。

3、 接收性能測試:只是信號波形好不能保證整個(gè)系統(tǒng)誤碼率一定很低,系統(tǒng)一定穩(wěn)定

和可靠,因?yàn)榻邮招阅艿暮脡囊彩菦Q定系統(tǒng)性能和穩(wěn)定性的一個(gè)關(guān)鍵方面。

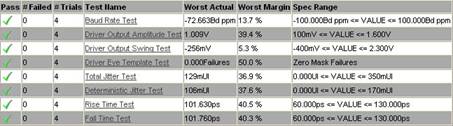

首先我們需要考慮的是信號波形參數(shù)測試分析部分。信號波形參數(shù)測試分析一方面檢測被測系統(tǒng)是否滿足規(guī)范或設(shè)計(jì)的要求,另一方面是幫助我們找到問題的根源。圖3是安捷倫信號波形參數(shù)分析解決方案。DSA90000A數(shù)字信號分析儀帶寬從2.5GHz到13GHz可選和帶寬可升級,采樣速率每通道高達(dá)40GSa/s,存儲(chǔ)深度最深每通道達(dá)1GB。DSO9000A帶寬從1GHz到4GHz可選和帶寬可升級,采用速率最高達(dá)20GSa/s,存儲(chǔ)深度最深達(dá)1GB(兩通道使用下每通道指標(biāo)),卓越的性能滿足RapidIO測試的要求。

注:測試3.125Gbps的RapidIO需要8GHz帶寬,測試2.5Gbps的RapidIO需要6GHz

帶寬,測試1.25GHz的RapidIO需要4GHz的帶寬。

圖3:安捷倫信號波形參數(shù)分析解決方案DSA90000A和DSO9000A

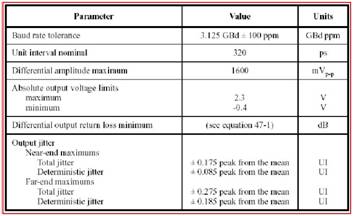

針對串行RapidIO,信號波形參數(shù)測試內(nèi)容如下(以3.125G為例):

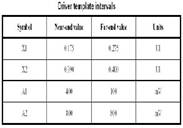

表1:串行RapidIO信號品質(zhì)測試規(guī)范(以3.125Gbps為例)

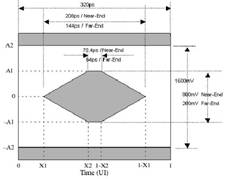

圖4:串行RapidIO模板定義

圖5:串行RapidIO測試結(jié)果示例(使用安捷倫基于示波器的自動(dòng)測試軟件)

RapidIO互連通道測試

物理層結(jié)構(gòu)正日益成為高速數(shù)字系統(tǒng)性能的瓶頸。在較低的信號速率時(shí),這些互連的電

長度很短,驅(qū)動(dòng)器和接收機(jī)一般是導(dǎo)致信號完整性問題的最主要因素。但隨著時(shí)鐘速率、總

線速率及鏈路速率突破每秒千兆大關(guān),物理層特性測試正變得日益關(guān)鍵。

時(shí)域分析一般用來描述這些物理層結(jié)構(gòu)的特征,但通常情況下,設(shè)計(jì)人員在測試時(shí)往往

只考慮器件工作在其被期望的工作模式上時(shí)的情況。為了獲得一個(gè)完整的時(shí)域信息,必須要

測試反射和傳輸(TDR和TDT)中的階躍和脈沖相應(yīng)。

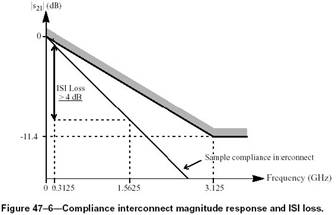

為了全面描述物理層結(jié)構(gòu)的特征,還必須進(jìn)行頻域分析。S參數(shù)模型說明了這些數(shù)字電

路結(jié)構(gòu)所展示出來的模擬特點(diǎn)包括:不連續(xù)點(diǎn)反射、頻率相關(guān)損耗、串?dāng)_和EMI等性能。

為使設(shè)備性能符合標(biāo)準(zhǔn),眼圖增加了重要的統(tǒng)計(jì)分析功能。為利用全面特性檢定技術(shù)改

善仿真能力,可以采用基于測試結(jié)果的S參數(shù)或RLCG模型提取技術(shù)。

隨著在多種工作模式下進(jìn)行數(shù)字和模擬綜合分析(時(shí)域和頻域)變得越來越重要,要完

成這些測試功能,通常需要使用多種測試儀表,同時(shí)操作多種儀表正變得越來越困難。物理

層測試系統(tǒng)PLTS是為了解決這種困難而設(shè)計(jì)的。它使用已獲專利的變換算法,自動(dòng)地在頻

域和時(shí)域里表示在所有可能的工作模式(單端、差分、共模和模式轉(zhuǎn)換)下所得到的前向和

后向、傳輸和反射的測試數(shù)據(jù)。強(qiáng)大的虛擬碼型發(fā)生器功能可以把用戶定義的二進(jìn)制序列應(yīng)

用到被測的數(shù)據(jù)上,形成仿真的眼圖。同時(shí),可以提取高精度的RLCG模型,用來提高建

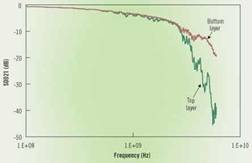

模的仿真的精度。圖6是RapidIO互連通道測試要求:

圖6:串行RapidIO互連通道損耗規(guī)范(以3.125Gbps為例)

圖7:串行RapidIO互連通道測試結(jié)果(使用Agilent物理層測試系統(tǒng))

安捷倫物理層測試方案功能

1、 高速互連的時(shí)域分析:可以得出16個(gè)單端時(shí)域參數(shù);可以得出16個(gè)混合模式(或差

分模式)時(shí)域參數(shù)。

2、 高速互連的頻域分析:可以得出16個(gè)單端頻域參數(shù);可以得出16個(gè)混合模式(或

差分模式)頻域參數(shù)。

3、 支持校準(zhǔn)引導(dǎo)和多種校準(zhǔn)模式,如:TRL,SOLT,夾具直通校準(zhǔn)方法等。

4、 基于測量結(jié)果的眼圖仿真:用戶定義虛擬碼型,進(jìn)行眼圖仿真。產(chǎn)生眼圖后,可以

用光標(biāo)或自動(dòng)進(jìn)行測量,如:模板,抖動(dòng),眼圖張開,上升時(shí)間和下降時(shí)間等。

5、 支持頻域S參數(shù)模型和時(shí)域RLGC模型提取,可以導(dǎo)到建模和仿真軟件中,進(jìn)行更

復(fù)雜的仿真分析。

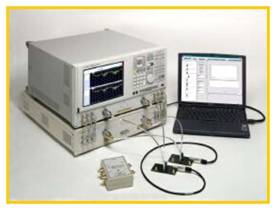

圖8:安捷倫物理層測試系統(tǒng)

RapidIO接收性能和誤碼率測試

接收性能測試往往被忽視。對于低速系統(tǒng),一般沒問題,但當(dāng)信號速率上升到了2.5Gbps

上后,規(guī)范對接收性能就有比較嚴(yán)格的要求。

一旦我們測試出了接收的性能或接收的模板,我們就可以知道我們的信號完整性設(shè)計(jì)應(yīng)

該設(shè)計(jì)到什么程度。比如,接收性能非常好,則信號波形較差,整個(gè)系統(tǒng)也仍然會(huì)穩(wěn)定和可

靠。

接收性能測試需要這樣一臺儀器:

1、 一臺高性能誤碼儀:能夠發(fā)抖動(dòng)非常小,波形非常好的信號;能夠接收信號和分析

誤碼率。

2、 能夠發(fā)帶抖動(dòng)的信號,并且抖動(dòng)是經(jīng)過校準(zhǔn)的,設(shè)置輸出多大抖動(dòng),實(shí)際就是多大

抖動(dòng),誤差較小。

3、 具備多種抖動(dòng)產(chǎn)生能力:正弦波抖動(dòng)SJ,周期性抖動(dòng)PJ,碼間干擾抖動(dòng)ISI,隨機(jī)

抖動(dòng)RJ,邊帶不相關(guān)抖動(dòng)BUJ等。

RapidIO抖動(dòng)容忍度的測試要求:

. pk-pk Receiver Jitter Tolerance =208ps (0.65UI)

. Jitter includes 3 components : Rj,Dj, Sinusoidal Jitter

. DJ tolerance shall be at least 118.4ps (0.37 UIp-p) .

. Tolerate an additional sinusoidal jitter with any frequency and amplitude

defined by the Far mask

圖9:RapidIO抖動(dòng)容忍度測試要求

安捷倫接收性能測試方案功能

安捷倫公司的N4903A/B J-BERT是典型的接收性能測試儀器。圖13是J-BERT總覽。

圖10:安捷倫接收性能測試方案J- BERT總覽

JBERT實(shí)現(xiàn)功能:

1、接收性能測試

2、誤碼率測量

3、快速眼圖和模板測試

4、碼型捕獲

5、抖動(dòng)容忍度測試

RapidIO協(xié)議層調(diào)試

RapidIO協(xié)議層分析和調(diào)試也是設(shè)計(jì)RapidIO系統(tǒng)時(shí)需要考慮的部分,尤其對于RapidIO

軟件設(shè)計(jì)者來說。RapidIO協(xié)議分析儀可以幫助我們完成RapidIO協(xié)議部分的測試和調(diào)試。

方案功能如下:

1、捕獲和分析串行RapidIO和PCI-Express協(xié)議

2、支持包頭識別和觸發(fā)

3、提供包級數(shù)據(jù)濾波

4、支持調(diào)試物理層,傳輸層和邏輯層

圖11:串行RapidIO和PCI-Express綜合協(xié)議分析儀

簡短小結(jié)

RapidIO互連技術(shù)已經(jīng)在各種無線通訊、雷達(dá)信號處理、高性能嵌入式處理等場合大量

使用,針對RapidIO設(shè)計(jì)的復(fù)雜性,安捷倫開發(fā)了全套的設(shè)計(jì)和測試解決方案:用ADS來

進(jìn)行系統(tǒng)的仿真和設(shè)計(jì),用示波器進(jìn)行波形參數(shù)的測試分析,用物理層測試系統(tǒng)進(jìn)行互連通

道的測試和分析,用抖動(dòng)誤碼儀進(jìn)行系統(tǒng)誤碼率和接收靈敏度的測試和分析,用協(xié)議分析儀

進(jìn)行協(xié)議層的分析和調(diào)試,以幫助研發(fā)工程師最快的開發(fā)RapidIO系統(tǒng)。