CAN總線是現(xiàn)場(chǎng)總線的一種,因?yàn)槠涑杀镜汀⑷蒎e(cuò)能力強(qiáng)、支持分布式控制、通信速率高等優(yōu)點(diǎn)在汽車、工業(yè)控制、航天等領(lǐng)域得到廣泛應(yīng)用。但是計(jì)算機(jī)沒有CAN總線接口,為了進(jìn)行CAN總線的調(diào)試,必須具有專用的適配卡才能實(shí)現(xiàn)與計(jì)算機(jī)的通信。目前常用的CAN轉(zhuǎn)換器是基于單片機(jī)設(shè)計(jì)的,一般只適用于單路CAN總線的數(shù)據(jù)轉(zhuǎn)換,可擴(kuò)展性差。

在小衛(wèi)星相機(jī)下位機(jī)系統(tǒng)中使用了多種總線,如CAN總線與衛(wèi)星管理計(jì)算機(jī)的通信;RS422(或RS485)總線與成像單元等下行單元的通信。在進(jìn)行相機(jī)下位機(jī)系統(tǒng)地面調(diào)試時(shí),可能需要多種總線轉(zhuǎn)換器。采用FPGA將不同總線協(xié)議轉(zhuǎn)換成USB2.0、RS232等可與計(jì)算機(jī)直接交換數(shù)據(jù)的協(xié)議,可增強(qiáng)設(shè)計(jì)的靈活性,降低設(shè)計(jì)的成本和復(fù)雜性,且可實(shí)現(xiàn)多路總線的數(shù)據(jù)通信接口。

這里以CAN總線通信接口為例,詳細(xì)論述了基于FPGA的CAN總線轉(zhuǎn)換USB接口的設(shè)計(jì)方案。

1 系統(tǒng)硬件組成

實(shí)現(xiàn)CAN總線與計(jì)算機(jī)雙向通信接口的核心是FPGA。它首先接收來(lái)自CAN總線的數(shù)據(jù),保存在FPGA內(nèi)部設(shè)計(jì)的FIF0緩存中,經(jīng)過(guò)內(nèi)部數(shù)據(jù)格式的轉(zhuǎn)換后,由USB控制器讀取并上傳給計(jì)算機(jī)。而總線數(shù)據(jù)注入過(guò)程的數(shù)據(jù)流向與之相反。FPCA選用Xilinx公司的Spartan3的XC3S200,系統(tǒng)硬件結(jié)構(gòu)如圖l所示。

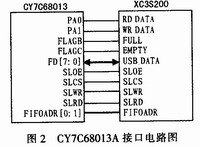

1.1 USB接口電路

USB是一種支持即插即用及熱插拔的串行總線,它具有傳輸速率高、連接靈活、使用方便等優(yōu)點(diǎn)。CYPRESS公司的EZ-USB芯片CY7C68013A支持USB2.0協(xié)議,通信可靠,傳輸速率可達(dá)480 Mb/s。CY7C68013A工作在SLAVE FIF0異步通信方式下,接口電路如圖2所示。

SLAVE FIFO異步寫周期中,高電平需維持70ns,低電平需維持50ns,理論最高傳輸速率為8Mb/s,而CAN總線的最高傳輸速率為1Mb/s,符合通信要求。端口PA0~PA1用作USB控制器端向FPGA發(fā)送讀寫命令的控制線,由USB固件程序配合上位機(jī)端自定義請(qǐng)求代碼產(chǎn)生PA端口的控制信號(hào)。另外使用了EEPROM芯片24LC128存放USB固件程序。

1.2 CAN總線接口電路

選用Philips公司的SJA1000作為CAN控制器,采用PCA82C250作為CAN收發(fā)器,并在CAN控制器與收發(fā)器之間使用6N137進(jìn)行光電隔離,以增強(qiáng)抗干擾能力。將MODE引腳接高電平即SJA1000工作在INTEL模式,![]() 引腳與復(fù)位芯片MAX706T的RESET引腳相連,進(jìn)行全局復(fù)位。在FPGA與SJA1000連接時(shí)需要使用741V164245電平轉(zhuǎn)換器完成CAN總線5 V TTL電平向3.3 V FPGA I/O電平的轉(zhuǎn)換。另外,SJA1000的RX1引腳與PCA-82C 250的VREF引腳相連,使用輸入比較器旁路功能,可減少內(nèi)部延時(shí),增加正常通信的總線長(zhǎng)度。具體的接口電路如圖3所示。

引腳與復(fù)位芯片MAX706T的RESET引腳相連,進(jìn)行全局復(fù)位。在FPGA與SJA1000連接時(shí)需要使用741V164245電平轉(zhuǎn)換器完成CAN總線5 V TTL電平向3.3 V FPGA I/O電平的轉(zhuǎn)換。另外,SJA1000的RX1引腳與PCA-82C 250的VREF引腳相連,使用輸入比較器旁路功能,可減少內(nèi)部延時(shí),增加正常通信的總線長(zhǎng)度。具體的接口電路如圖3所示。

2 FPGA邏輯控制程序

2.1 SJA1000邏輯控制

由于SJA1000地址線與數(shù)據(jù)總線復(fù)用,F(xiàn)PGA不僅僅要產(chǎn)生SJA1000讀寫控制引腳的信號(hào)邏輯,還需要模擬單片機(jī)等處理器產(chǎn)生對(duì)SJA1000的尋址信號(hào),實(shí)際上是一個(gè)向SJA1000寫地址的過(guò)程。根據(jù)SJA1000技術(shù)手冊(cè)的時(shí)序要求,要完成對(duì)SJA1000內(nèi)寄存器的正確讀寫,接口邏輯必須在地址鎖存信號(hào)ALE為高電平時(shí)將SJA1000的寄存器地址當(dāng)作數(shù)據(jù)寫入,然后在ALE和片選信號(hào)![]() 為低電平后使能SJA1000的讀寫控制信號(hào)(WR或RD)。SJA1000的邏輯控制采用狀態(tài)機(jī)的方式完成,狀態(tài)機(jī)流程圖如圖4所示。起始態(tài)為IDLE態(tài),當(dāng)接收到數(shù)據(jù)讀寫等命令時(shí),進(jìn)入ADDR-ESS態(tài),向SJA1000寫入相應(yīng)寄存器的地址值。然后根據(jù)命令類型決定下一個(gè)態(tài)是寫寄存器狀態(tài)(WR1~WR3)還是讀寄存器狀態(tài)(RD1~RD4)。以寫寄存器為例,在WR1態(tài)ALE、

為低電平后使能SJA1000的讀寫控制信號(hào)(WR或RD)。SJA1000的邏輯控制采用狀態(tài)機(jī)的方式完成,狀態(tài)機(jī)流程圖如圖4所示。起始態(tài)為IDLE態(tài),當(dāng)接收到數(shù)據(jù)讀寫等命令時(shí),進(jìn)入ADDR-ESS態(tài),向SJA1000寫入相應(yīng)寄存器的地址值。然后根據(jù)命令類型決定下一個(gè)態(tài)是寫寄存器狀態(tài)(WR1~WR3)還是讀寄存器狀態(tài)(RD1~RD4)。以寫寄存器為例,在WR1態(tài)ALE、![]() 、

、![]() 等信號(hào)置為非有效態(tài)。將

等信號(hào)置為非有效態(tài)。將![]() 置為有效狀態(tài);在WR2態(tài)ALE、

置為有效狀態(tài);在WR2態(tài)ALE、![]() 為非有效態(tài).而將

為非有效態(tài).而將![]() 信號(hào)置為有效態(tài),在時(shí)鐘的下降沿將數(shù)據(jù)寫入寄存器。WR3狀態(tài)保持

信號(hào)置為有效態(tài),在時(shí)鐘的下降沿將數(shù)據(jù)寫入寄存器。WR3狀態(tài)保持![]() 有效,WR信號(hào)變?yōu)闊o(wú)效,進(jìn)入IDLE態(tài),一次寫周期完成。

有效,WR信號(hào)變?yōu)闊o(wú)效,進(jìn)入IDLE態(tài),一次寫周期完成。

2.2 SJA1000讀寫數(shù)據(jù)流程控制

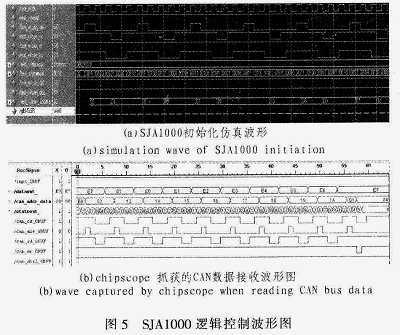

FPGA對(duì)SJA1000控制程序包括SJA1000初始化、SJA1000讀數(shù)據(jù)、SJA1000寫數(shù)據(jù)等部分。SJA1000的初始化是在復(fù)位模式下進(jìn)行的,在復(fù)位模式下分別設(shè)置時(shí)鐘分頻器CDR、總線定時(shí)器(BTR0、BTR1)、輸出控制寄存器(OCR)等重要寄存器。SJA1000通信波特率由總線定時(shí)器決定,需要與后端節(jié)點(diǎn)的波特率相同才能進(jìn)行節(jié)點(diǎn)間的正常通信。FPGA上電后需要延時(shí)一段時(shí)間.等待SJA1000復(fù)位完成才能進(jìn)行SJA1000初始化。初始化仿真波形如圖5(a)所示。SJA1000內(nèi)部有一個(gè)接收緩沖器和一個(gè)發(fā)送緩沖器。FPGA對(duì)SJA1000的讀寫操作,實(shí)際上對(duì)這兩個(gè)緩沖器的讀寫控制。當(dāng)FPGA接收CAN總線數(shù)據(jù)時(shí)首先讀取SJA1000中斷寄存器IR判斷是否有接收中斷。如果有接收中斷到來(lái)則開始讀取緩沖器內(nèi)的8字節(jié)數(shù)據(jù),然后釋放接收緩沖器(寫命令寄存器CMR)。使用Xilinx公司的Chipseope軟件進(jìn)行板上測(cè)試,測(cè)試數(shù)據(jù)為(E0,E1,……E7),抓取到的波形如圖5(b)所示。FPGA讀寫SJA1000的流程控制圖如圖6所示。

2.3 CY7C68013A通信控制程序

CY7C68013A提供一種量子FIFO的處理架構(gòu),使USB接口和應(yīng)用環(huán)境直接共享內(nèi)部含有的4 K FIF0空間。本文CY7C68013A的控制是以異步SLAVE FIFO方式實(shí)現(xiàn)的,F(xiàn)PGA對(duì)CY7C68013A的邏輯控制實(shí)際上是對(duì)CY7C68013A內(nèi)部FIFO的異步讀寫控制。設(shè)置CY7C68013A端點(diǎn)2為批量輸入端點(diǎn)(FIF0地址為00),端點(diǎn)6為批量輸出端點(diǎn)(FIF0地址為1O)。FPGA判斷CY7C68013A的PA[1:0]端口電平,當(dāng)PA[1:0]為01時(shí),F(xiàn)PGA將接收到的CAN總線數(shù)據(jù)寫入端點(diǎn)2對(duì)應(yīng)的FIF0空間并上傳給上位機(jī),PA[1:0]為10時(shí),F(xiàn)PGA讀取端點(diǎn)6對(duì)應(yīng)的FIFO內(nèi)數(shù)據(jù)。FPGA對(duì)CY7C68013A的時(shí)序控制嚴(yán)格按照芯片手冊(cè)完成。

由于USB數(shù)據(jù)包與CAN數(shù)據(jù)幀是基于兩種不同協(xié)議的數(shù)據(jù)格式,因此在FPGA內(nèi)開辟了2個(gè)512x8bit的FIFO緩存,并要進(jìn)行必要的格式轉(zhuǎn)換。例如,當(dāng)從USB總線端注入的數(shù)據(jù)大于8字節(jié)時(shí),需要將數(shù)據(jù)分成多幀傳送給CAN總線;當(dāng)數(shù)據(jù)小于8字節(jié)時(shí)則在數(shù)據(jù)后填充0。另外,在數(shù)據(jù)傳送給CAN總線之前還需要添加適當(dāng)?shù)膸畔⑴c幀識(shí)別碼。

3 軟件設(shè)計(jì)

3.1 USB固件程序

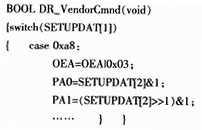

USB固件程序是在Keil工具上開發(fā)完成的,除了進(jìn)行必要的端點(diǎn)及寄存器配置外,程序中使用了自定義請(qǐng)求命令。自定義請(qǐng)求碼通過(guò)USB控制傳輸?shù)姆绞絺魉徒o固件,固件程序需要響應(yīng)自定義請(qǐng)求碼的請(qǐng)求信息。本文使用的自定義請(qǐng)求碼為Oxa8,在響應(yīng)代碼中設(shè)置端口PA[1:0]電平值,產(chǎn)生USB控制命令,代碼如下所示。SETUPDAT[2]對(duì)應(yīng)控制傳輸端點(diǎn)的Value值,由上位機(jī)應(yīng)用程序設(shè)定。

3.2 USB驅(qū)動(dòng)程序及應(yīng)用程序

使用CYPRESS公司提供的CY7C68013A通用驅(qū)動(dòng)程序CyUSB.sys。上位機(jī)應(yīng)用程序使用VC編寫,也是基于Cypress提供的C++類庫(kù)文件CyAP-I.lib設(shè)計(jì)完成的。使用的主要函數(shù)包括:BeginDataXfer、FinishDataXfer、XferData等函數(shù)。應(yīng)用程序中設(shè)計(jì)了獨(dú)立的數(shù)據(jù)接收線程,線程函數(shù)中不斷地發(fā)送USB數(shù)據(jù)讀命令,并完成批量輸人端點(diǎn)的讀操作。當(dāng)有數(shù)據(jù)讀入時(shí),與主線程之間采用事件的線程同步方式,將數(shù)據(jù)讀入計(jì)算機(jī)內(nèi)存并保存。以下是線程函數(shù)中用于發(fā)送USB控制命令的控制傳輸代碼:

4 實(shí)驗(yàn)調(diào)試與結(jié)果

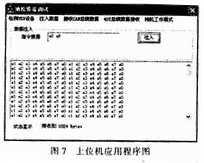

為驗(yàn)證設(shè)計(jì)的正確性,使用了周立功公司的USBCAN-I產(chǎn)品,與目標(biāo)電路板組成雙節(jié)點(diǎn)通信,2個(gè)節(jié)點(diǎn)設(shè)置相同波特率500 Kb/s(BTRO= 00,BTR1=1Ch)和相同幀格式,由測(cè)試軟件ZLGCANTest發(fā)送一組數(shù)據(jù)(eOh,e1h,……,e7h),上位機(jī)應(yīng)用程序接收到的數(shù)據(jù)如圖7所示。反過(guò)來(lái)由上位機(jī)應(yīng)用程序注入指令數(shù)據(jù)e0h,a8h,周立功軟件接收到的數(shù)據(jù)為e0h,a8h,00h,OOh……。經(jīng)實(shí)驗(yàn)表明,數(shù)據(jù)收發(fā)正確,近距離通信時(shí),通信速率可高達(dá)1 Mb/s。

5 結(jié)論

使用該方法設(shè)計(jì)的CAN總線轉(zhuǎn)換器優(yōu)點(diǎn)在于:使用USB總線完成CAN總線與計(jì)算機(jī)的數(shù)據(jù)交換,不會(huì)影響CAN總線的整體通信速率;通過(guò)FPGA控制完成通信接口的設(shè)計(jì),可擴(kuò)展性好,靈活性強(qiáng),穩(wěn)定性高。作為空間相機(jī)下位機(jī)地檢設(shè)備的一部分,F(xiàn)PGA同時(shí)還可以完成RS422等總線的通信控制。