隨著雷達(dá)技術(shù)的發(fā)展,出現(xiàn)了多種體制的雷達(dá),比如脈沖多普勒雷達(dá)、SAR、相控陣?yán)走_(dá)先進(jìn),雖然這些雷達(dá)的功能不同,但是為了提作用距離和距離向上的分辨率,都彩了大時(shí)寬積信號。

在雷達(dá)信號源設(shè)計(jì)領(lǐng)域,DDS技術(shù)和器件已經(jīng)得到了很大的發(fā)展,相應(yīng)的出現(xiàn)了很多性能優(yōu)異的DDS器件,本文旨在介紹一種基于ADI公司的AD9959設(shè)計(jì)的新型多體制的雷達(dá)信號源設(shè)計(jì)方法,該器件具有穩(wěn)定度高,相位、頻率和幅度調(diào)整靈活,能夠同時(shí)產(chǎn)生4路相關(guān)信號,信號形式可以任意設(shè)定的特點(diǎn),這些優(yōu)異的性能在雷達(dá)信號源的研制方面都表現(xiàn)出了良好的應(yīng)用前景。

2 系統(tǒng)硬件設(shè)計(jì)

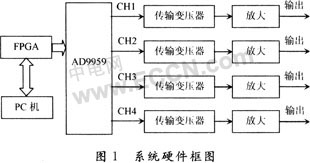

本文設(shè)計(jì)的多體制雷達(dá)信號源是以ADI公司的AD9959為核心,結(jié)合FPGA控制電路、信號放大電路構(gòu)成的。信號參數(shù)由主控計(jì)算機(jī)通過串口進(jìn)行發(fā)送,并同F(xiàn)PGA進(jìn)行接收,從而控制AD9959完成相應(yīng)的信號輸出。由于在雷達(dá)的實(shí)際發(fā)射過程中,大部分采用的是大時(shí)寬帶寬的脈沖信號,因此在系統(tǒng)硬件設(shè)計(jì)的架構(gòu)中,F(xiàn)PGA還完成了一定的脈沖輸出功能,對AD9959輸出的連續(xù)波信號進(jìn)行脈沖調(diào)制,從而達(dá)到輸出雷達(dá)脈沖信號的能力,而輸出的中頻信號經(jīng)過混頻電路就可以達(dá)到雷達(dá)發(fā)射所需要的頻段。

2.1 AD9959芯片簡介

AD9959是一款性能優(yōu)異的DDS芯片,主要體現(xiàn)在以下幾個(gè)方面:

4路同步輸出通道;

各個(gè)通道有獨(dú)立的頻率/相位/幅度控制功能;

超強(qiáng)的通道之間隔離度(>65 dB);

線性頻率/相位/幅度掃描能力;

能夠達(dá)到16級的頻率/相位/幅度調(diào)制能力;

可通過硬件/軟件控制節(jié)電模式。

AD9959通過串行I/O提供了多種配置功能,基于這種串行I/O提供的一種SPI模式,同以往的ADI的DDS器件是兼容的。同時(shí),器件采用先進(jìn)的設(shè)計(jì)技術(shù),使器件不僅具有優(yōu)異的性能,而且又具有低功耗的特點(diǎn)。器件集成了具有突出的寬帶和窄帶SFDR特性的4路高速10位DACs。每一個(gè)通道,都具有32位頻率控制字,14位相位控制字,10位輸出幅度控制字。REF CLK最高可以達(dá)到500 M/s,PLL倍頻器可以通過軟件編程在4~20之間設(shè)定。正因?yàn)锳D9959具有能夠輸出多通道相關(guān)信號的能力,所以AD9959可以廣泛地應(yīng)用于各種場合。

2.2 系統(tǒng)構(gòu)成

用戶通過計(jì)算機(jī)將所產(chǎn)生信號的參數(shù)傳送給FPGA,F(xiàn)PGA接收到相應(yīng)的參數(shù)后,控制AD9959輸出相應(yīng)的雷達(dá)信號,由于AD9959輸出信號是差分電流信號,因此在系統(tǒng)設(shè)計(jì)時(shí),采用1:1傳輸變壓器將差分的電流信號轉(zhuǎn)化為單端的電壓信號,同時(shí)為了提高系統(tǒng)的輸出驅(qū)動能力,在變壓器后面進(jìn)行了信號放大,系統(tǒng)框圖如圖1所示。

2.3 系統(tǒng)通信接口及協(xié)議

系統(tǒng)主要是由FPGA向AD9959發(fā)送命令,從而輸出相應(yīng)的信號,對于AD9959的控制主要是通過串行總線SCLK和SDIO來實(shí)現(xiàn)的,其中SCLK的最大時(shí)鐘速度可以達(dá)到200 MHz,AD9959可以通過SDIO的4根數(shù)據(jù)線(SDIO 0~SDIO 3)同時(shí)進(jìn)行數(shù)據(jù)傳輸,從而可以使數(shù)據(jù)吞吐量變?yōu)?00 Mb/s,以前ADI公司的DDS產(chǎn)品有并行和串行兩種控制模式,比如AD9850,而AD9959這種SPI控制模式,無疑是更加簡潔,對于用戶控制而言也更加方便。AD9959有4種串行控制傳輸模式,分別是Single-Bit Serial(2 and 3-wire)Modes,2-Bit Serial Mode,4-Bit SerialMode。AD9959四個(gè)輸出通道共享寄存器0x03~0x18,這種寄存器地址共享模式,能夠使4個(gè)通道同時(shí)寫入控制字。例如要使AD9959的4個(gè)通道都輸出某個(gè)頻率,只需要通過串行總線向AD9959寫入一次即可。如果使4個(gè)通道互相獨(dú)立操作,可以通過通道選擇寄存器(CSR)進(jìn)行選擇。

AD9959的串行工作模式都工作于寄存器級傳輸,而不是字節(jié)級傳輸。但是AD9959提供的SYNC I/O功能可以中斷I/O操作,這種模式可以使寄存器的某個(gè)字節(jié)進(jìn)行設(shè)置,從而減少了設(shè)置時(shí)間。所有指令都是在SCLK的上升沿寫入,而在SCLK的下降沿讀出的。在本文所設(shè)計(jì)的雷達(dá)信號源中,對于AD9959的控制模式采用了Single--Bit Serial 2-wire Mode,在這種工作模式下,AD9959使用SDIO 0作為數(shù)據(jù)傳輸管腳,要使AD9959工作于這種模式,可以將CSR寄存器中的CSR<2:1>設(shè)置為00即可。在Single-Bit Serial 2-wire Mode傳輸模式下,支持MSB優(yōu)先和LSB優(yōu)先兩種模式。

系統(tǒng)通過FPGA對AD9959進(jìn)行操作,主要分為兩個(gè)階段,第一個(gè)階段為指令周期,在這個(gè)階段把指令寫入到AD9959中,在SCLK的每個(gè)上升沿寫入一個(gè)比特,并且這個(gè)指令字節(jié)規(guī)定了將要進(jìn)行的傳輸?shù)降资亲x操作還是寫操作,同時(shí)包含了寄存器地址;第二個(gè)階段為數(shù)據(jù)傳送周期,主要傳送波形參數(shù)的控制字。

圖中完成的時(shí)序邏輯控制主要由FPGA來實(shí)現(xiàn),具體的信號參數(shù)是通過上位機(jī)通過串口發(fā)送給FPGA,因此FPGA還完成了串口收發(fā)功能,通過串口,系統(tǒng)主控制器(FPGA)不僅可以完成對上位機(jī)命令參數(shù)的接收,將信號各項(xiàng)參數(shù)寫入到AD9959中,同時(shí)還可以將AD9959內(nèi)部狀態(tài)信息讀出并且通過串口上傳到計(jì)算機(jī)。

3 系統(tǒng)軟件設(shè)計(jì)

3.1 FPGA程序設(shè)計(jì)

在本文所設(shè)計(jì)的雷達(dá)信號源中,采用了XINUNXSpartan-3系列FPGA,型號為XC23S1000,他具有106個(gè)邏輯門,Distributed RAM共120 kb,Block RAM共432 kb,還具有4個(gè)DCM單元,最大可用I/O391個(gè)。由于系統(tǒng)采用FPGA作為核心控制器件,因此具有很好的擴(kuò)展性,當(dāng)對系統(tǒng)的參數(shù)發(fā)生改變時(shí),只需要對FPGA內(nèi)部程序加以修改即可。而不用進(jìn)行硬件的改動,正因?yàn)镕P-GA具有這樣的優(yōu)勢,因此使本系統(tǒng)具有很好的靈活性。

通過對FPGA編程,主要完成了對AD9959控制功能和串口收發(fā)功能。AD9959內(nèi)部集成了4個(gè)DDS內(nèi)核,每個(gè)DDS內(nèi)核都集成了32-b的相位累加器和相位一幅度轉(zhuǎn)換器。每路DDS輸出的信號頻率可以通過下式來計(jì)算:

![]()

其中,fs表示系統(tǒng)采樣時(shí)鐘,F(xiàn)TW表示頻率控制字,fo表示DDS輸出信號頻率。由于在雷達(dá)信號源中,線性調(diào)頻信號是常用的信號形式,因此這里主要以線形調(diào)頻信號作參考。FPGA可以向AD9959發(fā)送控制字,從而可以控制輸出信號的起始頻率、調(diào)頻斜率系數(shù)、截止頻率等。FPGA控制AD9959寫入指令的時(shí)序邏輯圖如圖2所示。

FPGA在系統(tǒng)中不僅完成了控制AD9959的功能,同時(shí)還完成符合RS232協(xié)議的串口數(shù)據(jù)的傳送功能,UART功能都采用Verilog HDL語言描述,這樣使系統(tǒng)更加緊湊、小巧。

3.2 PC機(jī)程序設(shè)計(jì)

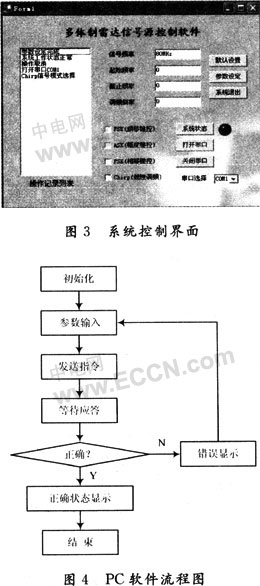

PC機(jī)軟件主要完成用戶參數(shù)的輸入并且將數(shù)據(jù)通過RS232串口發(fā)送到FPGA,程序采用C編寫,界面上可以輸入生成雷達(dá)信號的各種參數(shù),比如信號頻率、起始頻率、截止頻率、調(diào)頻斜率,由于AD9959可以生成FSK,PSK,ASK多種體制信號,用戶還可通過下拉列表選擇信號樣式。系統(tǒng)控制軟件界百如圖3所示。

軟件中利Visual Studio.NET中提供的串行通信控件Activex來實(shí)現(xiàn)串行數(shù)據(jù)通信功能,軟件的程序流程如圖4所示。

4 結(jié) 語

系統(tǒng)采用FPGA作為核心控制器,不僅完成了對AD9959的控制功能,同時(shí)還完成了串行數(shù)據(jù)傳輸功能,使電路設(shè)計(jì)更加簡潔并具有很好的擴(kuò)展性,在系統(tǒng)升級過程中,不必改動硬件設(shè)計(jì),只需要將FPGA內(nèi)部程序進(jìn)行修改即可完成新的功能。

本文所設(shè)計(jì)的雷達(dá)信號源已經(jīng)在實(shí)際工作中得到很好的應(yīng)用,系統(tǒng)可以同時(shí)輸出4路相參的信號,頻率范圍為10~150 MHz,每路輸出可以單獨(dú)控制也可以整體控制,用戶可以通過PC機(jī)對系統(tǒng)輸出的信號參數(shù)、樣式進(jìn)行沒定,從而可以很方便地輸出相應(yīng)的雷達(dá)信號。系統(tǒng)具有很強(qiáng)的實(shí)用性、靈活性和可擴(kuò)展性,在實(shí)際工作中取得了很好的效果,具有良好的應(yīng)用前景。