摘 要: 介紹了3DES" title="3DES">3DES加密算法的原理并詳盡描述了該算法的FPGA設計實現(xiàn)。采用了狀態(tài)機和流水線技術(shù)" title="狀態(tài)機和流水線技術(shù)">狀態(tài)機和流水線技術(shù),使得在面積和速度上達到最佳優(yōu)化;添加了輸入和輸出接口" title="輸出接口">輸出接口的設計以增強該算法應用的靈活性。各模塊均用硬件描述語言" title="硬件描述語言">硬件描述語言實現(xiàn),最終下載到FPGA芯片Stratix EP1S25F780C5中。

關(guān)鍵詞: 狀態(tài)機 流水線 3DES FPGA

隨著網(wǎng)絡的快速發(fā)展,信息安全越來越引起人們的關(guān)注。加密技術(shù)作為信息安全的利器,正發(fā)揮著重大的作用。通過在硬件設備(如路由器、交換機等)中添加解密功能,可使存儲和傳輸?shù)臄?shù)據(jù)具有較高的安全性。傳統(tǒng)的加密工作是通過在主機上運行加密軟件實現(xiàn)的。這種方法除占用主機資源外,其運算速度較硬件加密" title="硬件加密">硬件加密要慢,密鑰以明文的方式存儲在程序中,或者以加密的方式存儲在文件或數(shù)據(jù)庫中,重要數(shù)據(jù)(如個人密碼PIN等)會在某一時刻以明文形式出現(xiàn)在計算機的內(nèi)存或磁盤中,安全性較差。而硬件加密是通過獨立于主機系統(tǒng)外的硬件加密設備實現(xiàn)的,所有關(guān)鍵數(shù)據(jù)的存儲、運算都通過硬件實現(xiàn),不占主機資源、速度快、安全性較高。

盡管DES已被證實是不安全的算法(主要是密鑰太短),但三重DES增加了密鑰長度,由56位增加到112或168位,有更高的安全性,而且在新一代因特網(wǎng)安全標準IPSEC協(xié)議集中已將DES作為加密標準。另一方面,基于DES算法的加/解密硬件目前已廣泛應用于國內(nèi)外衛(wèi)星通信、網(wǎng)關(guān)服務器、機頂盒、視頻傳輸以及其它大量的數(shù)據(jù)傳輸業(yè)務中。利用3DES可以使原系統(tǒng)不作大的改動。所以對3DES的研究仍有很大的現(xiàn)實意義。

1 3DES加密算法描述

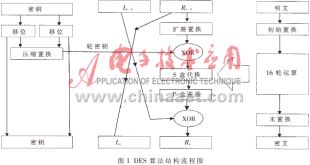

DES成為一個世界范圍內(nèi)的標準已經(jīng)20多年了,很好地抗住了多年的密碼分析,除最強有力的可能敵手外,對其它的攻擊仍是安全的。DES對64位的明文分組進行操作,通過一個初始置換,將明文分成左半部分和右半部分,然后進行16輪完全相同的運算,最后經(jīng)過一個末置換便得到64位密文。每一輪的運算包含擴展置換、S盒代換、P盒置換和兩次異或運算,另外每一輪中還有一個輪密鑰(子密鑰)。整體框圖如圖1所示。

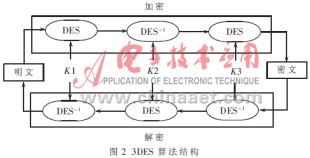

3DES(即Triple DES)是DES向AES過渡的加密算法(1999年,NIST將3-DES指定為過渡的加密標準),是DES的一個更安全的變形。它以 DES為基本模塊,通過組合分組方法設計出分組加密算法。其具體實現(xiàn)如下:設Ek()和Dk()代表DES算法的加密和解密過程,K代表DES算法使用的密鑰,P代表明文,C代表密文。這樣,

3DES加密過程為:C=Ek3(Dk2(Ekl(P)))

3DES解密過程為:P=Dkl(Ek2(DK3(C)))

具體的加/解密過程如圖2所示。K1、K2、K3決定了算法的安全性,若三個密鑰互不相同,本質(zhì)上就相當于用一個長為168位的密鑰進行加密。多年來,它在對付強力攻擊時是比較安全的。若數(shù)據(jù)對安全性要求不那么高,K1可以等于K3。在這種情況下,密鑰的有效長度為112位。

2 FPGA設計實現(xiàn)

2.1 FPGA設計的優(yōu)勢

用硬件實現(xiàn)某種密碼算法,首先要用硬件描述語言(如VHDL、Verilog HDL)進行系統(tǒng)設計和編碼,然后采用專用集成電路(ASIC)或現(xiàn)場可編程邏輯門陣列(FPGA)來具體實現(xiàn)。采用ASIC方法設計周期較長,且費用也較昂貴;而采用FPGA,可由設計者自己對芯片內(nèi)部單元進行配置,設計比較靈活,只需改變配置就可實現(xiàn)完全不同的功能,大大縮短了設計周期和開發(fā)時間,節(jié)省人力物力,同時經(jīng)過優(yōu)化可以達到較高的性能。另外,有多種EDA開發(fā)軟件支持FPGA的設計,在本設計中作者采用了ALTERA公司的QuartusⅡ開發(fā)軟件。

2.2 狀態(tài)機和流水線技術(shù)的應用

面積和速度這兩個指標貫穿著FPGA設計的始終,是設計質(zhì)量評價的終極標準。設計目標就是在滿足給定的時序要求(包含對設計頻率的要求)的前提下,占用較小的芯片面積;或者在所規(guī)定的面積下,使設計時序余量更大,頻率更高。通過功能模塊復用可減少設計消耗的芯片面積;反之,并行復制多個操作模塊可較大地提高設計頻率。在本設計中充分考慮了這一對矛盾體,采用狀態(tài)機和流水線相結(jié)合的技術(shù),使得在減少芯片資源消耗的情況下又能提高設計頻率。

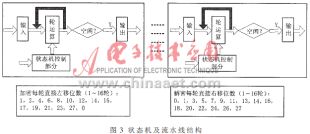

狀態(tài)機是組合邏輯和寄存器邏輯的特殊組合,尤其適合于數(shù)字系統(tǒng)的控制設計。系統(tǒng)的狀態(tài)在一定的條件下相互轉(zhuǎn)移。分析DES的算法結(jié)構(gòu)可以發(fā)現(xiàn),輪運算是相同的,只是輸入子密鑰不同,同時各輪的子密鑰都可以通過密鑰移位再經(jīng)過一個壓縮置換操作直接得到,所以將輪運算作為一個共享模塊,反復進行該操作,其輸入?yún)?shù)由狀態(tài)機控制部分提供,主要是密鑰移位的位數(shù)。只在空閑狀態(tài)下將輪運算結(jié)果輸出。因數(shù)據(jù)端是16位,故每個狀態(tài)機模塊中進行四輪輪運算。

流水線處理是高速設計中的一個常用設計手段。如果某個設計的處理流程可分為若干步驟,而且整個數(shù)據(jù)處理是“單流向”的,即沒有反饋,前一個步驟的輸出是下一個步驟的輸入,則可以考慮用流水線設計方法提高系統(tǒng)的工作頻率。流水線設計是一種技巧,它在很長組合路徑的中間點引入寄存器。寄存器會增加等待時間,但卻能增加速度,減少邏輯級。此外,附加寄存器雖然會增加一定的功耗,但卻極大地減少了毛刺。流水線處理方式之所以頻率較高,是因為復制了處理模塊,它是FPGA設計中面積換取速度思想的具體體現(xiàn)。DES的16輪運算結(jié)構(gòu)是相同的,符合流水線設計的要求,所以基于DES的結(jié)構(gòu)特點,將前面的狀態(tài)機模塊作為流水線的一個單元,這樣DES共有四個單元,串聯(lián)起來形成四級流水線。因狀態(tài)機中有寄存器,能保證流水線的工作,所以各單元間不需再加寄存器。狀態(tài)機及流水線結(jié)構(gòu)如圖3所示,圖中給出了由密鑰直接生成各子密鑰的移位數(shù)。將DES模塊復制三份,就形成了16級流水線,所不同的是流水線內(nèi)部是狀態(tài)機結(jié)構(gòu),所以每四個時鐘周期才會得到一組加/解密結(jié)果。這種結(jié)構(gòu)同樣適用于數(shù)據(jù)端是8位和32位的。

2.3 S盒的設計和接口設計

在3DES算法中,S盒代替是算法的關(guān)鍵所在。其它的運算都是線性的,易于分析和實現(xiàn),而S盒是非線性的,因此S盒的設計和優(yōu)化將直接影響整個系統(tǒng)的性能。DES的8個S盒都是6輸入、4輸出的結(jié)構(gòu),適合于用ROM來實現(xiàn),因此用VHDL定義如下結(jié)構(gòu)設計的ROM:

input : in std_logic_vector(5 downto 0);

output : out std_logic_vector(3 downto 0);

subtype s_word is std_logic_vector(3 downto 0);

subtype s1_rangeij is integer range 0 to 63;

type s_type is array(s1_rangeij) of s_word;

constant s:s_type:=( (“1110”),(“0100”),(“1101”),(“0001”)……);

function logic2int(din:std_logic_vector(5 downto 0)) return s1_rangeij --二進制轉(zhuǎn)換為十進制

output<=s(logic2int(input));

經(jīng)綜合后,每個S盒只用了24個邏輯單元。

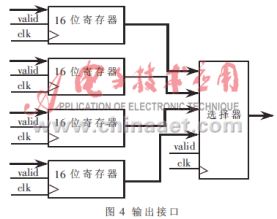

3DES是64位分組大小的加密算法,數(shù)據(jù)線一般是8位、16位或32位,為此增加了輸入、輸出接口,這部分接口完成的功能就是串/并轉(zhuǎn)換和并/串轉(zhuǎn)換。以16位輸出接口為例,設計中將加/解密出來的數(shù)據(jù)從低位到高位在valid信號有效的情況下同時存入四個16位寄存器,再通過一個選擇器依次將數(shù)據(jù)送出。該選擇器不同于普通的多路選擇器,它是由valid信號觸發(fā)其內(nèi)的計數(shù)功能,從而依次將寄存器中數(shù)據(jù)輸出,如圖4所示。輸入接口要簡單一些,只需一個64位可移位的寄存器,在第四個16位數(shù)據(jù)到來后才將這一組64位數(shù)據(jù)送給加密模塊。這種結(jié)構(gòu)非常容易用硬件描述語言實現(xiàn)。

2.4 總體結(jié)構(gòu)

通過一個密鑰控制模塊為3DES提供三個56位的密鑰以及加/解密控制信號。密鑰的輸入是28位的,所產(chǎn)生的三個56位密鑰并不是同一時間提供給3DES的,相互之間有16個時鐘的延時,這樣可以保證修改密鑰后并不影響先前流水線的工作。再加上輸入、輸出接口就構(gòu)成了該設計的總體結(jié)構(gòu),如圖5所示。限于圖的大小,不影響理解的部分信號沒有畫出。加/解密的流程是先輸入六組28位的密鑰,然后就可以發(fā)送需要加/解密的數(shù)據(jù)了,中間可以有間斷,如果需要更改密鑰,也是先輸入改后的密鑰,再輸入數(shù)據(jù),可實時更改,無需等到流水線中最后一組數(shù)據(jù)加/解密完成。

本設計在ALTERA公司的QuartusⅡ環(huán)境下用VHDL、Verilog HDL實現(xiàn)設計輸入,采用同步時鐘,成功編譯、綜合、適配和仿真,并下載到Stratix系列FPGA芯片EP1S25F780C5中。在綜合的過程中用邏輯鎖等技術(shù)進行了優(yōu)化。消耗邏輯單元16250個,設計時鐘頻率可達95.07MHz。

參考文獻

1吳世忠.應用密碼學[M].北京:機械工業(yè)出版社,2003

2潘 松,黃繼業(yè).EDA技術(shù)實用教程.北京:科學出版社,2003