簡介

IEEE 1588標準誕生于2002年,主要定義網(wǎng)絡(luò)分布式時鐘的同步協(xié)議。測試與測量、電信和多媒體流處理等許多不同應(yīng)用,都開始首選這種時鐘同步方法。這種標準化時鐘同步法成本效益高,支持異構(gòu)系統(tǒng),并可提供納秒級同步精度。

本文介紹原版IEEE 1588-2002標準以及更新版本IEEE 1588-2008中的改進內(nèi)容。由于IEEE 1588在一些目標應(yīng)用中越來越重要,因此ADSP-BF518 Blackfin嵌入式處理器中也集成專用硬件來支持IEEE 1588。本文將概要介紹其功能,并通過一個示例來展示利用ADSP-BF518處理器解決方案獲得的時鐘同步性能結(jié)果。

現(xiàn)在幾點了?

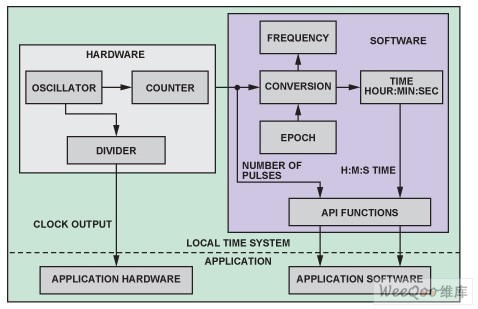

大多數(shù)系統(tǒng)都需要利用本振來維護自己的時間概念。圖1顯示硬件和軟件如何組合,在系統(tǒng)內(nèi)產(chǎn)生時間信息。

圖1. 本地計時

系統(tǒng)內(nèi)的硬件和軟件資源均可使用此時間信息。對于硬件,振蕩器時鐘會產(chǎn)生一個或多個物理時鐘信號(時鐘輸出),并可利用這些時鐘信號驅(qū)動或觸發(fā)系統(tǒng)的其它部分。軟件中維護的時間通常稱為“系統(tǒng)時間”。系統(tǒng)時間可以用時鐘脈沖數(shù)或秒/納秒的形式表示。系統(tǒng)軟件利用振蕩器時鐘脈沖數(shù)及其頻率信息得出時間,并提供“應(yīng)用程序編程接口”(API)函數(shù),軟件的其它部分可以使用這些函數(shù)檢索并設(shè)置時間。如果需要絕對時間,則所提供的時間將與預定義時間點,即基準時間點相關(guān)聯(lián)。

時鐘同步

許多應(yīng)用要求兩臺獨立的設(shè)備以同步方式工作。如果每臺設(shè)備僅依靠自己的振蕩器,則各振蕩器的特性與工作條件差異將會限制時鐘同步工作的能力。一些簡單可行的解決方案可以克服這些限制,包括:

●所有設(shè)備共用一個物理振蕩器。這種方法僅對距離很近的分布式系統(tǒng)可行;高頻時鐘信號無法實現(xiàn)長距離可靠傳輸。

●所有設(shè)備均使用特性幾乎完全相同的振蕩器。由于很難獲得幾乎完全一樣的振蕩器,并確保性能不隨時間飄移,因此這種方法不可行。更重要的是,各振蕩器的工作條件并不相同。

●如果所有設(shè)備均通過一個通信網(wǎng)絡(luò)(例如以太網(wǎng))互連,則這些設(shè)備可以通過網(wǎng)絡(luò)交換時間消息,根據(jù)單個“主”時鐘動態(tài)調(diào)整各自的時鐘。利用傳統(tǒng)的時間同步協(xié)議——“網(wǎng)絡(luò)時間協(xié)議”(NTP),系統(tǒng)中的每臺設(shè)備根據(jù)它從NTP時間服務(wù)器獲取的時間信息調(diào)整其時鐘。然而,該協(xié)議只能實現(xiàn)毫秒級同步精度。

IEEE 1588定義了一個新協(xié)議,能夠?qū)崿F(xiàn)納秒級同步精度。下面討論該標準如何實現(xiàn)這種水平的時鐘同步。

IEEE 1588有何作用

IEEE 1588標準定義了一種時間同步協(xié)議,適用于地理位置分散但通過某種通信技術(shù)(例如以太網(wǎng))互連的設(shè)備。設(shè)備之間通過交換時序消息,從而保持相同的絕對系統(tǒng)時間(用秒和納秒表示)。

要實現(xiàn)此目標,一個直觀的方法是將一臺具有“最佳”(最精確)時鐘的設(shè)備指定為“主時鐘”設(shè)備,讓它向其它設(shè)備廣播其時間。其它設(shè)備將會調(diào)整各自的時間,與主時鐘所發(fā)送的時間保持一致。不過,這種解決方案也有幾點不足:

主時鐘設(shè)備無法以極短的間隔廣播時間,因此“從”時鐘設(shè)備必須使用自己獨立的“低劣”振蕩器,在主時鐘設(shè)備的兩次廣播之間插入時間點。這將導致主時鐘更新周期之間的同步精度下降。

廣播路徑難免存在延遲,延遲幅度取決于通信技術(shù),例如物理信號沿導線從一臺設(shè)備傳輸至另一臺設(shè)備所需的時間。這種延遲會進一步擴大主時鐘與各從時鐘之間的失調(diào)。

主時鐘設(shè)備與各從時鐘設(shè)備之間的廣播路徑存在差異,這會進一步降低各從時鐘設(shè)備之間的同步精度。

IEEE 1588要求通過測量路徑延遲,解決第二個和第三個問題。它還要求待調(diào)整的從時鐘與主時鐘保持步調(diào)一致,從而減輕第一個問題。如果可能,使用更小的廣播間隔和更高質(zhì)量的振蕩器,可以進一步減輕第一個問題。

IEEE 1588如何測量通信延遲

IEEE 1588-2002定義了四種消息Sync、Followup、DelayReq和DelayResp,用來測量前向(主時鐘至從時鐘)和后向(從時鐘至主時鐘)路徑的通信延遲。更新版本IEEE 1588-2008還提供其它機制,新增三種消息:PdelayReq、PdelayResp和 PdelayRespFollowup來測量“點對點延遲”。

這些消息中,Sync、DelayReq、PdelayReq和PdelayResp是所謂“事件”消息,在離開和到達一臺設(shè)備時必須加上“時間戳”(記錄本地時間)。給分組加上時間戳的方法有兩種:

1.消息由軟件處理時出現(xiàn)軟件時間戳。通常出現(xiàn)在消息的接收/發(fā)送“中斷服務(wù)程序”(ISR)中,該時間戳為系統(tǒng)時間的當前值。

2.消息實際到達或離開設(shè)備時出現(xiàn)硬件時間戳。該時間戳操作由硬件執(zhí)行,硬件會維護自己的連續(xù)時間信息。

兩種時間戳方法均為IEEE 1588所接受,但硬件時間戳的精度明顯更高,如下文所述。

主時鐘設(shè)備到從時鐘設(shè)備的延遲

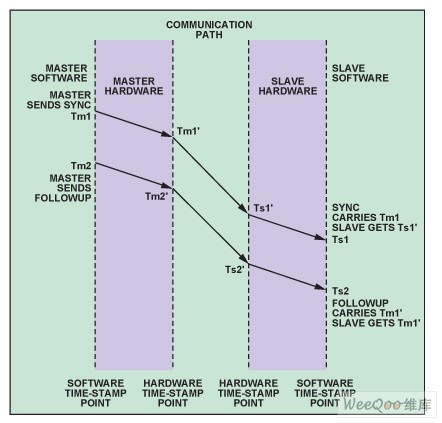

消息Sync和Followup由主時鐘設(shè)備發(fā)送,從時鐘設(shè)備負責接收這些消息,并計算主時鐘設(shè)備到從時鐘設(shè)備的通信路徑延遲。

圖2中,在時間點Tm1,主時鐘設(shè)備軟件讀取當前本地系統(tǒng)時間(Tm1,軟件時間戳),將其插入Sync消息中,并送出該消息。該消息在稍后的時間點Tm1'離開主時鐘設(shè)備,該時間點為硬件時間戳。該消息在時間點Ts1'(從時鐘設(shè)備本地時間)到達從時鐘硬件,從時鐘設(shè)備軟件在稍后的時間點Ts1收到該消息。該軟件將讀取硬件時間戳以獲得Ts1'。如果沒有通信延遲,Ts1'應(yīng)等于(Tm1' + Tms),其中Tms為主時鐘與從時鐘之間的時間差。該協(xié)議的最終目標是補償此時間差。

圖2. 測量主時鐘設(shè)備與從時鐘設(shè)備之間的通信延遲

發(fā)送Sync消息之后,主時鐘設(shè)備軟件通過時間戳單元讀取Sync消息的離開時間Tm1',將其插入Followup消息中,然后在時間點Tm2發(fā)送該消息。從時鐘設(shè)備軟件在時間點Ts2收到此消息。此時,從時鐘設(shè)備軟件有兩個時間:Ts1'(Sync到達時間)和Tm1'(Sync離開時間)。主從路徑延遲Tmsd由公式1確定。

![]() (1)

(1)

從時鐘設(shè)備到主時鐘設(shè)備的延遲

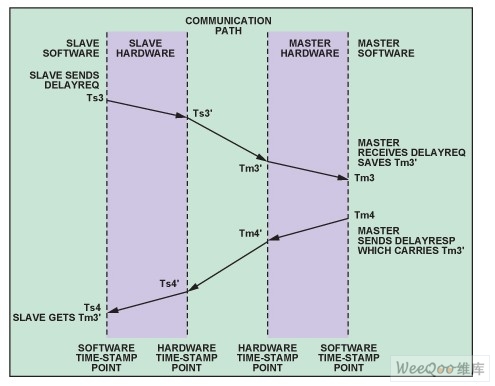

從時鐘設(shè)備發(fā)送DelayReq消息,主時鐘設(shè)備予以響應(yīng)發(fā)送DelayResp消息。利用這些消息,從時鐘設(shè)備可以計算從時鐘設(shè)備到主時鐘設(shè)備的通信路徑延遲。

在時間點Ts3(圖3),從時鐘設(shè)備軟件讀取當前本地系統(tǒng)時間(Ts3),將其插入DelayReq消息中,并送出該消息。

圖3. 測量從主通信延遲

DelayReq消息在稍后的時間點Tm3'到達主時鐘設(shè)備,由主時鐘設(shè)備軟件在時間點Tm3處理。然后,該軟件讀取時間戳以獲取到達時間Tm3',將其插入DelayResp消息中,并在時間點Tm4發(fā)送至從時鐘設(shè)備。當從時鐘設(shè)備軟件在時間點Ts4收到DelayResp消息時,它可以提取時間Tm3',并通過公式2計算從主通信延遲Tsmd。

![]() (2)

(2)

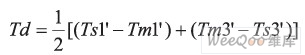

公式1和公式2中均有一個未知變量,即主從時間差Tms,因此無法單獨求得Tmsd或Tsmd。但是,如果我們合理地假設(shè)通信路徑是對稱的,即

![]() (3)

(3)

——這是IEEE 1588成立的關(guān)鍵假設(shè)——那么,將公式1與公式2相加可以得出:

(4)

(4)

由于從時鐘設(shè)備尋求與主時鐘設(shè)備同步,因此所有這些計算均由這些設(shè)備執(zhí)行。從時鐘設(shè)備從主時鐘設(shè)備的Followup消息獲得Tm1',從其Rx(接收)時間戳獲得Ts1',從其Tx(發(fā)送)時間戳獲得Ts3',并通過主時鐘設(shè)備的DelayResp消息獲得Tm3'。

如何計算從時鐘與主時鐘的時間差

一旦獲得通信路徑延遲Td,便可利用公式1或公式2輕松計算從時鐘與主時鐘的時間差,如公式5和公式6所示。

![]() (5)

(5)

![]() (6)

(6)

如何調(diào)整從時鐘設(shè)備的時間

知道與主時鐘的時間差之后,各從時鐘需要調(diào)整自己的本地時間,與主時鐘保持一致。該任務(wù)包括兩方面。第一,從時鐘設(shè)備需要加上時間差以調(diào)整絕對時間,使其時間在此刻與主時鐘時間完全一致。第二,從時鐘設(shè)備需要調(diào)整各自的時鐘頻率,與主時鐘的頻率保持一致。我們不能單靠絕對時間,因為時間差僅在一定期間內(nèi)應(yīng)用,可能是正值,也可能是負值;調(diào)整的結(jié)果是從時鐘時間向前跳躍或向后倒退。因此,在實際操作中,調(diào)整分兩步執(zhí)行:

1.如果時間差過大,例如1秒以上,則應(yīng)用絕對時間調(diào)整。

2.I如果時間差較小,則使從時鐘的頻率改變某一百分比。

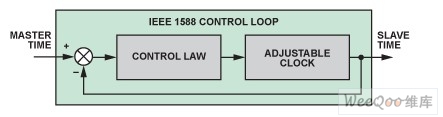

一般而言,該系統(tǒng)會變成一個控制環(huán)路,其中主時鐘時間是參考命令,而從時鐘時間是跟蹤主時鐘時間的輸出,二者之差驅(qū)動可調(diào)整時鐘。可以使用PID控制來實現(xiàn)特定跟蹤性能,這是許多IEEE 1588實施方案常用的方法。圖4顯示了這種控制環(huán)路。

圖4. IEEE 1588控制環(huán)路

點對點延遲

修訂版IEEE 1588-2008引入了新的機制來測量路徑延遲,稱為“點對點”(P2P)延遲。與之相比,上文討論的主從機制則是“端對端”(E2E)延遲。在支持IEEE 1588-2008的網(wǎng)絡(luò)中,主時鐘設(shè)備可以與從時鐘設(shè)備直接相連,或者隔幾個中繼站(級)相連。E2E延遲實際上是主時鐘設(shè)備到從時鐘設(shè)備的“總”延遲,包括其間的所有中繼站在內(nèi)。但是,P2P延遲則僅限于兩個直接相連的設(shè)備。通信路徑的總延遲等于所有中繼站的P2P延遲之和。從確保路徑對稱性的角度看,P2P機制可提供更高的精度。

如上文所述,IEEE 1588-2008新增了PdelayReq、PdelayResp和PdelayRespFollowup三種消息來測量P2P延遲。這些消息的工作方式與上文所述方式相似,詳情請看參考文獻3。

影響同步性能的因素

精心設(shè)計的IEEE 1588設(shè)備能夠?qū)崿F(xiàn)高度精確的時鐘同步,但也必須了解直接影響同步性能的主要因素,其中包括:

1.路徑延遲:如上文所述,IEEE 1588的路徑延遲測量假設(shè)通信路徑延遲是對稱的,即前向路徑的傳輸延遲與后向傳輸延遲相同。此外,在延遲測量期間,延遲不應(yīng)變化。測量期間延遲變化會導致不對稱和延遲抖動,這將直接影響同步精度。雖然無法在IEEE 1588設(shè)備的邊界之外控制延遲對稱性和抖動,但如果測量基于硬件時間戳,則可在設(shè)備內(nèi)改善路徑對稱性和抖動。由于中斷延時、環(huán)境切換和線程調(diào)度,軟件時間戳會導致明顯的抖動,而硬件時間戳則不存在這一問題。

2.時鐘的漂移和抖動特性:主時鐘的頻率和相位代表跟蹤控制系統(tǒng)的輸入,從時鐘則是控制對象。主時鐘的任何時變行為都會擾動該控制系統(tǒng),導致穩(wěn)態(tài)和瞬態(tài)兩種誤差。因此,時鐘的漂移和抖動越低,則同步精度越高。

3.控制法則:從時鐘調(diào)整如何校正從時鐘設(shè)備的時間誤差取決于控制方法。控制法則參數(shù)包括建立時間、過沖和穩(wěn)態(tài)誤差,都將直接影響時鐘同步性能。

4.時鐘分辨率:如圖1所示,本地時間的分辨率由時鐘頻率決定;最小時間增量為時鐘信號的一個周期。IEEE 1588-2002支持1 ns的時間分辨率,IEEE 1588-2008則支持2–16 ns的時間分辨率。216 (!) GHz(甚至1 GHz)的時鐘是不現(xiàn)實的。本地時鐘的量化會影響本地時間測量和控制的精度。

5.Sync消息的發(fā)送周期:從時鐘的更新頻率最終會影響同步精度。因為時間誤差是從時鐘頻率誤差的整體累積值,所以發(fā)送周期越長,下一個Sync所觀察到的時間誤差一般會越大。

6.延遲測量的頻率:以預期相鄰采樣點之間延遲沒有明顯變化的間隔時間,定期執(zhí)行延遲測量。如果IEEE 1588網(wǎng)絡(luò)的延遲變化較大,則增加延遲測量頻率可以改善時鐘同步性能。

哪個是主時鐘?

在考慮如何精確確定主時鐘設(shè)備與從時鐘設(shè)備之間的時間差之后,下一個相關(guān)問題是:在成百上千臺互連設(shè)備中,如何確定哪一臺設(shè)備充當主時鐘。

IEEE 1588定義了一種稱為“最佳主時鐘”(BMC)算法的方法,用于選擇主時鐘設(shè)備。這種方法要求IEEE 1588網(wǎng)絡(luò)的每臺設(shè)備均提供一個數(shù)據(jù)集,描述其本地時鐘的性質(zhì)、質(zhì)量、穩(wěn)定性、唯一識別符和首選設(shè)置。當一臺設(shè)備加入IEEE 1588網(wǎng)絡(luò)時,它會廣播其時鐘的數(shù)據(jù)集,并接收所有其它設(shè)備的數(shù)據(jù)集。利用所有參與設(shè)備的數(shù)據(jù)集,每臺設(shè)備均運行同一BMC算法,以確定主時鐘及其自己的未來狀態(tài)(主時鐘或從時鐘)。由于所有設(shè)備均采用同樣的數(shù)據(jù)獨立執(zhí)行同一算法,因此結(jié)論將會相同,設(shè)備之間不需要進行任何協(xié)商。有關(guān)BMC算法的更多詳細信息,請看參考文獻2和3。

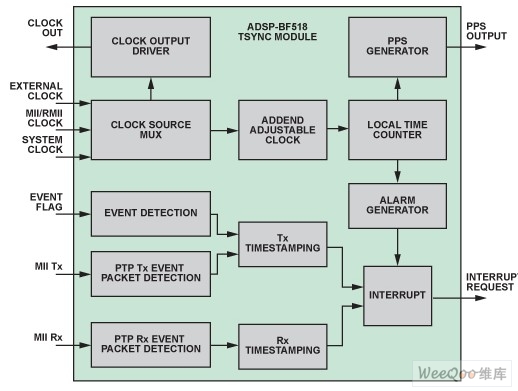

ADSP-BF518處理器支持IEEE 1588

ADI公司Blackfin DSP系列最近新增一款產(chǎn)品:ADSP-BF518處理器。像前款產(chǎn)品ADSP-BF537,4一樣,該處理器內(nèi)置“以太網(wǎng)媒體訪問控制器”(EMAC)模塊。它還具有TSYNC模塊,進一步擴展了支持IEEE 1588標準EMAC功能的能力;還提供其它額外特性,可支持以太網(wǎng)的各種IEEE 1588應(yīng)用。圖5顯示了TSYNC模塊的框圖。 ADSP-BF51x Blackfin處理器硬件參考提供了更多信息。

圖5. ADSP-BF518處理器TSYNC模塊的框圖

分組檢測

ADSP-BF518處理器可以檢測IEEE 1588的所有事件消息,包括送入和送出的分組,并為其提供硬件時間戳。因為事件消息時間戳的精度及其提取位置會影響路徑延遲的對稱性和穩(wěn)定性要求,所以IEEE 1588系統(tǒng)的精度在很大程度上取決于這二者。ADSP-BF518的TSYNC模塊持續(xù)監(jiān)控MAC控制器與以太網(wǎng)“物理接口收發(fā)器”(PHY)之間的硬件接口,即“媒體獨立接口”(MII),并且只要檢測到事件消息,就會產(chǎn)生硬件時間戳,這一功能可提高ADSP-BF518的同步精度。

事件消息檢測功能是可編程的,基本配置有兩種:支持IEEE 1588-2002(默認狀態(tài))或支持IEEE 1588-2008。此外,這種可編程能力還支持將來版本的IEEE 1588,以及其它要求時間戳的一般協(xié)議,包括配置為給進出處理器的每個以太網(wǎng)分組加上時間戳。

靈活的時鐘源

本地時鐘的屬性對于IEEE 1588系統(tǒng)的性能很重要。為了滿足各種不同應(yīng)用的要求,ADSP-BF518處理器可提供三種本地時鐘源選項:系統(tǒng)時鐘、外部時鐘或以太網(wǎng)時鐘。如果應(yīng)用具有特定時鐘要求,則可以選擇“外部時鐘”,并提供定制時鐘源。如果主時鐘設(shè)備與從時鐘設(shè)備“背靠背”連接,由于“以太網(wǎng)時鐘”來自以太網(wǎng)線路,而且兩臺設(shè)備采用同一時鐘工作,因此該時鐘選項可以提供良好的精度。一般應(yīng)用可以選擇處理器的“系統(tǒng)時鐘”作為時鐘源。

所選源時鐘也由TSYNC模塊驅(qū)動,通過特定引腳Clockout作為處理器輸出,系統(tǒng)的其它部分可利用該輸出提供本地時間信息。

PPS輸出

“每秒脈沖”(PPS)信號是時間信息的物理表示。它名義上是一個1-Hz信號,在每個1秒轉(zhuǎn)換時間發(fā)出一個脈沖。它可用來控制本地設(shè)備,或者在發(fā)生網(wǎng)絡(luò)故障時提供輔助時間通道。它也可以用于測試。兩臺設(shè)備的PPS信號之間的相位差是二者時間偏移的物理量度。

ADSP-BF518處理器提供靈活的PPS輸出。它利用可編程“開始時間”(PPS_ST)和周期(PPS_P)產(chǎn)生一個在時間(PPS_ST + n × PPS_P)發(fā)出脈沖的信號,其中n = 1, 2, 3…。基本用法是將PPS_P設(shè)置為1秒,并將PPS_ST設(shè)置為用秒數(shù)表示的將來任一時刻,從而產(chǎn)生PPS信號。參考基本用法,可以利用這種PPS輸出功能產(chǎn)生具有可編程頻率和開始時間的周期性信號。

輔助快照

一些應(yīng)用可能需要按照標志信號切換指示,給某一事件加上時間戳。ADSP-BF518的TSYNC模塊通過輔助“快照”功能,使用一個專用引腳來接收外部標志,以便實現(xiàn)這種請求。切換標志將觸發(fā)該模塊捕捉時間戳寄存器中的當前本地時間,供軟件訪問。

報警

如果應(yīng)用需在特定時間執(zhí)行一項任務(wù),則可以用TSYNC模塊的“報警”功能。這項功能可以設(shè)置本地絕對時間,到達該時間時,就會觸發(fā)處理器中斷。然后,軟件便可利用中斷執(zhí)行任務(wù)。

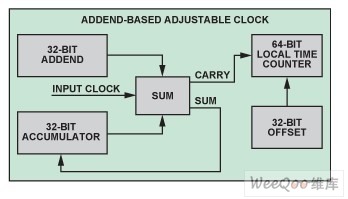

可調(diào)時鐘

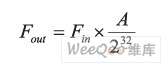

TSYNC模塊的可調(diào)時鐘是一種“基于加數(shù)”的時鐘。如圖6所示,它獲得一個固定輸入時鐘信號,并輸出該輸入的“盜取脈沖”版本信號:對于每個輸入時鐘,“加數(shù)”的值增加到累加器中,并且每次累加器溢出時,進位位就會驅(qū)動“本地時間計數(shù)器”,從而產(chǎn)生以脈沖計數(shù)值表示的本地時間。更改加數(shù)可以調(diào)整本地時鐘的頻率,因為加數(shù)決定累加器溢出的頻率,從而決定本地時間計數(shù)器遞增的頻率。如果輸入時鐘的頻率為Fin,且加數(shù)的值為A,則本地時鐘頻率為:

(7)

(7)

圖6. 基于加數(shù)的可調(diào)時鐘

采用ADSP-BF518處理器的IEEE 1588實施方案

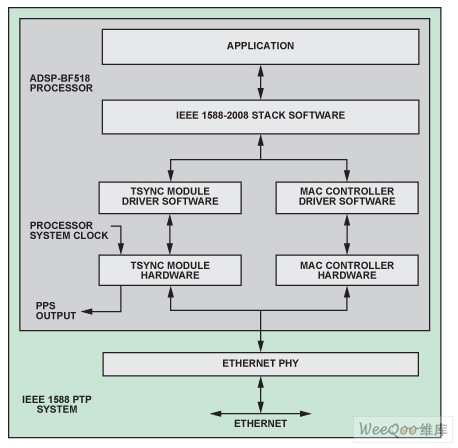

ADSP-BF518處理器上構(gòu)建了一個完整的IEEE 1588-2008兼容系統(tǒng),如圖7所示。

圖7. 采用ADSP-BF518的IEEE 1588實施方案

處理器的TSYNC模塊檢測送入和送出的IEEE 1588消息,并通過硬件給事件消息加上時間戳。由IXXAT (IXXAT Automation GmbH)提供的IEEE 1588協(xié)議棧軟件可實現(xiàn)標準所要求的消息交換協(xié)議。它利用TSYNC驅(qū)動程序讀取、寫入并調(diào)整TSYNC時鐘,并使用MAC控制器驅(qū)動程序在以太網(wǎng)MAC層(開放系統(tǒng)互連模型的第二層)發(fā)送和接收消息。它還可實現(xiàn)P2P延遲測量的控制法則和過濾。以太網(wǎng)PHY選擇具有低抖動延遲特性的National Semiconductor DP83848 。為簡明起見,TSYNC模塊時鐘源選擇處理器的系統(tǒng)時鐘(80 MHz)。

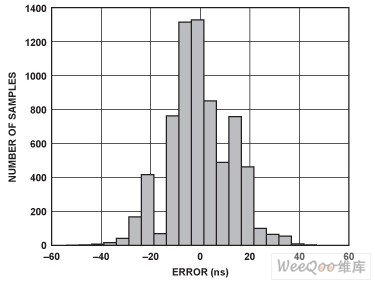

圖8. ADSP-BF518上IEEE 1588系統(tǒng)的從時鐘誤差直方圖

圖8是兩個完全相同的ADSP-BF518 IEEE 1588系統(tǒng)之間的測量誤差直方圖,由此可看出該器件的時鐘同步性能。在約1700秒的時間內(nèi)共進行了6938次測量。最終平均誤差為0.015 ns,標準差為12.96 ns。該測試所用的Sync消息間隔為0.25秒。

結(jié)論

IEEE 1588標準提供了一種高精度、低成本的分布式時鐘同步方法。雖然IEEE 1588并未明文要求硬件支持,但硬件輔助消息檢測和時間戳對于實現(xiàn)極高同步精度至關(guān)重要。ADSP-BF518為IEEE 1588-2002和IEEE 1588-2008提供硬件支持,包括各種應(yīng)用的支持功能。利用ADSP-BF518處理器和IXXAT IEEE 1588-2008協(xié)議軟件實施IEEE 1588技術(shù),已證明可以實現(xiàn)高精度時鐘同步。