數(shù)字調(diào)制解調(diào)器在點對點的數(shù)據(jù)傳輸中得到了廣泛的應(yīng)用,。通常的二進制數(shù)字調(diào)制解調(diào)

器是建立在模擬載波上的,,在電路實現(xiàn)時需要模擬信號源,這會給全數(shù)字應(yīng)用場合帶來不方便,。本文分析了MSK(最小頻移鍵控)數(shù)字調(diào)制信號特征,,提出一種全數(shù)字固定數(shù)據(jù)速率MSK調(diào)制解調(diào)器的設(shè)計方法,應(yīng)用VHDL 語言進行了模塊設(shè)計和時序仿真,。硬件部分在Altera公司 EP2C15AF256C8N FPGA 上實現(xiàn)了MSK 數(shù)字調(diào)制解調(diào)器,,并在常州市科技攻關(guān)項目:糧庫儲糧安全網(wǎng)絡(luò)智能監(jiān)測系統(tǒng)的嵌入式測控部分應(yīng)用。實測表明,,數(shù)字MSK 調(diào)制解調(diào)器具有絡(luò)恒定,,相位連續(xù),頻帶利用率高的優(yōu)點,。并且在FPGA 上實現(xiàn)時設(shè)計效率高,,可與其他模塊共用片上資源,對于全數(shù)字系統(tǒng)中的短距離數(shù)據(jù)通信是較好的解決方案,。

1 數(shù)字MSK 調(diào)制的載波頻率與相位常數(shù)

最小頻移鍵控MSK ( Minimum Frequency Shift Keying ) 是二進制連續(xù)相位FSK 的一

種特殊形式,。有時也稱為快速頻移鍵控(FFSK)。MSK 調(diào)制方式能以最小的調(diào)制指數(shù)(0.5)獲得正交信號,, 同時MSK 比2PSK 的數(shù)據(jù)傳輸速率高,,且在帶外的頻譜分量要比2PSK 衰減更快。

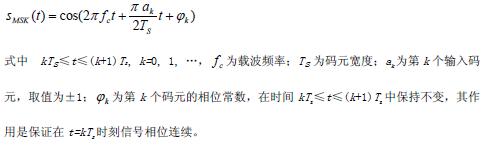

MSK 是恒定包絡(luò)連續(xù)相位頻率調(diào)制,,其信號的表示式為

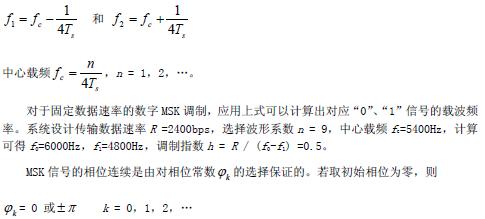

MSK 調(diào)制必須同時滿足調(diào)制指數(shù)0.5 和相位連續(xù)條件,,由MSK 信號表示可知,為了使調(diào)

制指數(shù)為0.5,,MSK 信號的兩個頻率應(yīng)分別為:

上式反映了MSK 信號前后碼元區(qū)間的約束關(guān)系。MSK 信號在第k 個碼元的相位常數(shù)不僅與當(dāng)前碼元的取值有關(guān),,而且還與前一個碼元的取值及相位常數(shù)有關(guān),。在數(shù)字載波的情況下,,上述條件等同于根據(jù)前一碼元的相位,選擇當(dāng)前碼元的相位是同相或反相,,以保證數(shù)字MSK信號的相位連續(xù),。

2 數(shù)字MSK 調(diào)制解調(diào)器FPGA 模塊實現(xiàn)

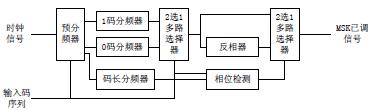

用FPGA 實現(xiàn)的MSK 調(diào)制器模塊如圖1 所示。

圖1 MSK 調(diào)制器模塊

圖中預(yù)分頻器和“0”,、“1”碼分頻器組成載波發(fā)生器,,在輸入碼序列同步信號的控制下

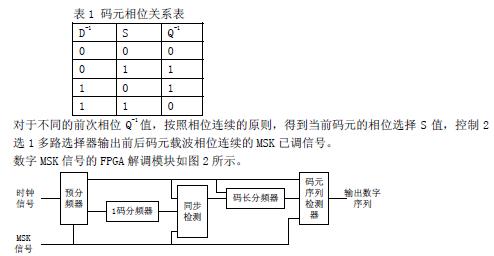

分別產(chǎn)生“0”碼和“1”碼的數(shù)字載波。為了方便設(shè)計與調(diào)整,,預(yù)分頻器設(shè)置2 級分頻電路,,分頻系數(shù)分別為D1 和D2,從分頻效率考慮,,D1 和D2 的乘積應(yīng)為總分頻系數(shù)的最大公共因子,。“0”碼和“1”碼分頻器的分頻系數(shù)C1、C2 的設(shè)置必須滿足調(diào)制指數(shù)0.5 的條件,。輸入調(diào)制信號數(shù)字序列控制2 選1 多路選擇器,,選出對應(yīng)輸入碼流中“0”、“1”碼元的數(shù)字載波,。相位檢測模塊與第二級2 選1 多路選擇器,、碼長分頻器和反相器組成連續(xù)相位形成電路。在前面確定“0”,、“1”碼元的數(shù)字載波時,,每個碼元的載波周期數(shù)也隨之確定, 其中“0”,、“1”數(shù)字載波相位差固定為180°,,因此可以簡單地用0、1 來表示2 個載波相位,。在相位檢測模塊中,,碼長分頻器作為1bit 延時的時鐘信號,輸入數(shù)字信號延遲一碼元信號D-1 與前次產(chǎn)生的2 選1 選擇器控制信號S 比較,,得到前一碼元結(jié)束時的相位Q-1,,其結(jié)果如表1 所示。

圖2 MSK 解調(diào)器模塊

數(shù)字MSK 信號的解調(diào)是由碼元同步和碼序列檢測二部分實現(xiàn)的,。預(yù)分頻器,、“1”碼分頻器和同步檢測模塊組成碼元同步電路,通過對輸入信號中的“1”碼檢測建立碼元同步,。在同步檢測模塊中,,“1”碼分頻器的同相和反相碼同時與輸入信號比較,并由同步碼長計數(shù)器計數(shù),當(dāng)計數(shù)長度等于碼元長度時輸出同步信號,。進入碼元同步狀態(tài)后,,在碼長分頻器輸出的碼元同步信號控制下,碼序列檢測器對輸入信號中的“1”碼(同相及反相碼)進行檢測并輸出解調(diào)數(shù)字序列,。解調(diào)模塊中的預(yù)分頻器和“1”碼分頻器和在半雙工通信方式中可與調(diào)制模塊合用以減少目標(biāo)器件片上資源的占用,。MSK 調(diào)制/解調(diào)器的FPGA 模塊中,計數(shù)器,、分頻器和多路選擇器用VHDL 程序可以簡單

實現(xiàn),,碼元序列檢測器的部分VHDL 結(jié)構(gòu)描述如下:

architecture behav of codesdect is

signal m : integer range 0 to 3;

signal sdata : std_logic_vector(2 downto 0);

begin

cdata<= wavenum;

process(clk,clr)

begin

if clr='1' then m<=0;

elsif clk'event and clk='1' then

case m is

when 0 => if datain = cdata (2) then m<=1; else m <= 0 ; end if;

…

when 2 => if datain = cdata (0) then m<=3; else m <= 0 ; end if;

when others => m <= 0;

end case;

end if;

end process;

process(m)

begin

if m=3 then outputt<='1';

else outputt<='0';

end if;

end process;

end behav;

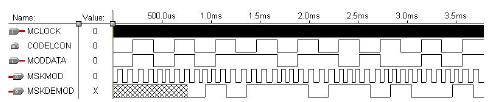

數(shù)字MSK 調(diào)制/解調(diào)器模塊在Altera 公司FPGA:EP2C15AF256C8N 上實現(xiàn)。EP2C15 是Altera 公司基于90nm 工藝的第二代Cyclone 器件(CycloneⅡ),,片內(nèi)集成14,,448 邏輯單元(LE),240Kb 嵌入式RAM 塊,,26 個18×18 乘法器,,4 個鎖相環(huán)(PLL),具有高速差分I/O能力,,在音視頻多媒體,、汽車電子、通信及工業(yè)控制領(lǐng)域等有廣泛的適用性,,是一款高性能低成本器件,。圖3 是MSK 調(diào)制/接解調(diào)器的時序仿真結(jié)果。

圖3 MSK 調(diào)制/解調(diào)器時序仿真

由圖中可見,,數(shù)字基帶調(diào)制信號MODDATA 經(jīng)過MSK 調(diào)制器被調(diào)制到高頻數(shù)字載波上,,形成MSK 已調(diào)信號MSKMOD,其中“0”碼為2.5 個載波周期,,“1”碼為2 個載波周期,,調(diào)制指數(shù)為0.5,同時載波相位連續(xù),。MSKDEMOD 為接收端MSK 解調(diào)后的信號,,除了傳輸時延,解調(diào)信號完全恢復(fù)了發(fā)送端數(shù)字基帶調(diào)制信號,。

3 結(jié)論

MSK 調(diào)制具有載波相位連續(xù),,頻帶利用率高的優(yōu)點,在通常的應(yīng)用中需要專用集成電路

構(gòu)成調(diào)制/解調(diào)電路,?;谟布枋稣Z言用FPGA 實現(xiàn)MSK 調(diào)制/解調(diào)器,可充分利用FPGA片內(nèi)資源,,使數(shù)據(jù)采集測量控制與傳輸集中于單一芯片,,有利于提高系統(tǒng)的經(jīng)濟性和可靠性,,具有一定的應(yīng)用價值。本文作者創(chuàng)新點在于提出了一種保證調(diào)制指數(shù)為0.5 同時載波相位連續(xù)的數(shù)字MSK 信號的設(shè)計方法,,用VHDL 語言設(shè)計了調(diào)制/解調(diào)模塊并在FPGA 器件上實現(xiàn),。