摘要: 針對(duì)在自動(dòng)控制系統(tǒng)設(shè)計(jì)領(lǐng)域和通信領(lǐng)域中有著廣泛運(yùn)用的AD7862芯片, 介紹了一種基于FPGA 的驅(qū)動(dòng)接口電路的設(shè)計(jì)。闡述了AD7862的特點(diǎn)及基本功能, 以及基于這些功能特點(diǎn)的驅(qū)動(dòng)時(shí)序, 并以此時(shí)序?yàn)榛A(chǔ)在FPGA 芯片中實(shí)現(xiàn)了AD7862 的驅(qū)動(dòng)電路。給出了主要的VHDL代碼以及最終的仿真測(cè)試結(jié)果, 實(shí)現(xiàn)了對(duì)AD7862芯片的穩(wěn)定可靠驅(qū)動(dòng), 同時(shí)也驗(yàn)證了所設(shè)計(jì)驅(qū)動(dòng)電路的正確性。

0、引言

在自動(dòng)控制的很多應(yīng)用場(chǎng)合, 都需要實(shí)時(shí)對(duì)信號(hào)進(jìn)行采樣分析, 然后由DSP來(lái)進(jìn)行運(yùn)算控制。AD芯片是采樣中最常用的芯片, 本文主要對(duì)ADI 公司的AD7862芯片進(jìn)行介紹, 同時(shí)為它設(shè)計(jì)了驅(qū)動(dòng)接口電路。由于AD7862不能自動(dòng)工作, 需要給它提供相關(guān)的驅(qū)動(dòng)信號(hào)才能觸發(fā)它進(jìn)行轉(zhuǎn)換,本文用FPGA 芯片給它做一個(gè)接口驅(qū)動(dòng)電路, 并詳細(xì)的介紹了驅(qū)動(dòng)電路程序的設(shè)計(jì), 設(shè)計(jì)的電路為AD7862提供了非常好的驅(qū)動(dòng)作用, 并在實(shí)際運(yùn)用中能使其穩(wěn)定的工作。

1、AD7862芯片簡(jiǎn)介

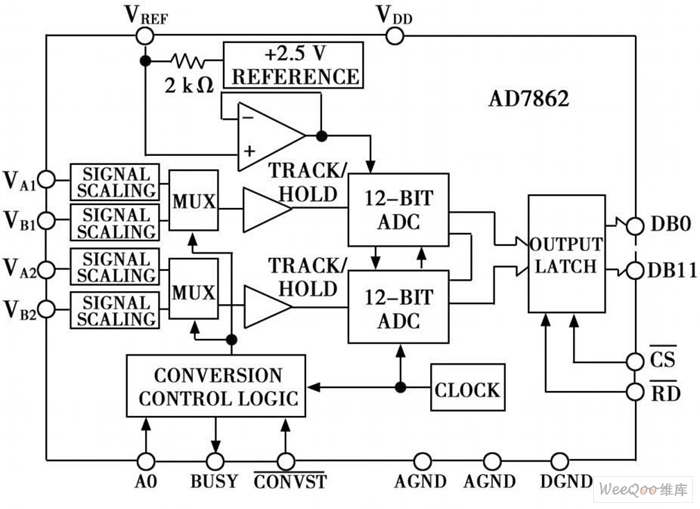

AD7862是美國(guó)AD I公司出品的12 bit高速, 低功耗轉(zhuǎn)換器, 單電源5伏供電。共有4 個(gè)模擬輸入端, 被分為兩個(gè)通道( A& B), 通過(guò)輸入端A0來(lái)進(jìn)行選擇。每一個(gè)通道有兩個(gè)輸入端( VA1& VA2或者VB1&VB2) 。能夠接受的模擬信號(hào)的輸入范圍為正負(fù)10伏。不過(guò)模擬信號(hào)的輸入端的過(guò)壓保護(hù)允許輸入電壓達(dá)到正負(fù)17 伏。原理框圖如圖1所示。

AD7862原理框圖

圖1 AD7862原理框圖。

AD7862芯片具有以下特點(diǎn):

( 1) 對(duì)每一個(gè)通道而言, 從啟動(dòng)轉(zhuǎn)換到轉(zhuǎn)換完成需要3. 6 s的時(shí)間。

( 2) 芯片由5 V 單電源供電, 功耗低, 工作時(shí)典型值為60 mW。具有自動(dòng)休眠模式, 當(dāng)一次轉(zhuǎn)換完成后自動(dòng)進(jìn)入休眠模式, 節(jié)省電能。當(dāng)下一個(gè)轉(zhuǎn)換周期來(lái)臨時(shí)在自動(dòng)蘇醒。

( 3) 提供一個(gè)高速并行接口, 和微處理器、微控制器以及數(shù)字信號(hào)處理器的連接變得容易。

( 4) AD7862系列共有三個(gè)版本分別針對(duì)三種不同的輸入范圍。其中AD7862—10針對(duì)標(biāo)準(zhǔn)工業(yè)級(jí)輸入范圍正負(fù)10伏; AD7862—3 主要針對(duì)普通信號(hào)輸入范圍正負(fù)2. 5 V。

AD7862—2被用于單極0 到2. 5 V 的輸入范圍。對(duì)AD7862—10和AD7862-3來(lái)說(shuō), 轉(zhuǎn)換輸出的12位為二進(jìn)制補(bǔ)碼, 對(duì)于AD7862-2來(lái)說(shuō), 輸出的為12位的原碼。

2、接口電路程序設(shè)計(jì)

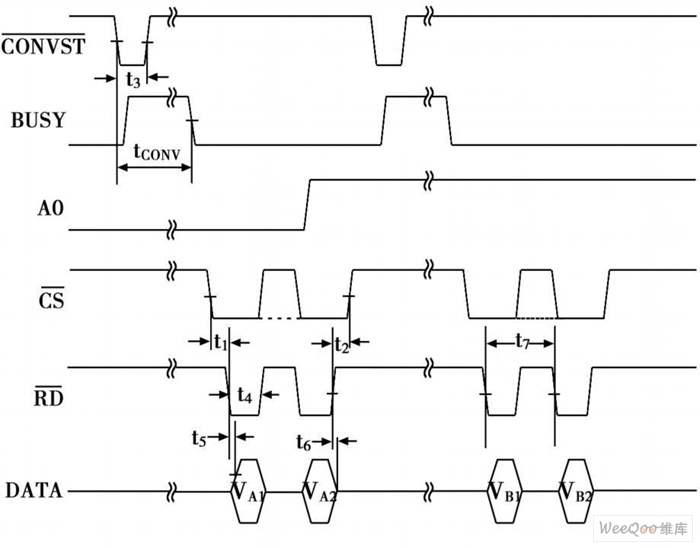

在本設(shè)計(jì)中用的是AD7862??10, 采用高速轉(zhuǎn)換模式, 典型轉(zhuǎn)換時(shí)序如圖2所示。

高速轉(zhuǎn)換模式時(shí)序圖

圖2高速轉(zhuǎn)換模式時(shí)序圖。

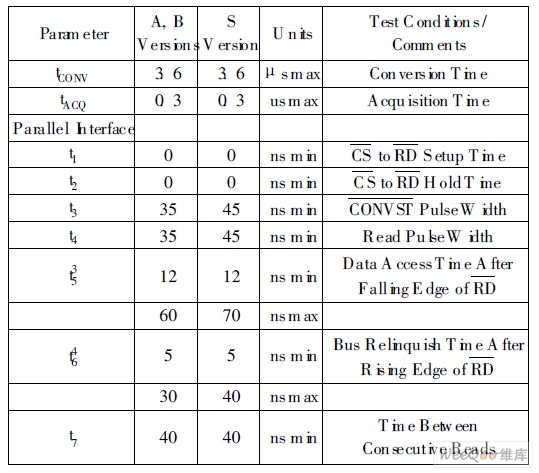

圖2中對(duì)應(yīng)的時(shí)間參數(shù)的要求如下表1所示。

表1高速采樣模式時(shí)序參數(shù)表。

高速采樣模式時(shí)序參數(shù)表

從圖2的時(shí)序圖可以看出AD7862 通過(guò)輸入脈沖信號(hào)CONVST啟動(dòng)轉(zhuǎn)換。在CONVST 信號(hào)的下降沿, 片上的兩個(gè)track /ho ld都同時(shí)的被設(shè)置為ho ld狀態(tài), 兩個(gè)通道開(kāi)始進(jìn)行轉(zhuǎn)換。轉(zhuǎn)換時(shí)鐘由內(nèi)置的晶振提供。BUSY 信號(hào)指示轉(zhuǎn)換結(jié)束, 同時(shí)兩個(gè)通道的轉(zhuǎn)換結(jié)果可以被讀出。由A0 的值來(lái)決定第一次讀取的值是VA1 或者VB1, 第二次讀取的是VA2或者VB2。當(dāng)CS信號(hào)和RD信號(hào)為低時(shí), 數(shù)據(jù)被從12位的并行數(shù)據(jù)線上讀取。在高速轉(zhuǎn)換模式下, AD7862 的轉(zhuǎn)換時(shí)間為3. 6 us, track /ho ld收集時(shí)間為0. 3 us。為了保證最佳轉(zhuǎn)換效果, 在轉(zhuǎn)換期間和下一次轉(zhuǎn)換開(kāi)始前300 ns不能進(jìn)行讀取操作。

上述的時(shí)序圖對(duì)應(yīng)為先讀取VA1和VA2, 然后在讀取VB1和VB2, 對(duì)應(yīng)的信號(hào)A0首先被設(shè)為低電平, 然后被拉為高電平。在設(shè)計(jì)驅(qū)動(dòng)電路的過(guò)程中, 一定要保證設(shè)計(jì)的時(shí)序滿足上述時(shí)序參數(shù)的要求 , 不然就有可能發(fā)生采樣不準(zhǔn), 出錯(cuò)。

結(jié)合AD7862的轉(zhuǎn)換速度, FPGA選擇10MH z的處理時(shí)鐘。對(duì)于整個(gè)轉(zhuǎn)換過(guò)程的控制用一個(gè)狀態(tài)機(jī)來(lái)完成, 狀態(tài)機(jī)分為12 個(gè)狀態(tài)( idle, convert1, busy1, reada1, w ait1, reada2,sw apchna,l convert2, busy2, readb1, w ait2, readb2), 其中idle狀態(tài)為空閑等待轉(zhuǎn)換狀態(tài); convert1指示第一次轉(zhuǎn)換啟動(dòng)狀態(tài);busy1指示第一次轉(zhuǎn)換狀態(tài); reada1狀態(tài)下讀取VA1; wait1狀態(tài)為讀取VA1和VA2之間的等待狀態(tài); reada2狀態(tài)下讀取VA2; sw apchnal狀態(tài)指示交換到另一個(gè)通道進(jìn)行轉(zhuǎn)換;convert2指示第二次轉(zhuǎn)換啟動(dòng)狀態(tài); 剩余狀態(tài)和前面的類似,只不過(guò)是針對(duì)VB1 和VB2 而言。設(shè)計(jì)代碼如下( 只描述VA1和VA2的部分, 剩下的類似):

process( clkdiv4, nrst)

beg in

if nrst = ‘0’ then

adc_state < = id le;

e lsif( r ising _edge( clkd iv4) ) then

case adc_state is

when idle= >

ada0< = '0' ;

adconv< = '1';

adncs< = '1';

adnrd< = '1';

clkcnt< = 0;

if( start= ‘1’) then

adc_state< = convert1;

end if;

w hen convert1= >

ada0< = '0';

adconv< = '0' ;

if( adbusy= '1') then

adc_state< = busy1;

end if;

w hen busy1= >

adconv< = '1';

if( adbusy= '0') then

adc_state< = reada1;

end if;

when reada1= >

if ( c lkcnt= 2) then

addataa1< = 0000 & adda tain;

end if;

if( c lkcnt= 4) then

adc_state< = w a it1;

adncs< = '1';

adnrd< = '1';

clkcnt< = 0;

else

clkcnt< = c lkcnt+ 1;

adncs< = '0';

adnrd< = '0';

end if;

when wait1= >

adc_state< = reada2;

when reada2= >

if ( c lkcnt= 2) then

addataa2< = 0001 & adda tain;

end if;

3設(shè)計(jì)電路的仿真驗(yàn)證

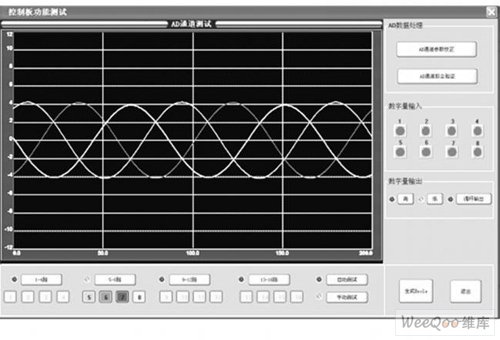

最終設(shè)計(jì)用Quartus 2 軟件編譯綜合后在板上測(cè)試,F(xiàn)PGA 接口電路接受到的轉(zhuǎn)換數(shù)據(jù)傳給DSP芯片, 然后將DSP受到的數(shù)據(jù)用實(shí)時(shí)監(jiān)控軟件顯示。圖3是給AD 輸入端加50 H z的正弦波信號(hào)(同時(shí)對(duì)其中三個(gè)輸入端加信號(hào)), 監(jiān)控軟件顯示的波形。

軟件顯示波形圖

圖3 軟件顯示波形圖。

從圖3波形圖可以看出, 接口驅(qū)動(dòng)電路成功的控制了AD7862芯片的采樣過(guò)程, 從而驗(yàn)證了驅(qū)動(dòng)電路設(shè)計(jì)的正確性。