隨著EDA技術(shù)的發(fā)展,由于其在電子系統(tǒng)設(shè)計(jì)領(lǐng)域中的明顯優(yōu)勢,,FPGA已經(jīng)在許多方面得到了廣泛應(yīng)用,,特別是在無線通信領(lǐng)域,F(xiàn)PGA以其極強(qiáng)的實(shí)時性,,指令軟件編程的極大靈活性贏得了巨大的市場,。本文采用FPGA來設(shè)計(jì)一款廣泛應(yīng)用于計(jì)算機(jī)、Modem、數(shù)據(jù)終端以及許多其他數(shù)字設(shè)備之間的數(shù)據(jù)傳輸?shù)膶S卯惒讲⑿型ㄐ沤涌谛酒?,?shí)現(xiàn)了某一時鐘域(如66 MHz)的8位并行數(shù)據(jù)到另一低時鐘域(如40 MHz)16位并行數(shù)據(jù)的異步轉(zhuǎn)換,,并且客戶可以根據(jù)自己的要求進(jìn)行數(shù)據(jù)定義。完成數(shù)據(jù)在不同時鐘域間的正確傳遞的同時防止亞穩(wěn)態(tài)的出現(xiàn),,保持系統(tǒng)的穩(wěn)定,,是電路設(shè)計(jì)的關(guān)鍵。

1 時鐘域轉(zhuǎn)換中亞穩(wěn)態(tài)的產(chǎn)生

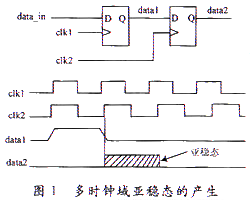

觸發(fā)器是數(shù)字電路設(shè)計(jì)中的一個重要元件,,而觸發(fā)器工作過程中存在數(shù)據(jù)建立與保持時間的約束,,如果這種約束得不到滿足,觸發(fā)器就會進(jìn)入某個不確定狀態(tài)——亞穩(wěn)態(tài),。亞穩(wěn)態(tài)的存在可能導(dǎo)致連鎖反應(yīng),,以致引起整個系統(tǒng)功能混亂。在單時鐘域電路設(shè)計(jì)中由于不存在時鐘之間的延遲和錯位,,所以建立條件和保持條件的時間約束容易滿足,。而在多時鐘域里由于各個模塊的非同步性,則必須考慮亞穩(wěn)態(tài)的發(fā)生,,如圖1所示,。

2 多時鐘域數(shù)據(jù)傳遞方案

多時鐘域傳遞的信號有兩種,其一為控制信號,,其二為數(shù)據(jù)流信號。針對這兩種不同的信號,,分別采取不同方案遏制系統(tǒng)墮入亞穩(wěn)態(tài),。對控制信號采用同步器裝置,即在2個不同的時鐘域之間插入同步器,;而對于不同獨(dú)立時鐘域之間的數(shù)據(jù)流傳遞,,為了避免異步時鐘域產(chǎn)生錯誤的采樣電平,采用FIFO存儲器作為其轉(zhuǎn)換接口,,在輸入端口使用寫時鐘寫數(shù)據(jù),,在輸出端口使用讀時鐘讀數(shù)據(jù),這樣就完成了異步時鐘域之間的數(shù)據(jù)交換,。

芯片的總體邏輯框圖如圖2所示,,圖中輸入輸出信號定義如表1所示。

從邏輯結(jié)構(gòu)上將芯片劃分為3塊:寫時鐘域I/OBUFFER,、讀時鐘域I/O BUFFER及FIFO存儲器,。I/O BUFFER的主要作用是對外部信號進(jìn)行預(yù)處理,消除外部信號的毛刺,,保證信號可靠并使外部的信號與時鐘信號同步,,消除不穩(wěn)定的因素。根據(jù)信號的數(shù)目,BUFFER由相應(yīng)數(shù)目的多個D觸發(fā)器構(gòu)成,。

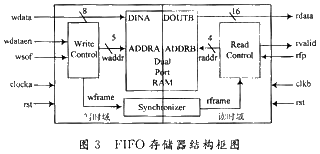

FIFO存儲器結(jié)構(gòu)框圖如圖3所示,,他由雙端口存儲器(Dual Port RAM)、寫控制單元(Writc Control)和讀控制單元(Read Control)構(gòu)成,。其中DUAL PORT RAM是由ISE6.0的一個編輯軟件CORE GENERATER自動生成,,使用者只需設(shè)定RAM的端口數(shù)、內(nèi)存大小和瀆寫控制便可以生成一個適合程序的子模塊,。由于讀寫時鐘屬于不同的時鐘域,,滿幀信號Frame從寫控制單元向讀控制單元傳遞時必須采取同步器(Synchronizer)同步。

2.1 寫控制單元設(shè)計(jì)

寫控制單元主要的功能是根據(jù)寫數(shù)據(jù)有效信號wdataen判斷輸入數(shù)據(jù)是否正確,,在檢測到寫入數(shù)據(jù)幀的開始標(biāo)志位wsof后開始計(jì)數(shù)控制寫指針waddr的移動,,將正確的數(shù)據(jù)寫入DUAL PORT RAM中,并在一幀數(shù)據(jù)寫滿后向讀控制單元發(fā)出寫數(shù)據(jù)滿幀信號wframe,。為防止亞穩(wěn)態(tài)的出現(xiàn),,設(shè)計(jì)中采取了兩個措施:一是采用鎖存器將幀頭信號wsof拉長,確保其被穩(wěn)定的采集,;二是采用Gray編碼計(jì)數(shù)器替代普通二進(jìn)制編碼計(jì)數(shù)器來控制寫指針waddr的移動,,因?yàn)镚ray碼相鄰兩個編碼之間有且只有1位發(fā)生變化從而抑制了競爭冒險的出現(xiàn)。

2.2 同步器設(shè)計(jì)

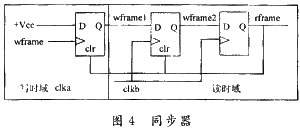

寫控制單元發(fā)出的寫數(shù)據(jù)滿幀信號wframe屬于控制信號,,他從寫時域進(jìn)入讀時域必須采用同步器實(shí)現(xiàn)信號同步,,將寫時域的滿幀信號wframe變換為讀時域的滿幀信號rframe。由于信號是從高時鐘域(66 MHz)流向低時鐘域(40 MHz),,因此采用如圖4所示的同步器,。

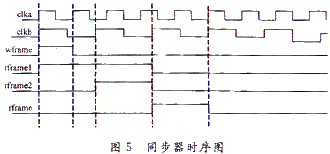

同步器時序圖如圖5所示,可見在寫時域的滿幀信號wframe經(jīng)過3個clka周期延后跨越到讀時鐘域,。

2.3 讀控制單元設(shè)計(jì)

數(shù)據(jù)從寫時域傳遞到讀時域,,時鐘發(fā)生了變化,而且讀控制單元的行為受到寫控制單元及Dual Port RAM中數(shù)據(jù)的存儲情況的雙重制約,,因此他的設(shè)計(jì)是整個芯片設(shè)計(jì)成功的關(guān)鍵,。

由于當(dāng)Dual Port RAM中寫入一幀完整的正確數(shù)據(jù)后才能輸出,所以讀控制首先必須判斷Dual Port RAM一幀是否寫滿,。榆測到滿幀信號rframe后,,在等待輸出數(shù)據(jù)幀頭信號rfp到來后控制讀指針waddr移動讀出數(shù)據(jù),并置位rvalid表征輸出數(shù)據(jù)的可靠性,。

部分程序沒計(jì)如下:

3 多時鐘域數(shù)據(jù)傳遞的FPGA實(shí)現(xiàn)

設(shè)計(jì)方案完成后選用Xilinx Spartan-II FPGA實(shí)現(xiàn)電路,,并在Xilinx ISE6.0集成環(huán)境下用Modelsim5.7進(jìn)行了電路仿真。

圖6為寫使能信號dataen恒為有效值“1”的仿真結(jié)果截圖,。

可見,,在寫使能信號dataen恒為有效值“1”的情況下,,在寫時鐘clka控制下當(dāng)寫數(shù)據(jù)幀頭信號sof有效時,寫控制器開始寫入數(shù)據(jù),,接收到連續(xù)8個數(shù)據(jù)后,,寫控制器發(fā)出一個幀滿信號wframe。wframe信號經(jīng)過異步轉(zhuǎn)換后轉(zhuǎn)換成clkb時鐘域的信號,。在讀控制器的控制下,,當(dāng)clkb時鐘處于上升沿,并且檢測到讀出數(shù)據(jù)幀頭fp時,,開始從outdata向外發(fā)送數(shù)據(jù),,并將valid置為有效。

圖7為當(dāng)寫使能信號dataen變化時的仿真結(jié)果截圖,。

可見,,將dataen置低后,系統(tǒng)不再接受寫入數(shù)據(jù),,所以也不再輸出數(shù)據(jù),,valid被置為低電平,輸出數(shù)據(jù)無效,。寫控制的使能端控制達(dá)到要求,。

4 結(jié) 語

針對異步并行通信接口芯片設(shè)計(jì)中涉及的多時鐘域的數(shù)據(jù)傳遞問題,本文采用FIFO存儲器來完成不同時鐘域之間數(shù)據(jù)流傳遞,、同步器來完成控制信號傳遞的方案,。仿真驗(yàn)證結(jié)果表明,數(shù)據(jù)傳遞準(zhǔn)確,、穩(wěn)定,、可靠,沒有出現(xiàn)競爭冒險和亞穩(wěn)態(tài),,完全達(dá)到了設(shè)計(jì)要求。