引言

近年來,由于電力電子裝置等非線性負(fù)荷的大量增加,電力系統(tǒng)的諧波污染越來越嚴(yán)重,嚴(yán)重地影響了電能計(jì)量的準(zhǔn)確性和合理性,由此導(dǎo)致的糾紛也屢見不鮮。因此,研究用于電能計(jì)量的諧波電壓源裝置,對(duì)電能計(jì)量有著非常重要的意義。

要求用于電能計(jì)量的諧波電壓源能模擬21次內(nèi)任意諧波的疊加,因此對(duì)采樣頻率要求較高。

目前,絕大多數(shù)諧波電壓源裝置采用開關(guān)功率放大器作為主電路,利用數(shù)字信號(hào)處理器(DigitalSignal Processing,DSP) 作為控制芯片。電力電子模型屬于典型的高度并行模型,沒有復(fù)雜的控制過程,但對(duì)采樣率要求很高。開關(guān)器件的開關(guān)頻率可達(dá)數(shù)百kHz,開關(guān)周期為μs 量級(jí),實(shí)時(shí)系統(tǒng)要能穩(wěn)定工作,其采樣周期應(yīng)小于開關(guān)周期的1 /10,DSP 則就有些顯得力不從心了。

現(xiàn)場(chǎng)可編程門陣列(Field Programrnable GateArray,FPGA)采樣率很高,適用于高速度要求的并行運(yùn)算,運(yùn)算過程簡(jiǎn)單。采用FPGA 執(zhí)行運(yùn)算,不僅能提高采樣精度,還能節(jié)約成本。近年來,隨著技術(shù)進(jìn)步及市場(chǎng)需求量的增加,F(xiàn)PGA 產(chǎn)品單位貨幣所買到的MAC(乘法/累加運(yùn)算)數(shù)比傳統(tǒng)的DSP 還要高。200 萬門FPGA 可達(dá)到1 280 億/s MAC 的性能,比目前最快的DSP 性能還高一個(gè)量級(jí),有取代DSP 之勢(shì)。因此,將FPGA應(yīng)用于諧波電壓源的研究中,不失為一種好的思路。

VHS-ADC 是基于Matlab /Simulink 和FPGA的高速數(shù)字信號(hào)處理平臺(tái),采用Virtex-Ⅱ系列FPGA,內(nèi)部擁有豐富的門資源與硬件乘法器,工作頻率可達(dá)420 MHz,高速A/D 通道采樣率可達(dá)105 MS /s,高速D/A 通道采樣率可達(dá)125 MS /s。VHS-ADC 實(shí)現(xiàn)了與Simulink 的無縫連接。

本文在分析系統(tǒng)原理和設(shè)計(jì)系統(tǒng)參數(shù)基礎(chǔ)上,在Simulink 中搭建了諧波電壓源的連續(xù)域模型,并將其離散化,基于VHS-ADC 平臺(tái)搭建了離散域仿真模型。

1 主電路結(jié)構(gòu)和控制策略

1. 1 諧波電壓源的主電路結(jié)構(gòu)

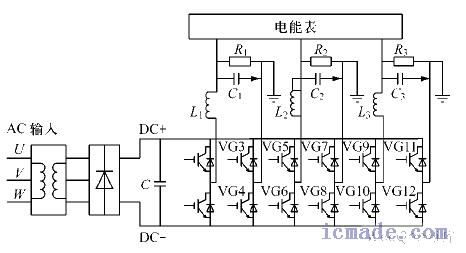

諧波電壓源裝置可模擬電網(wǎng)的各種現(xiàn)場(chǎng)情況,每相的諧波含量各不相同,因此主電路逆變部分采用3 個(gè)單相H 橋,每個(gè)單相H 橋由4 個(gè)開關(guān)管IGBT 組成。諧波電壓源裝置的主電路圖如圖1 所示。其中,每個(gè)H 橋可以等效為一個(gè)可控電壓源,為系統(tǒng)提供頻率、幅值、相位可調(diào)的諧波電壓。逆變部分由4 個(gè)開關(guān)管IGBT 組成,逆變部分的直流側(cè)電壓由整流部分提供。整流部分由降壓變壓器和三相不可控整流電路組成,三相市電由降壓變壓器降壓隔離,再經(jīng)三相不可控整流,得到逆變電路所需的穩(wěn)定直流電壓。出口處的電感電容構(gòu)成單調(diào)濾波器,用于濾除載波和高次諧波。

圖1 諧波電壓源裝置主電路。

1. 2 諧波電壓源的控制策略

雙閉環(huán)PI 調(diào)節(jié)的控制器簡(jiǎn)單,具有一定的魯棒性,在工程控制領(lǐng)域得以廣泛應(yīng)用。因此,本文采用基于SPWM 的雙閉環(huán)PI 控制策略,雙閉環(huán)PI 控制的原理框圖如圖2 所示。圖2 中,外環(huán)電壓以理想的正弦波作為參考電壓,輸出電壓與參考電壓比較后經(jīng)PI 調(diào)節(jié)作為電流內(nèi)環(huán)的參考值,該電流參考值與反饋電流比較,再經(jīng)PI 調(diào)節(jié)后與PWM 控制器中的三角波比較,產(chǎn)生PWM 信號(hào)驅(qū)動(dòng)逆變器。

圖2 電壓、電流雙閉環(huán)PI 控制原理框圖。

本文引入負(fù)載電壓瞬時(shí)值和濾波電容電流瞬時(shí)值作為反饋信號(hào),根據(jù)實(shí)際值和期望值的偏差來實(shí)時(shí)控制輸出電壓波形,保證輸出電壓波形的精度,消除各種非正弦因素和擾動(dòng)對(duì)輸出電壓的影響。由于輸出濾波電容電流是對(duì)逆變器輸出電壓的微分,十分微小的電壓變化即可引起電容電流的較大波動(dòng)。因此,電容電流的引入更能使系統(tǒng)得到良好的動(dòng)態(tài)性能。

2 基于VHS-ADC 平臺(tái)的系統(tǒng)建模

基于FPGA 的VHS-ADC 高速信號(hào)處理平臺(tái),其模型庫具有豐富的數(shù)字信號(hào)處理模型,Simulink自帶的模型庫不能編譯成FPGA 代碼,而Xilinx模型庫是基于離散信號(hào)z 域的模型。因此,需要構(gòu)建z 域電力電子仿真模型。

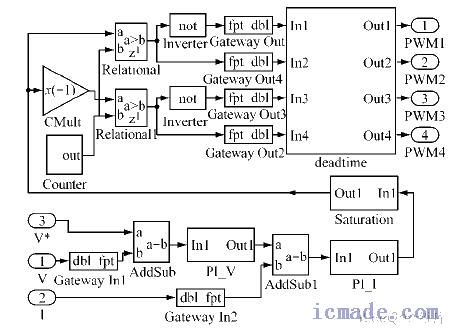

基于z 域的控制電路VHS-ADC 模型如圖3所示。該模型主要由PWM 發(fā)生器、PI 控制模塊、限幅模塊和死區(qū)模塊組成。三角波用Counter 計(jì)數(shù)器產(chǎn)生。圖3 中的Gateway in 為數(shù)據(jù)轉(zhuǎn)化模塊,將s 域信號(hào)轉(zhuǎn)化為z 域信號(hào)。

圖3 控制電路VHS-ADC 模型。

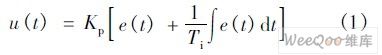

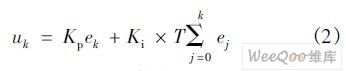

電壓外環(huán)PI 環(huán)節(jié)可表示為:

式中u(t)———控制量

e(t)———系統(tǒng)的控制偏差

Ti———積分時(shí)間

Kp———比例系數(shù)

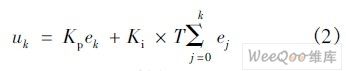

為了搭建離散域模型,在近似條件下得離散化方程為:

式中T———采樣周期

k———采樣序號(hào),k = 1,2,…

e(k)———PI 環(huán)節(jié)的輸入信號(hào)

Ki = Kp /Ti———積分系數(shù)

將式(2) 與uk - 1的表達(dá)式進(jìn)行比較,則可得到第k 次采樣時(shí)刻的離散方程:

根據(jù)PI 的離散方程,可構(gòu)建VHS-ADC 模型。

以電壓外環(huán)PI 為例,其模型如圖4 所示。CMult為乘法器模塊,大小等于采樣時(shí)間T;Convert 為數(shù)據(jù)轉(zhuǎn)化模塊,將輸入信號(hào)轉(zhuǎn)化為合理的數(shù)據(jù)格式。數(shù)據(jù)格式由數(shù)據(jù)位數(shù)和小數(shù)位數(shù)確定,在保證仿真精度的前提下,盡量減小數(shù)據(jù)位數(shù),節(jié)約硬件資源。

圖4 電壓外環(huán)PI 模型。

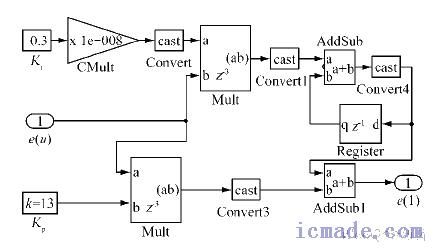

利用3 個(gè)加法器和1 個(gè)減法器,可實(shí)現(xiàn)限幅環(huán)節(jié)。減法器運(yùn)算結(jié)果為負(fù)時(shí),輸出為0;運(yùn)算結(jié)果為正時(shí),輸出為正常值。Constant1 和Constant2分別設(shè)置限幅模塊的上、下限,限幅環(huán)節(jié)的模型如圖5 所示。

圖5 限幅環(huán)節(jié)模型。

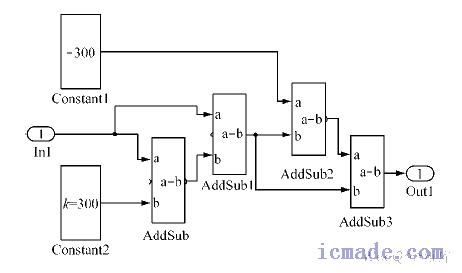

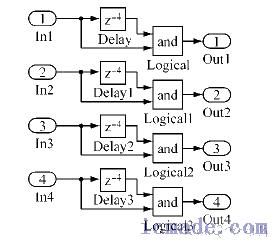

利用延遲模塊和邏輯模塊,可設(shè)置逆變器死區(qū)時(shí)間。輸入信號(hào)經(jīng)過Delay 模塊,被延遲4 個(gè)采樣周期時(shí)間,再與原信號(hào)進(jìn)行邏輯與運(yùn)算,就可得到帶有死區(qū)時(shí)間的PWM 信號(hào),被Delay 模塊延遲的時(shí)間就是設(shè)置的死區(qū)時(shí)間。死區(qū)時(shí)間模型如圖6 所示。

圖6 死區(qū)時(shí)間的VHS-ADC 模型。

依靠平臺(tái)提供的co-simulink 接口,將搭建的離散域控制模型進(jìn)行編譯,并自動(dòng)生成代碼,下載到FPGA,生成一個(gè)bit 流文件,將含有bit 文件的協(xié)議同仿真模塊與諧波電壓源的主電路連接。當(dāng)在Simulink 中進(jìn)行仿真時(shí),F(xiàn)PGA 上的實(shí)時(shí)運(yùn)算結(jié)果返回到Simulink 環(huán)境中,提高了仿真速度。

3 仿真結(jié)果

利用Matlab /Simulink 軟件和VHS-ADC 仿真平臺(tái),建立完整的諧波電壓源仿真模型。仿真參數(shù):輸入電壓為Uu = Uv = Uw = 220 V;濾波電感L = 0. 05 mH,濾波電容C = 100 μF。電壓環(huán)PI 參數(shù):比例系數(shù)Kp = 13,Ki = 0. 4;電流環(huán)PI 參數(shù):比例系數(shù)Kp = 15,Ki = 0. 2,負(fù)載R = 30 Ω;采樣時(shí)間為100 ns,單相額定輸出功率為3 kVA。

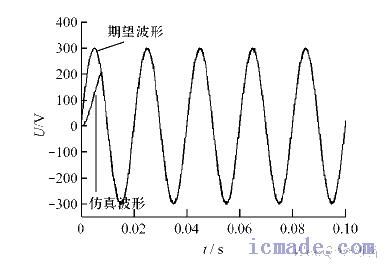

穩(wěn)態(tài)下,諧波電壓源輸出的單相基波波形如圖7 所示。因?yàn)槿嗖豢煽卣魈峁┑闹绷麟妷盒枰s0. 01 s 才能達(dá)到穩(wěn)定,所以諧波電壓源輸出波形在0. 01 s 之前是逐漸增大的,當(dāng)直流電壓穩(wěn)定后,仿真波形幾乎與期望波形重合。

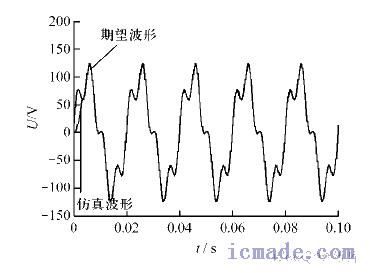

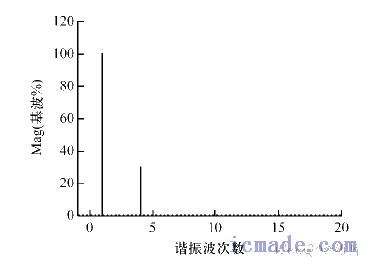

為了驗(yàn)證裝置的諧波合成能力,將30 V 4 次諧波疊加到100 V 基波上,如圖8 所示。疊加后的波形在0. 01 s 前逐漸增大,在0. 01 s 后幾乎與期望波形重疊;將所得波形進(jìn)行傅里葉分析,4 次諧波含量為基波的30%,其頻譜分析圖如圖9 所示。

圖7 基波輸出波形與期望波形的對(duì)比。

圖8 疊加信號(hào)輸出波形與期望波形的對(duì)比。

圖9 疊加波形的頻譜圖。

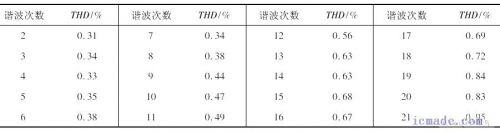

表1 為輸出波形為單次諧波時(shí),總諧波畸變率(THD)的大小。仿真結(jié)果表明,諧波電壓源輸出21 次內(nèi)的單次諧波時(shí),其THD 不會(huì)超過1%。

上述仿真結(jié)果說明了諧波電壓源輸出波形具有很高的精度,同時(shí)也驗(yàn)證了諧波電壓源離散域模型的正確性。

表1 諧波電壓源輸出單次諧波時(shí)的畸變率。

4 結(jié)語

分析了諧波電壓源的主電路模型,探討了基于濾波電容電流和負(fù)載電壓瞬時(shí)值的雙閉環(huán)PI控制策略,利用VHS-ADC 數(shù)字信號(hào)處理系統(tǒng)采樣率高、實(shí)時(shí)性強(qiáng)、建模靈活等特點(diǎn),構(gòu)建離散域?qū)崟r(shí)仿真控制模型。仿真結(jié)果表明,該設(shè)計(jì)方法和離散化模型是正確的,說明了基于FPGA 進(jìn)行諧波電壓源研究的可行性。