20多年來(lái),研究人員和半導(dǎo)體制造商一直在試圖開(kāi)發(fā)一種針對(duì)混合信號(hào)IC的實(shí)用模擬BIST(內(nèi)置自檢),。這種技術(shù)能夠用數(shù)字測(cè)試儀作混合信號(hào)IC測(cè)試,,以及簡(jiǎn)化的多址測(cè)試,從而能減少I(mǎi)C測(cè)試成本,,以及IC上市時(shí)間,。其它預(yù)期優(yōu)點(diǎn)還有更快的測(cè)試開(kāi)發(fā),以及系統(tǒng)上的自檢等,。

大多數(shù)IC設(shè)計(jì)工程師都了解數(shù)字BIST的工作原理,。它用一個(gè)LFSR(線性反饋移位寄存器)生成偽隨機(jī)的位模式,并通過(guò)臨時(shí)配置成串行移位寄存器的觸發(fā)器,,將這個(gè)位模式加到待測(cè)電路上,。數(shù)字BIST亦用相同的觸發(fā)器捕獲響應(yīng),將移出的結(jié)果壓縮成一個(gè)數(shù)字標(biāo)志,,再將其與一個(gè)正確的標(biāo)志作逐位對(duì)比,。盡管工業(yè)邏輯BIST的細(xì)節(jié)要更復(fù)雜,但基本原理仍適用于多時(shí)鐘域,、多周期延遲路徑,,以及電源軌噪聲等。

不過(guò),,大多數(shù)工程師仍然難以理解模擬BIST的原理,,尤其是模擬電路設(shè)計(jì)者。這件事在2009年設(shè)計(jì)自動(dòng)化研討會(huì)上又被證實(shí),,當(dāng)時(shí)一名有經(jīng)驗(yàn)的PLL(鎖相環(huán))電路設(shè)計(jì)者問(wèn)道:“如果你用于PLL的BIST如此精確,,為什么你不設(shè)計(jì)PLL呢?”要回答這個(gè)問(wèn)題,,首先必須了解實(shí)用模擬BIST的原理,。

如何定義“模擬”?

“模擬”電路對(duì)不同的人有不同的含義,。一個(gè)PLL或SERDES(串行器/解串器)可以看作是數(shù)字的,,模擬的,或混合信號(hào)的,。對(duì)這些單元的BIST測(cè)試可以是純數(shù)字的,,因?yàn)檫@些功能只有數(shù)字輸入和輸出,。例如,有些IC會(huì)用片上的頻率計(jì)數(shù)器來(lái)測(cè)量PLL的輸出頻率,,它是用一個(gè)基準(zhǔn)頻率的已知周期數(shù),,統(tǒng)計(jì)振蕩的周期數(shù),如果計(jì)數(shù)中的任何位不同于期望值,,則測(cè)試就失敗,。很多用于測(cè)試IC SERDES收發(fā)器性能的方法是采用環(huán)回的偽隨機(jī)數(shù)據(jù),如檢測(cè)到一個(gè)誤碼就認(rèn)為失敗,。然而,,測(cè)試ADC或DAC這類(lèi)模擬電路時(shí),顯然要求BIST電路可以生成或捕獲模擬信號(hào),,即瞬時(shí)電壓總是相關(guān)的信號(hào),。傳統(tǒng)的模擬電路(如濾波器和線性穩(wěn)壓器)都有模擬輸入與輸出,不過(guò)很多都有數(shù)字控制的信號(hào)或時(shí)鐘,。最純粹的模擬電路(如RF電路)可能根本沒(méi)有數(shù)字信號(hào),。

在測(cè)試時(shí),模擬電路至少要有一個(gè)非確定性瞬態(tài)電壓的信號(hào),。測(cè)試包括對(duì)信號(hào)的檢查,,是在兩個(gè)電壓之間,是數(shù)字值,,還是時(shí)間閾值,;還要檢查信號(hào)統(tǒng)計(jì)值是否在極限內(nèi);或檢查一個(gè)有關(guān)信號(hào)的算術(shù)運(yùn)算值是否在極限之間,。對(duì)所有具備任何模擬信號(hào)的電路,,都應(yīng)采用模擬測(cè)試原理。

純數(shù)字電路的響應(yīng)是確定性的,,因此,,一個(gè)可接受的輸出信號(hào)只需要采樣一次。不過(guò),,如果能看到數(shù)字電路信號(hào)足夠多的細(xì)節(jié),,如毫伏或皮秒量級(jí),則所有電路都是模擬的,。在納米級(jí)CMOS工藝時(shí),,這種考慮尤其不能忽視,因?yàn)閷?duì)于1V電源軌以及亞納秒級(jí)時(shí)鐘周期,,電源軌噪聲、抖動(dòng),、溫度以及參量變動(dòng)都有顯著的影響,。測(cè)試模擬電路的BIST電路容易受這些效應(yīng)影響,,哪怕BIST幾乎是全數(shù)字的,因此,,很多模擬設(shè)計(jì)者都想了解模擬BIST如何比相同芯片上的模擬電路更精確,。

設(shè)計(jì)模擬BIST的挑戰(zhàn)

設(shè)計(jì)用于模擬電路的BIST要比精確提供和捕捉模擬信號(hào)更加復(fù)雜。信號(hào)變動(dòng)與需要測(cè)量的參數(shù)都要比數(shù)字BIST處理的邏輯0和邏輯1要多得多,。模擬激勵(lì)與響應(yīng)可以從直流電壓,、線性斜坡以及脈沖,直到正弦波與頻率調(diào)制,。激勵(lì)與響應(yīng)可能還屬于不同的域,,從而使挑戰(zhàn)更加復(fù)雜化。例如,,一個(gè)DC電壓輸入可能產(chǎn)生一個(gè)頻率輸出,。挑戰(zhàn)中還增加了需要分析的各種參數(shù),它們可能包括幅度,、相位延遲,,以及SNR(信噪比),還有DC電壓,、峰峰抖動(dòng),,以及占空比。

測(cè)試設(shè)備一般必須比待測(cè)電路精度高一個(gè)數(shù)量級(jí),。于是,,最令人生畏的模擬BIST挑戰(zhàn)就是:如何經(jīng)濟(jì)地實(shí)現(xiàn)比待測(cè)電路更高的精度,而后者很可能已經(jīng)實(shí)現(xiàn)了在其硅片面積與技術(shù)下的最佳精度,。信號(hào)幅度的范圍可能非常巨大,。ADC與DAC可以處理動(dòng)態(tài)范圍高達(dá)224的片上模擬信號(hào),相當(dāng)于8個(gè)數(shù)量級(jí),。

數(shù)字BIST可以比作一個(gè)正在給自己的多項(xiàng)選擇測(cè)試打分的學(xué)生,。他將一個(gè)模板放在答題紙上,統(tǒng)計(jì)正確答案數(shù),。另一方面,,模擬BIST則可以比做一個(gè)正在做作文考試的學(xué)生。這不是一個(gè)簡(jiǎn)單而客觀的過(guò)程?,F(xiàn)在,,考慮到實(shí)用模擬BIST所必須應(yīng)用的基礎(chǔ)電路原理,應(yīng)可以了解挑戰(zhàn)的量級(jí)了,。

基礎(chǔ)電路原則

第一個(gè)原則是,,通過(guò)施加時(shí)序不敏感的數(shù)字測(cè)試模式、時(shí)鐘以及DC電壓,測(cè)試機(jī)制本身必須是可測(cè)的,,而無(wú)需片外的線性AC信號(hào)或測(cè)量,。ATE(自動(dòng)測(cè)試設(shè)備)在離開(kāi)工廠前,要做大量的校準(zhǔn)與測(cè)試,。要讓BIST成為混合信號(hào)ATE的替代方案,,就必須在使用前作校準(zhǔn)與測(cè)試。采用基于掃描的測(cè)試,,模擬BIST電路的純數(shù)字部分應(yīng)是可測(cè)的,,包括邏輯BIST。如果數(shù)字電路包含了延遲線或延遲匹配線路,,則應(yīng)測(cè)試這些延遲和延遲增量,。測(cè)量一個(gè)延遲的方法是:將延遲線包含或配置到一個(gè)回路振蕩器中,并用片上頻率計(jì)數(shù)器測(cè)量其振蕩頻率,。

對(duì)模擬BIST中純 模擬部分的測(cè)試則更復(fù)雜,。有些研究人員建議在自己的模擬BIST中使用一個(gè)ADC或DAC,暗含著ATE可以測(cè)試它的假設(shè),;然而,,混合信號(hào)ATE仍將是必要的,因此削弱了BIST的很多優(yōu)勢(shì),。

也許最陳舊的BIST技術(shù)就是將一個(gè)DAC輸出連回到一個(gè)ADC輸入,,或?qū)⒁粋€(gè)調(diào)制器輸出連到一個(gè)解調(diào)器輸入,以此完成整個(gè)數(shù)字測(cè)試,。這種方法仿佛是用一個(gè)未經(jīng)測(cè)試的電路,,去測(cè)試另外的電路,對(duì)補(bǔ)償失誤不敏感,。例如,,對(duì)于ADC中補(bǔ)償?shù)南嗨品蔷€性,DAC的非線性則可能過(guò)高,,因?yàn)閮烧咭黄鹨糜谌魏螁为?dú)一個(gè),。

模擬BIST的第二個(gè)原則是欠采樣,即慢于Nyquist速率的采樣,,這意味著采樣速率要低于最高頻率的兩倍——這對(duì)于較慢地分析一個(gè)信號(hào)是必需的,。較慢的采樣還有利于使BIST電路小于待測(cè)電路。

在有些自校準(zhǔn)方法中,,會(huì)用一個(gè)低速ADC去欠采樣一只高速ADC或DAC的模擬信號(hào),。一級(jí)sigma-delta調(diào)制器是小而簡(jiǎn)單的模擬電路,如果帶寬降低就可以將模擬信號(hào)轉(zhuǎn)換為任意分辨率的數(shù)字碼流,。調(diào)制器可以采樣一個(gè)1600萬(wàn)次/秒的信號(hào),,產(chǎn)生1600個(gè)1 bit的采樣,;調(diào)制器可以對(duì)這些采樣作數(shù)字濾波,產(chǎn)生100萬(wàn)個(gè)4位分辨率采樣/秒,,或16000個(gè)16 位采樣/秒,,每種情況都將可用帶寬減少至1/16。欠采樣可以讓一個(gè)較窄的興趣帶寬定位于原始信號(hào)頻率的中心,,使其轉(zhuǎn)換為一個(gè)低的頻率,從而更便于做分析,。不過(guò),,欠采樣也要付出混疊效應(yīng)的代價(jià),這是必須考慮的,。

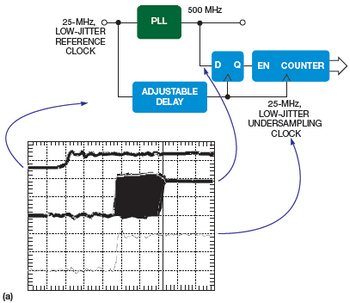

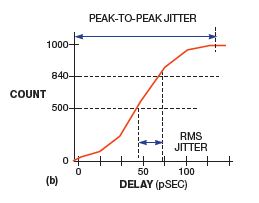

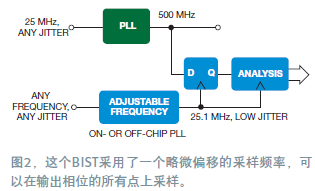

另一個(gè)采樣的例子是一個(gè)PLL BIST,,它使用PLL的輸入基準(zhǔn)時(shí)鐘沿,去采樣PLL的輸出(圖1a),。此時(shí),,一個(gè)基準(zhǔn)通過(guò)一個(gè)可調(diào)延遲線,為一只鎖存器提供時(shí)鐘,,鎖存器完成采樣工作,。假設(shè)鎖存器的輸出計(jì)數(shù)1000個(gè)時(shí)鐘周期,然后延遲遞增,。這個(gè)動(dòng)作不斷重復(fù),,直到鎖存器獲得了累加的分布函數(shù)(圖1b)。PLL的輸出頻率可以比其基準(zhǔn)頻率高出很多倍,。這種BIST不能檢測(cè)到基準(zhǔn)時(shí)鐘沿之間的抖動(dòng),,但另外一種采用略微偏移的采樣頻率的技術(shù),可以在輸出相位的所有點(diǎn)上作采樣(圖2),。

圖1,,PLL BIST使用PLL的輸入基準(zhǔn)時(shí)鐘沿,采樣PLL的輸出 (a),。一個(gè)基準(zhǔn)通過(guò)一根可調(diào)延遲線,,為一個(gè)鎖存器提供時(shí)鐘,鎖存器完成采樣工作,。鎖存器的輸出計(jì)數(shù)1000個(gè)時(shí)鐘周期,,然后延遲遞增。這個(gè)動(dòng)作不斷重復(fù),,直到鎖存器獲得了累積分布函數(shù) (b),。

這兩種技術(shù)表示了時(shí)間測(cè)量的一個(gè)重要原則:控制一個(gè)信號(hào)被采樣的時(shí)間時(shí),要么是一個(gè)來(lái)自可調(diào)延遲的恒定時(shí)間偏移,,要么是來(lái)自一個(gè)可調(diào)振蕩器的恒定頻率偏移,,如PLL。在實(shí)現(xiàn)納米CMOS時(shí),低抖動(dòng)延遲越來(lái)越困難,,但低抖動(dòng)頻率偏移卻越來(lái)越容易實(shí)現(xiàn),。

模擬BIST的另一個(gè)原則通過(guò)減去系統(tǒng)誤差來(lái)提高精度。例如,,當(dāng)測(cè)量電壓時(shí),,必須消除任何比較器或運(yùn)算放大器的偏移電壓。如果這些電路有可忽略的偏移,,則必須測(cè)量該偏移,,以驗(yàn)證它確實(shí)是可忽略的;否則,,就必須減去它的值,。比較簡(jiǎn)單的方法是假設(shè)該偏移較大,將其減掉,。當(dāng)測(cè)量延遲時(shí),,必須從輸出的延遲中,減去待測(cè)電路輸入端的測(cè)試接入路徑延遲,,以確保消除了接入路徑的延遲,。ATE通常采用乘法和減法,做模擬自校準(zhǔn),,但這種運(yùn)算需要太多電路,,對(duì)BIST并不經(jīng)濟(jì)。當(dāng)系統(tǒng)誤差上下起伏時(shí),,可能會(huì)出現(xiàn)低頻效應(yīng),,如由于電力線噪聲而使偏移以50 Hz或60 Hz變化。

通過(guò)增加采樣來(lái)計(jì)算均值,,可以提高精度,。一個(gè)信號(hào)或測(cè)量電路中的隨機(jī)噪聲限制了對(duì)任何信號(hào)特性測(cè)量的可重復(fù)性。當(dāng)在一次測(cè)量中包含了更多的采樣時(shí),,就改善了測(cè)量的變動(dòng)與可重復(fù)性,。模擬測(cè)量電路實(shí)現(xiàn)均化的方法一般是用低通濾波,或用一個(gè)電容做電荷積分,。

可以在模擬BIST的數(shù)字電路中使用全加法器,,但很多情況下,用二進(jìn)制計(jì)數(shù)器可以更高效地實(shí)現(xiàn)均化,。用簡(jiǎn)單的均化或減法都無(wú)法抑制掉非隨機(jī)的噪聲,,例如來(lái)自鄰近同步邏輯或60 Hz電力線的干擾。不過(guò),,可以通過(guò)與干擾的同步采樣(參考文獻(xiàn)1),,或?qū)Ω蓴_頻率作整數(shù)周期的積分,,從而降低其影響。

為獲得成本效益,,BIST電路必須有高于待測(cè)電路的成品率,。對(duì)于數(shù)字BIST的情況,這種要求只是意味著其面積必須小于待測(cè)電路面積,。然而對(duì)于模擬BIST,,這一原則還意味著B(niǎo)IST必須在不影響成品率情況下,實(shí)現(xiàn)所需要的線性度,、噪聲以及帶寬,。在一項(xiàng)研究中,一個(gè)測(cè)試芯片上只有70%的小型模擬BIST電路可以實(shí)現(xiàn)所需要的測(cè)量精度,。該BIST的成品率對(duì)SoC(系統(tǒng)單芯片)的影響等同于電路占整個(gè)SoC的30%情況。

使BIST的成品率高于待測(cè)模擬電路的最佳方式是盡可能減少BIST中的模擬電路數(shù)量,,即使其數(shù)字化,。通過(guò)在多個(gè)功能之間共享一個(gè)BIST電路,可以減少與BIST電路有關(guān)的面積,。數(shù)字BIST可以很容易實(shí)現(xiàn)這一任務(wù),,但模擬BIST則相反,因?yàn)樾枰獪y(cè)試的功能之間存在差異性,。這就是MadBIST建立的原因,,這種方法由MF Ton er和Gordon W Roberts共同開(kāi)發(fā)(參考文獻(xiàn)2)。采用MadBIST時(shí),,一只DSP首先測(cè)試一只ADC然后才是DAC,。MadBIST、ADC和DAC,,然后再測(cè)試其它模擬電路,。

采用共享分析塊有一個(gè)問(wèn)題,即將感興趣的模擬信號(hào)傳送給分析塊,。完成這個(gè)工作一般采用模擬總線,,但它們會(huì)帶來(lái)負(fù)載、噪聲和非線性,,并且會(huì)減小帶寬,。一種替代方法是在本地將信號(hào)轉(zhuǎn)換為某種數(shù)字表述,然后采用一個(gè)數(shù)字總線,。

模擬BIST必須能夠采用基于規(guī)范的結(jié)構(gòu)化測(cè)試,。換句話說(shuō),所做激勵(lì)與響應(yīng)分析的結(jié)果,,必須能與模擬電路的功能規(guī)范作校對(duì),,但它們也必須面向制造缺陷,,幫助做診斷,并盡可能減少測(cè)試時(shí)間,。面向缺陷的測(cè)試有助于完成這個(gè)任務(wù),,但一般不會(huì)嘗試使用仿功能測(cè)試。飛利浦(現(xiàn)在的恩智浦公司)在1995年首先在基于規(guī)范的傳統(tǒng)模擬測(cè)試與面向缺陷的測(cè)試之間做了一個(gè)公開(kāi)的行業(yè)對(duì)比(參考文獻(xiàn)3),。結(jié)論是:當(dāng)設(shè)計(jì)規(guī)范有更大的裕度,,并且過(guò)程得到良好的控制時(shí),面向缺陷的測(cè)試能對(duì)相近的缺陷覆蓋實(shí)現(xiàn)更快的測(cè)試,。另一方面,,基于規(guī)范的測(cè)試對(duì)保持測(cè)試覆蓋和成品率都是必要的。

數(shù)字BIST天然地就采用一種仿功能的激勵(lì),,因?yàn)閹缀跞魏?和0的模式都能表示功能模式下的輸入信號(hào),,包括偽隨機(jī)數(shù)據(jù)。而為模擬電路提供一種仿功能激勵(lì)則可能復(fù)雜得多,。偽隨機(jī)噪聲是一個(gè)誘人的模擬激勵(lì),,它能處理很多潛在的缺陷,并且易于生成,。一只電阻和一只電容就可以對(duì)數(shù)字BIST中的LFSR輸出做濾波,,產(chǎn)生一個(gè)模擬波形。乘法器和加法器可以將待測(cè)模擬電路的響應(yīng)與其偽隨機(jī)輸入做交叉關(guān)聯(lián),。

另外一種更容易實(shí)現(xiàn)的方案是,,將電路輸出端連接到輸入端,必要時(shí)增加增益或反相,,從而將電路重新配置為一個(gè)振蕩器,,并測(cè)量其振蕩頻率。這種技術(shù)具有面積效率,。不幸的是,,這兩種方案都被證明難以使用,因?yàn)闇y(cè)量對(duì)于噪聲和非線性都太不敏感,,而診斷也不實(shí)用,。

ATE廣泛采用一種線性斜坡與單音正弦波作為測(cè)試激勵(lì),從而有效地測(cè)試ADC和DAC的線性度,,并作診斷輔助,。在片上產(chǎn)生一個(gè)純斜坡或正弦波的最強(qiáng)大方式是在一個(gè)循環(huán)移位寄存器中存儲(chǔ)一個(gè)周期性的sigma-delta碼流,不過(guò)這種方案可能需要數(shù)千個(gè)邏輯門(mén),,外加模擬濾波,。所幸的是,一個(gè)激勵(lì)塊可能就足以應(yīng)付一片SoC中的所有模擬功能,,并且可以有效地將串行數(shù)字碼流送給芯片的各個(gè)區(qū)域,。

激勵(lì)生成的最簡(jiǎn)單而有用的信號(hào)是一個(gè)數(shù)字方波,,可以用它去測(cè)量一個(gè)步長(zhǎng),或一個(gè)脈沖響應(yīng),。令人驚訝的是,,對(duì)于一個(gè)用于生成波形的采樣比較器來(lái)說(shuō),精確DC電壓是一種困難的激勵(lì)或基準(zhǔn),,除非求助于需要更多自測(cè)的模擬技術(shù),。對(duì)一個(gè)占空比可編程的數(shù)字波形做低通濾波,可以產(chǎn)生一個(gè)基本上是DC的波形,,其平均電壓取決于占空比,,并且在高開(kāi)關(guān)頻率時(shí),平均電壓還取決于數(shù)字信號(hào)上升和下降時(shí)間的不匹配度,。

降低開(kāi)關(guān)頻率,,就降低了DC電壓對(duì)這種不匹配的敏感度,但增加了DC電壓的峰峰變動(dòng),。在模擬功能中(如穩(wěn)壓器),,增加有源低通濾波就可以減少這種噪聲。但采用這種方案的模擬BIST必須對(duì)濾波做測(cè)試,。更適合于BIST的是在“高速模擬電路測(cè)試與驗(yàn)證研討會(huì)”上剛剛演示的一種技術(shù)(參考文獻(xiàn)4)。

模擬BIST的最后原則是,,必須通過(guò)與上下測(cè)試極限值的比較,,將其結(jié)果輸出為一個(gè)數(shù)字測(cè)量值以及合格/不合格的比特。如果要將一個(gè)模擬的電壓結(jié)果送至片外做特性描述,,它就可能遭到損壞,,并且可能需要混合信號(hào)ATE。一個(gè)未在片上與極限值比較過(guò)的數(shù)字結(jié)果可能需要用ATE去捕捉和分析數(shù)字字,,而不是單個(gè)比特,,這就不能使用最常見(jiàn)的測(cè)試模式語(yǔ)言WGL(波形生成語(yǔ)言)和STIL(標(biāo)準(zhǔn)測(cè)試界面語(yǔ)言),以及很多低成本的測(cè)試儀,。單有合格/不合格的結(jié)果將無(wú)法確定參數(shù)特性,,也缺乏測(cè)量的可重復(fù)性,而這是設(shè)定測(cè)試極限的一個(gè)基本步驟,。

PL-BIST精度,?

了解了這些基礎(chǔ)原則,有助于回答PLL設(shè)計(jì)者的問(wèn)題,。實(shí)用PLL BIST既沒(méi)有采用模擬電路,,也沒(méi)有使用延遲線,因此它對(duì)噪聲的敏感度弱于待測(cè)PLL,。例如,,PLL必須每納秒生成一個(gè)低抖動(dòng)邊沿,,并盡量減小抖動(dòng)的累積。但是,,PLL BIST可以用一個(gè)預(yù)測(cè)試的低抖動(dòng)時(shí)鐘對(duì)邊沿作欠采樣,,時(shí)鐘通過(guò)幾個(gè)數(shù)字反相器傳送,這些反相器有快速的轉(zhuǎn)換性能,,盡量減少附加的抖動(dòng),。

如果沒(méi)有預(yù)測(cè)試的時(shí)鐘,則PLL可以對(duì)相同芯片上工作在一個(gè)略為異步頻率的其它PLL邊沿作采樣,。獲得的抖動(dòng)測(cè)量結(jié)果是兩個(gè)抖動(dòng)水平之和,;隨機(jī)抖動(dòng)不可能相互抵消。在一個(gè)直方圖中增加很多這類(lèi)采樣,,可以降低寄生噪聲的影響,,并且以與任何干擾相同速率采樣,可以進(jìn)一步降低這種影響,。

模擬BIST的需求

過(guò)去15年來(lái),,很少有什么人提出的模擬BIST技術(shù)包含了上述所有原則。但所有這些原則都是BIST實(shí)用性與性價(jià)比的關(guān)鍵,。開(kāi)發(fā)一種實(shí)用的模擬BIST已被證明有太高的挑戰(zhàn)性,,但工程師們無(wú)疑將開(kāi)發(fā)出一些包含這 些原則的技術(shù),因?yàn)閷?duì)它們的需求在不斷增加,。

SoC中正在加入更多的系統(tǒng)模擬功能,,有更多的管腳數(shù)和門(mén)數(shù),所有這些都推升了測(cè)試時(shí)間與測(cè)試成本,。增加嵌入閃存會(huì)大大增加測(cè)試時(shí)間(遠(yuǎn)不止一分鐘),,從而絕對(duì)需要多址的測(cè)試,這種要求又推動(dòng)了對(duì)低管腳接入以及更多模擬測(cè)試資源的需求,。

阻止采納模擬BIS或任何其它新的模擬測(cè)試技術(shù)的最大障礙是,,缺乏被行業(yè)接受的模擬故障模型。所幸的是,,在2009年國(guó)際測(cè)試會(huì)議上一個(gè)小組討論結(jié)果是,,一些討論成員表達(dá)了對(duì)開(kāi)發(fā)一種IEEE贊助的標(biāo)準(zhǔn)化模擬故障模型的興趣。小組成員還同意,,在行業(yè)可以采用任何新技術(shù)以前,,更多的DFT(可測(cè)試設(shè)計(jì))自動(dòng)化是必要的,這種情形已出現(xiàn)在IC的數(shù)字部分,。只有當(dāng)IC設(shè)計(jì)者采納了系統(tǒng)化的通用技術(shù),,可以測(cè)試一片IC上的多個(gè)功能時(shí),EDA公司才會(huì)開(kāi)發(fā)自動(dòng)化方案,。

參考文獻(xiàn)

1. Sunter, Stephen, and Aubin Roy, “Noise-Insensitive Digital BIST for any PLL or DL,” Journal of Electronic Testing: Theory and Applications, Volume 24, No. 5, pg 461, October 2008.

2. Toner, MF, and Gordon W Roberts, “A BIST Scheme for an SNR Test of a Sigma-Delta ADC,” Proceedings of the International Test Conference, October 1993.

3. Sachdev, Manoj, “A Realistic Defect Oriented Testability Methodology for Analog Circuits,” Journal of Electronic Testing: Theory and Applications, Volume 6, No. 3, pg 265, June 1995.

4. Sunter, Stephen, “A General Strategy for BIST of High- Speed Analog Functions,” Informal Digest of Workshop on Test and Verification of High-Speed Analog Circuits, November 2009.

5. Wilson, Ron, “ITC 2009 panel explores future of analog test,” Test & Measurement World, November 2009.