千兆位級串行I/O技術有著極其出色的優(yōu)越性能,但這些優(yōu)越的性能是需要條件來保證的,即優(yōu)秀的信號完整性。例如,有個供應商報告說,他們第一次試圖將高速、千兆位級串行設計用于某種特定應用時,失敗率為90%。為了提高成功率,我們可能需要進行模擬仿真,并采用更復雜的新型旁路電路。

Spartan-6 FPGA的GTP工作性能取決于PCB的信號完整性,PCB設計過程中需要考慮到以下因素:板的疊層結構,元器件的布局,信號走線。

電源與疊層

針對Spartan-6 FPGA的GTP transceiver,疊層可以分為兩組,電源分布層和信號走線層。電源層用來連接GTP的MGTACC,MGTAVCCPLL,MGTAVTTTX和MGTAVTTRX電源引腳。疊層結構可以參考下圖。

在上圖的疊層中,地平面層位傳輸信號線提供了信號回流路徑。同時,由于在兩信號層中間有屏蔽的平面,在信號走線時就可以不考慮相鄰層走線的所需考慮的問題,并且提供了更多的信號路徑。

GTP的電源層應該與地平面緊密相鄰,增加耦合效果,地平面可以為GTP的電源平面提供屏蔽,屏蔽電源平面來自上一層或下一層信號引起的噪聲干擾。

實際上,從另一個角度考慮,即當電源的噪聲出現(xiàn)在高頻范圍,隨著頻率的增大,越來越難找到電容可以覆蓋此頻率范圍,達到濾波效果,直至不可能找到這樣的電容。隨著電容值的減小,相關的雜散電感和封裝的電阻值并不相應改變,所以頻率響應也不會發(fā)生太大變化。為了在高速情況下實現(xiàn)較好的電源分配,我們需要利用電源層和地層來建構我們自己的電容。為了更有效的達到我們的目的,通常需要使用相鄰的電源層和地層。

GTP的電源管腳和電源分布網(wǎng)絡之間的連接對GTP的工作性能起著很關鍵的作用。PDN,和FPGA需要低阻抗和低噪聲的連接。FPGA的GTP電源容忍最大噪聲為10mVpp,在10KHz到80MHz的范圍內(nèi),電源可以用一個小塊平面。這個小的電源平面不要覆蓋到SelectIO接口的區(qū)域。

電容擺放

旁路電容除了考慮容值大小外,需要考慮的另一重要方面是電容的放置。

一般的規(guī)則是,電容值越大則其放置要求越不嚴格。若電容值較小,則電容應該盡可能靠近電源和地的引腳。可以采用的一種方法是將不用的通用IO的走線和過孔移除,從而為旁路電容騰出空間

GTP的電源分割區(qū)域的位置和GTP濾波電容的位置也可以參考下圖。

信號走線

應該避免GTP信號走線和SelectIO信號走線在相鄰層,其各自的回流路徑也應保持分離,包括過孔。

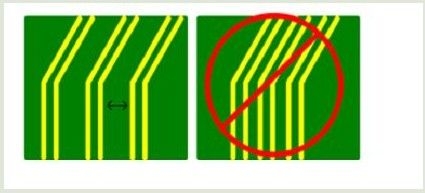

差分線路對之間以及差分線路和其他線路之間都要保持一定的距離,這一點是很重要的。通常的規(guī)則是:相鄰線路對間的距離至少要 5 倍于線路對中兩線的距離如下圖所示。

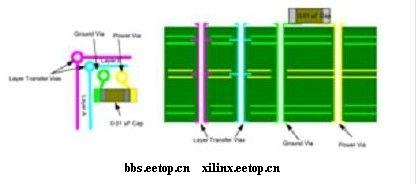

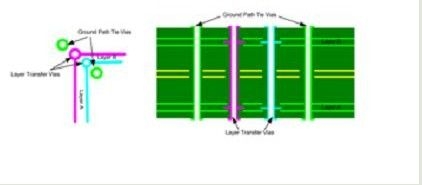

千兆位級信號差分線路應當盡可能避免改變走線層。如果跨層傳輸是必須的,那么需要特別小心。首先,必須提供一個完整的返回路徑。所以我們必須把層A的參考層和層B的參考層耦合在一起。最理想的情況是兩個參考層都是地層。在這種情況下,返回路徑可以通過在轉層過孔附近放置另一個連接兩個參考層的過孔來實現(xiàn)。下圖給出這種技術的示意圖。

如果參考層是不同的(一個是地層,另一個是電源層),則需要在離過孔盡可能近的地

方放置 0.01μF 的電容來連接兩個參考層,降低回流路徑的阻抗。如下圖所示。