摘要:設(shè)計了基于FPGA" title="FPGA">FPGA和NioslI軟核的全數(shù)字逆變焊接電源控制器" title="電源控制器">電源控制器,采用變參數(shù)PID和改進的I-I型雙閉環(huán)電流-弧長控制策略,并應(yīng)用于數(shù)字化MIG焊接電源系統(tǒng)中。介紹了該電源控制器各模塊的功能及設(shè)計方案,分析了MIG焊接電流和弧長的控制問題,并進行了仿真和實際焊接試驗。

關(guān)鍵詞:FPGA;NioslI;變參數(shù)PID;雙閉環(huán)控制;數(shù)字MIG逆變電源

1 概述

脈沖金屬惰性氣體保護焊(pulsed metal inert gas welding),簡稱MIG焊。MIG焊在工藝上具有以下優(yōu)點:焊接保護作用好,焊縫金屬純凈,焊接過程穩(wěn)定,焊縫成形好等。目前,國內(nèi)逆變焊機多采用以DSP為核心或以MCU+DSP為核心的控制結(jié)構(gòu)。當(dāng)需要實時采集焊接數(shù)據(jù)并傳送到上位機上時,單個DSP將難以勝任,以DSP為核心控制器的一種改進的處理方案是采用MCU+DSP或者多個DSP配合完成焊接控制和實時通信等環(huán)節(jié)。該方案無疑增加了系統(tǒng)的成本和復(fù)雜程度。

采用高密度的FPGA取代傳統(tǒng)的模擬驅(qū)動型控制芯片,可大大提高控制器電路設(shè)計的集成度,同時提高逆變電源控制器設(shè)計的靈活性和電源系統(tǒng)的抗干擾能力、控制精度。但是,F(xiàn)PGA作為核心控制器也存在缺點,其存儲能力和軟件的擴展接口能力有限。

NioslI軟核可以根據(jù)用戶的要求來定制和拓展,F(xiàn)PGA內(nèi)部引入NioslI軟核采用SOPC的設(shè)計思路,可以彌補單獨使用FPGA的缺陷,使得基于FPGA硬件邏輯的并行快速性充分發(fā)揮的同時,軟件接口和擴展通信能力也大大加強。本文采用嵌入NioslI軟核的FPGA作為逆變電源的核心控制結(jié)構(gòu)。

2 逆變電源控制器的硬件設(shè)計

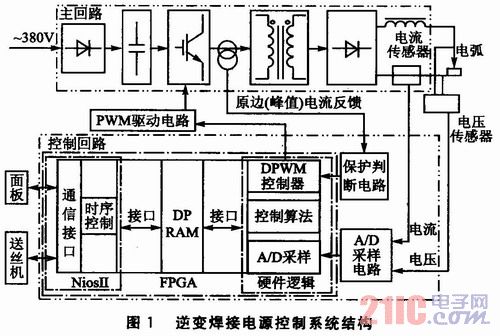

全數(shù)字逆變焊接電源控制系統(tǒng)的硬件結(jié)構(gòu)如圖1所示。主要分為兩部分:焊接電源主回路和控制回路。主回路的工作過程為:380 V工頻交流電整流濾波后變?yōu)?20 V左右直流電,經(jīng)逆變環(huán)節(jié)變?yōu)楦哳l方波交流電,經(jīng)中頻降壓變壓器和輸出整流-濾波環(huán)節(jié)后變?yōu)榈蛪褐绷麟姽┖附邮褂?受控環(huán)節(jié)為橋式逆變過程)。控制回路的核心器件為FPGA,其內(nèi)部設(shè)計包括:FPGA硬件邏輯部分、NiosII" title="NiosII">NiosII軟核部分,以及DPRAM和接口邏輯。

2.1 FPGA硬件邏輯設(shè)計

FPGA硬件邏輯設(shè)計主要包括ADC" title="ADC">ADC采樣控制器、DPWM控制器以及雙閉環(huán)控制算法的設(shè)計。

2.1.1 ADO采樣控制器

全數(shù)字逆變焊機工作頻率為20~40 kHz,采樣速度要求較快;為了滿足電源輸出控制的精度,要求采樣精度要足夠高。另外,由圖1可知,系統(tǒng)需要同時采集電源的輸出電壓和電流兩路信號。采用ADI公司的AD7863。

其轉(zhuǎn)換速率為175 ksps,并行輸出接口,轉(zhuǎn)換精度最高為14位,內(nèi)置兩個獨立A/D轉(zhuǎn)換器。根據(jù)其數(shù)據(jù)手冊中提供的ADC轉(zhuǎn)換時序,可以將ADC控制器分為7個狀態(tài):S0,空閑狀態(tài);S1,啟動轉(zhuǎn)換;S2,A/D正在轉(zhuǎn)換,Busy信號置高電平;S3,轉(zhuǎn)換完成,Busy信號置低,發(fā)送讀取命令;S4,讀取第一個轉(zhuǎn)換值;S5,讀完第一個轉(zhuǎn)換值,發(fā)送第二個讀命令;S6,完成第二個通道的讀取,轉(zhuǎn)移至S0。

根據(jù)以上的設(shè)計思路,采用VHDL語言描述、以狀態(tài)機的形式設(shè)計ADC控制器。

2.1.2 DPWM控制器

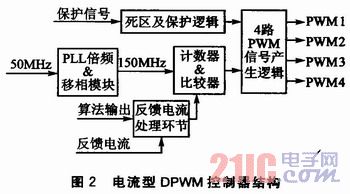

數(shù)字PWM(DPWM)控制器作為連接控制算法與焊接電源主回路的橋梁,作用至關(guān)重要。在以DPWM方式控制的逆變電源系統(tǒng)中,DPWM一般可以分為電壓型DPWM和電流型DPWM兩種方式。電流型DPWM反饋電流和鋸齒波疊加后,與控制信號直接比較,DPWM信號可以迅速輸出電流的變化,動態(tài)性能較好,因此本文采用電流型設(shè)計方案。

DPWM控制器一般需要滿足:占空比可變,而且PWM占空比更新快;有足夠的死區(qū)時間保證IGBT可靠關(guān)斷;能快速抑制不正常輸出電流的突變,以防止焊接電源負(fù)載在短路、焊接電弧、斷路之間切換時造成系統(tǒng)不穩(wěn)定;當(dāng)出現(xiàn)過流等異常現(xiàn)象時,能快速封鎖DPWM驅(qū)動信號,保護主回路。

此外,為了避免系統(tǒng)輸出出現(xiàn)極限震蕩現(xiàn)象,要求DPWM控制信號的分辨率要高于采樣分辨率。本設(shè)計中,ADC有效采樣分辨率設(shè)置為10位,采用150 MHz的計數(shù)頻率和30 kHz的逆變器開關(guān)頻率,由式(1)可推算出DPWM控制信號的分辨率:

![]()

其中,fCLK為計數(shù)(時鐘)頻率,fSW為逆變器開關(guān)頻率,為DPWM控制信號的分辨率。代入實際數(shù)據(jù)可得,計數(shù)上限為5000,即至少13位的分辨率,高于ADC的采樣分辨率。綜合上述分析,電流型DPWM控制器的結(jié)構(gòu)如圖2所示。

2.1.3 雙閉環(huán)控制算法

(1)電流控制方案

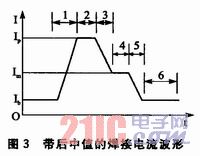

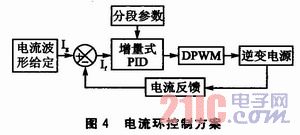

脈沖MIG焊一般采用帶后中值的焊接電流波形,如圖3所示。焊接過程的要求各階段電流穩(wěn)定,且峰值電流Ip、基值電流Ib、中值電流Im以及電流變化斜率都應(yīng)精確控制,以保證焊縫質(zhì)量。因此,保證控制脈沖參數(shù)的精度為電流控制的基本要求。閉環(huán)形式的PID算法最為常用,但是各階段的電流變化斜率不盡相同,即使反復(fù)選擇PID算式的kp、ki、kd參數(shù),也只能折中各階段的控制指標(biāo)。變參數(shù)PID控制則可以分段設(shè)定kp、ki、kd參數(shù),優(yōu)化控制效果。本文采用變參數(shù)PID作為控制方案。

根據(jù)波形的6個階段,將PID參數(shù)分為6組,分別分段調(diào)試取優(yōu)后存儲。工作時控制器根據(jù)當(dāng)前的焊接電流階段選擇最優(yōu)PID參數(shù),以充分保證焊接電流的各個指標(biāo)。這里采用增量式PID方案,變參數(shù)PID電流環(huán)控制方案如圖4所示。

(2)弧長控制方案

焊接電弧的穩(wěn)定對于焊接質(zhì)量的提高和保證焊接電源適應(yīng)不同的焊接工況十分重要。由于焊接電弧電壓直接影響弧長的變化,而電弧電壓隨著焊接電流的改變而變化,因此弧長控制和電流控制是關(guān)聯(lián)的。

當(dāng)前對焊接電弧的調(diào)節(jié)主要有2種方式:以脈沖峰值電流Ip和基值電流Ib均保持不變的I-I方式,以及脈沖電壓Up和基值電流Ib保持不變的U-I方式。I-I方式由于Ip和Ib均為恒流外特性,可以達到穩(wěn)定的熔滴過渡,并且通過控制脈沖電流波形可以精確地控制熔滴過渡行為。但I-I方式是通過調(diào)節(jié)脈沖頻率來實現(xiàn)電弧長度的調(diào)節(jié),存在調(diào)節(jié)速度慢且弧長變化時脈沖周期劇烈變動等缺點。本文采用在不影響熔滴過渡過程的前提下對Ip和Ib進行閾值范圍內(nèi)微調(diào)變化的方式,不但可以減小電流脈沖頻率變化的劇烈程度,而且可以加快電弧動態(tài)調(diào)節(jié)過程。這樣電流控制構(gòu)成內(nèi)環(huán),弧長(壓)控制構(gòu)成外環(huán)。雙閉環(huán)控制算法如圖5所示。

2.2 NiOSIl軟核設(shè)計

NiosII是專門針對Altera公司FPGA的32位嵌入式CPU。它是一個完全由Altera FPGA的邏輯單元和嵌入式RAM塊實現(xiàn)的RISC結(jié)構(gòu)的軟核CPU。NiosIICPU提供3種不同的配置:NioslI/f(快速型)、NiosII/s(標(biāo)準(zhǔn)型)和NiosII/e(經(jīng)濟型)。可以通過SOPC Builder來選擇所需的NiosII軟核,根據(jù)具體的應(yīng)用需求來定制它的外圍設(shè)備,還可以通過自定義指令和外圍模塊來增加NiosII系統(tǒng)的功能。這里考慮到功能需要和FPGA內(nèi)部資源占用率,選用NioslI/e型CPU。

在本設(shè)計中,NiosII/e型CPU任務(wù)有:與面板通信,將電流波形和其他焊接參數(shù)傳送到FPGA的DPRAM中,并且讀取DPRAM中的焊機數(shù)據(jù)傳送到面板上;負(fù)責(zé)保護氣體起停、快送絲、慢送絲等焊接的時序控制。因此NiosII軟核的軟件設(shè)計包括:與DPRAM接口、焊接時序控制,以及控制送絲機和面板通信。根據(jù)上述要求,通過SOPC Builder配置的NioslI軟核系統(tǒng)資源如圖6所示。

2.3 DPRAM和接口邏輯設(shè)計

NioslI和FPGA硬件邏輯之間的數(shù)據(jù)交換可以采用DPRAM、SPI和SCI等形式。DPRAM采用并行傳輸,傳輸速度快,通信協(xié)議簡單,而且FPGA中一般有DPRAM的宏模塊可供使用。因此,本文采用DPRAM作為各種焊接波形數(shù)據(jù)和工藝參數(shù)的存儲媒介。采用FPGA內(nèi)部DPRAM宏模塊,只需根據(jù)需要修改位數(shù)、容量等參數(shù)。考慮本設(shè)計的需要,DPRAM選擇16位,容量為1K字。采用DPRAM作為通信中間環(huán)節(jié),關(guān)鍵問題是如何合理解決以下2個問題:

①DPRAM與NiosII的接口。可以通過為NiosII添加I/O口以模擬DPRAM讀寫時序進行接口,也可以直接利用NiosII中的Avalon總線和DPRAM互連。采用I/O口模擬讀寫時序速度較慢且浪費FPGA的內(nèi)部邏輯資源,本文采用自定義邏輯模塊將Avalon總線與DPRAM進行連接,根據(jù)Avalon總線的讀寫時序設(shè)計接口模塊。

②DPRAM與FPGA硬件邏輯的接口。本文結(jié)合SOPC Builder幫助文件中給出的DPRAM讀寫時序,設(shè)計簡單的邏輯實現(xiàn)接口。

3 仿真與實驗

3.1 ADC控制器仿真

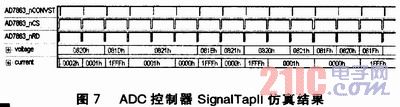

ADC控制器可以使用QuartusII自帶的SignalTapII邏輯分析儀進行仿真驗證。SignalTapII邏輯分析儀可以直觀地觀測ADC控制器采集到的當(dāng)前ADC的轉(zhuǎn)換結(jié)果,準(zhǔn)確而高效。為了加快仿真速度,對ADC的轉(zhuǎn)換值不加濾波處理;為避免最低位劇烈抖動,仿真時僅僅采用高12位,去掉最低兩位的結(jié)果。參考電壓5 V,將電壓通道接到了模擬地(理論值為0000h),電流通道連接到2.54 V左右的模擬電壓(理論值為0820h)。 SignalTapII仿真結(jié)果如圖7所示。

可見,所設(shè)計的ADC控制器能夠穩(wěn)定地控制AD7863工作,除了稍有抖動之外(未加濾波環(huán)節(jié)),采樣結(jié)果準(zhǔn)確可靠。

3.2 DPWM控制器仿真

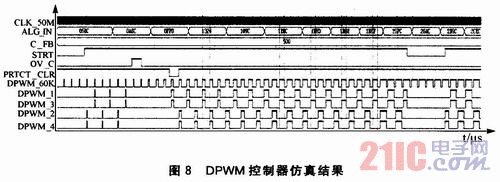

為了驗證所設(shè)計的DPWM控制器是否合理,在保證仿真有效的前提下做如下約定:保護清除按鍵和DPWM啟動按鍵信號均以直接數(shù)字量置位來代替;將算法輸出信號ALG_IN視作給定;反饋電流數(shù)字量設(shè)為恒值500;死區(qū)時間設(shè)定為3.0μs,最小脈寬占空比為2.4%。

仿真環(huán)境為QuartusII-7.2,仿真結(jié)果如圖8所示。啟動信號STRT有效之前DPWM輸出全部封鎖,輸出均為低電平;STRT有效后,在給定小于最小脈寬時輸出最小脈寬,隨著給定的增大,脈寬變大;當(dāng)檢測到過流信號(OV_C)時,4路DPWM輸出立即置低(即全部被封鎖),且置低狀態(tài)能一直持續(xù)到保護信號PRTCT_CLR清除后才結(jié)束。可見DPWM的輸出嚴(yán)格受控。

3.3 焊接試驗波形

3.3.1 靜態(tài)負(fù)載焊接試驗

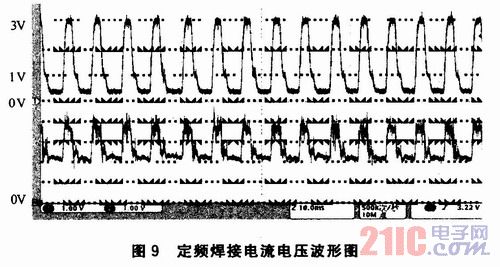

在靜態(tài)負(fù)載條件下,NioslI通過DPRAM給定定頻100 Hz和帶后中值的脈沖電流。電流脈沖參數(shù)為:峰值300 A,峰值時間4 ms;中值100 A,中值時間1 ms;基值電流30 A。采用6段PID參數(shù)。實際輸出的電流和電壓波形如圖9所示。

圖9中,上面為通道1,波形為輸出電流,每格1 V,代表實際焊接電流100 A;下面為通道2,波形為輸出電壓,每格1 V,代表實際焊接電壓10 V。可見,焊接電流波形與給定的脈沖波形(如圖3所示)基本一致。

3.3.2 動態(tài)負(fù)載焊接試驗

雙閉環(huán)控制策略下,死區(qū)時間3.0μs,最小脈寬占空比為2.4%。電流脈沖參數(shù)為:峰值450 A,峰值時間3 ms;中值150 A,中值時間2 ms;基值電流50 A。6段PID參數(shù)。給定平均電弧電壓為30 V,保護氣體成分為20%CO2+80%Ar,保護氣體流量為25 L/min,碳鋼焊絲直徑為1.2 mm,送絲速度為4.5 m/min。試驗結(jié)果表明,當(dāng)焊槍大范圍抖動時,為了調(diào)節(jié)電弧的平均電壓以保證焊接電弧穩(wěn)定,電源系統(tǒng)實時地穩(wěn)定電弧,且電流脈沖的頻率變化均勻,峰值、基值分別隨焊槍的抖動而上下微調(diào)。

4 結(jié)論

本設(shè)計采用FPGA+NioslI軟核為控制核心,設(shè)計了全數(shù)字化脈沖MIG逆變焊接電源控制器。試驗結(jié)果證明:數(shù)字化的設(shè)計思路增強了系統(tǒng)的穩(wěn)定性和靈活性;一塊FPGA在保證控制器功能的前提下,大大降低了開發(fā)成本,縮短了開發(fā)周期;在FPGA內(nèi)部實現(xiàn)6段變參數(shù)PID以及改進的I-I電流-電弧雙閉環(huán)的控制策略,脈沖電流跟蹤效果良好,焊接電弧調(diào)節(jié)穩(wěn)定,動態(tài)性能良好,實際焊接效果出色。本設(shè)計的核心邏輯都是基于統(tǒng)一性較好的VHDL語言設(shè)計,并采用模塊化的設(shè)計方案,因此便于推廣和移植。