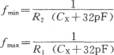

如圖所示為PLL脈沖發(fā)生電路。該電路為鎖相環(huán)(PLL)脈沖發(fā)生器電路。鎖相環(huán)對(duì)晶振進(jìn)行分頻得1kHz信號(hào)作為步進(jìn)頻率,在輸出端獲得10kHz 999kHz的脈沖波形。集成塊74HC4060是內(nèi)部具有非門和1/2n分頻電路的集成芯片,其中,非門與頻率為4.096MHz晶振構(gòu)成振蕩電路,分頻電路對(duì)此進(jìn)行分頻獲得lkHz基準(zhǔn)頻率的信號(hào)。TC9122P是高速可編程計(jì)數(shù)器,其分頻比由BCD碼決定,由編程數(shù)據(jù)決定的分頻比范圍為8~999,本電路工作在10~999的分頻比上。74HC4060內(nèi)部有3種相位比較器,其中相位比較器PC2把輸出頻率同基準(zhǔn)頻率的正沿進(jìn)行比較,從而控制其反饋。VC0的振蕩頻率由Cx、R1和R2決定,其最低、最高頻率為:

如圖所示為PLL脈沖發(fā)生電路。該電路為鎖相環(huán)(PLL)脈沖發(fā)生器電路。鎖相環(huán)對(duì)晶振進(jìn)行分頻得1kHz信號(hào)作為步進(jìn)頻率,在輸出端獲得10kHz 999kHz的脈沖波形。集成塊74HC4060是內(nèi)部具有非門和1/2n分頻電路的集成芯片,其中,非門與頻率為4.096MHz晶振構(gòu)成振蕩電路,分頻電路對(duì)此進(jìn)行分頻獲得lkHz基準(zhǔn)頻率的信號(hào)。TC9122P是高速可編程計(jì)數(shù)器,其分頻比由BCD碼決定,由編程數(shù)據(jù)決定的分頻比范圍為8~999,本電路工作在10~999的分頻比上。74HC4060內(nèi)部有3種相位比較器,其中相位比較器PC2把輸出頻率同基準(zhǔn)頻率的正沿進(jìn)行比較,從而控制其反饋。VC0的振蕩頻率由Cx、R1和R2決定,其最低、最高頻率為:

。

。