Ni VeriStand是一種配置實(shí)時(shí)測試應(yīng)用程序的軟件環(huán)境。即買即用的NI VerStand有助于您配置針對多核處理器的實(shí)時(shí)引擎,以執(zhí)行以下任務(wù):

· 模擬、數(shù)字、通信總線,和基于現(xiàn)場可編程門陣列(FPGA)的I/O接口

· 可觸發(fā),多文件數(shù)據(jù)記錄

· 實(shí)時(shí)激勵(lì)生成

· 計(jì)算通道

· 事件預(yù)警和預(yù)警響應(yīng)程序

NI VeriStand 還能夠從NI LabVIEW 軟件和第三方環(huán)境中導(dǎo)入控制算法,仿真模型和其他任務(wù)。您可以使用運(yùn)行時(shí)可編輯的用戶界面監(jiān)測這些任務(wù),并與其交互,該界面包含許多用于強(qiáng)制賦值、警報(bào)監(jiān)控、I/O校準(zhǔn)、激勵(lì)配置編輯的有效工具。NI VeriStand的使用不需要掌握編程知識(shí),但是可以在多種不同的軟件環(huán)境進(jìn)行自定義和擴(kuò)展,如NI LabVIEW,ANSI C/C++,和其他建模和編程環(huán)境。

NI VeriStand 面向?qū)崟r(shí)測試應(yīng)用

實(shí)時(shí)測試中將實(shí)時(shí)操作系統(tǒng)作為測試系統(tǒng)的一部分。與使用通用操作系統(tǒng)相比,推動(dòng)實(shí)時(shí)測試系統(tǒng)最常見的需求是需要實(shí)現(xiàn)更高的可靠性和更高的性能。

實(shí)時(shí)測試系統(tǒng)的一個(gè)實(shí)例是硬件回路測試仿真器,在該系統(tǒng)中,必須確定性地執(zhí)行系統(tǒng)模型,以提供在物理上不屬于測試組件的準(zhǔn)確仿真。使用閉環(huán)控制的應(yīng)用程序是另一種實(shí)時(shí)測試應(yīng)用。這些系統(tǒng)必須自動(dòng)控制測試系統(tǒng)某部分,如溫室,通過傳感器交互,確定性定點(diǎn)設(shè)置的變化以實(shí)現(xiàn)達(dá)到系統(tǒng)的預(yù)想狀態(tài)。系統(tǒng)也必須檢測并對預(yù)警條件迅速地作出 響應(yīng),這有助于防止操作人員受傷或?qū)y試系統(tǒng)造成損害。與這些應(yīng)用程序類似,測試單元激勵(lì)和檢測應(yīng)用程序都已經(jīng)擁有一個(gè)完整的控制系統(tǒng),或者不需要閉環(huán)控制,只需要能夠提供確定性激勵(lì)生成和測試單元檢測的工具。

這些實(shí)時(shí)測試應(yīng)用程序必需的核心功能已經(jīng)實(shí)現(xiàn),并在NI VeriStand架構(gòu)上進(jìn)行了優(yōu)化——可以配置并使用。這包括主接口通信、數(shù)據(jù)記錄、激勵(lì)生成、預(yù)警檢測和響應(yīng),以及算法和模型執(zhí)行。在該框架的基礎(chǔ)上,您可以通過使用LabVIEW,ANSI C/C++和其他模型和編程環(huán)境,向NI VeriStand軟件環(huán)境添加定制功能。

通過使用NI VeriStand 來建立您的實(shí)時(shí)測試系統(tǒng),您既可以縮短開發(fā)時(shí)間與應(yīng)用程序維護(hù)成本,又能在每次版本升級(jí)時(shí),獲得軟件功能和性能的提升。

用NI VerStand軟件環(huán)境來開發(fā)應(yīng)用程序

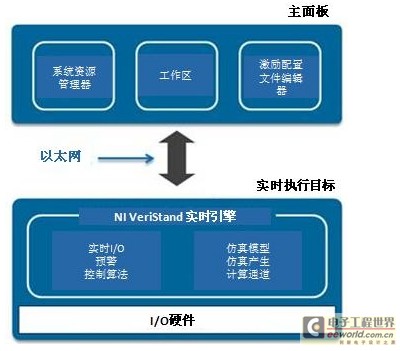

NI VeriStand 實(shí)時(shí)測試應(yīng)用程序通常包括一個(gè)或多個(gè)實(shí)時(shí)執(zhí)行目標(biāo),這些目標(biāo)通過以太網(wǎng)與主機(jī)系統(tǒng)進(jìn)行通信。每個(gè)實(shí)時(shí)執(zhí)行目標(biāo)運(yùn)行NI VeriStand 引擎,該引擎通過Windows主系統(tǒng)進(jìn)行配置,通過以太網(wǎng)部署。一旦您的NI VeriStand引擎配置完成部署,您就可以使用NI VeriStand 工作區(qū)窗口和其所提供的工具,如激勵(lì)配置文件編輯器,在運(yùn)行時(shí)與您的測試系統(tǒng)進(jìn)行交互。

當(dāng)開發(fā)和運(yùn)行NI VeriStand應(yīng)用程序時(shí),您可以使用三個(gè)主要窗口:系統(tǒng)資源管理器,工作區(qū),和激勵(lì)配置文件編輯器。

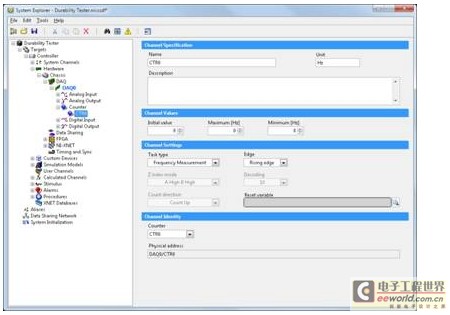

系統(tǒng)資源管理器

您可以使用系統(tǒng)資源管理器窗口來創(chuàng)建一個(gè)系統(tǒng)定義。該系統(tǒng)定義包含了執(zhí)行NI VeriStand引擎任務(wù)的設(shè)置選項(xiàng),如硬件I/O,還有從其他程序或模型環(huán)境中導(dǎo)入的功能。您可以通過添加選項(xiàng)到位于系統(tǒng)資源管理器左側(cè)的系統(tǒng)定義樹上,和在右側(cè)窗口的配置選項(xiàng)上設(shè)置選項(xiàng),進(jìn)行系統(tǒng)的定義。一旦系統(tǒng)定義完成,您就部署了您的執(zhí)行目標(biāo)的系統(tǒng)定義,并開始使用NI VeriStand 工作區(qū)來創(chuàng)建一個(gè)針對您的測試系統(tǒng)的運(yùn)行界面。

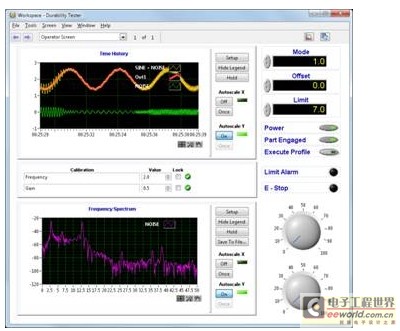

工作區(qū)

工作區(qū)是部署后的系統(tǒng)定義用戶界面。使用該運(yùn)行時(shí)可編輯的用戶界面,您可以放置界面輸入控件和顯示控件,并將它們映射到您的實(shí)時(shí)應(yīng)用程序的通道中。您可以使用多個(gè)工作區(qū)屏幕,將您的控件和指示組織成您的邏輯組,從而對應(yīng)各類不同的應(yīng)用任務(wù),或者僅是為了增加用戶界面的可用空間。用戶接入管理功能允許您基于不同用戶的登錄賬號(hào),對不同的用戶控制其訪問權(quán)限。

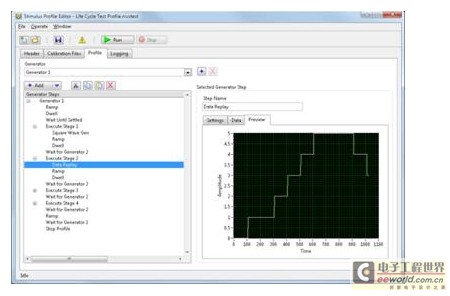

激勵(lì)配置文件編輯器

激勵(lì)配置文件編輯器是NI VeriStand工作區(qū)上的一種工具,用于創(chuàng)建激勵(lì)生成,以及記錄部署于NI VeriStand引擎、對測試配置文件確定性執(zhí)行的任務(wù)。

激勵(lì)配置文件是通過指定一組NI VeriStand實(shí)時(shí)引擎將會(huì)執(zhí)行的激勵(lì)生成步驟而創(chuàng)建的。在您的激勵(lì)生成器中,產(chǎn)生波形、回放數(shù)據(jù)、設(shè)置通道值有多個(gè)步驟,以及執(zhí)行分支和循環(huán)結(jié)構(gòu)有一個(gè)條件步驟。您還可以以獨(dú)立的日志速率添加多個(gè)日志任務(wù)和激勵(lì)條件到您的激勵(lì)配置文件中。例如,對于變化緩慢的通道,一個(gè)日志文件能夠以較低的速率采集數(shù)據(jù),如果在測試期間,觸發(fā)條件發(fā)生,那么另一個(gè)日志文件能夠被設(shè)置為較高的速率進(jìn)行采集數(shù)據(jù)。

激勵(lì)配置文件在NI VeriStand實(shí)時(shí)引擎中執(zhí)行,然而,您可以從主機(jī)界面中使用NI VeriStand 工作宏記錄,或者使用其他工具,如NI TestStand或Iron Python添加額外的測試自動(dòng)化功能。

除了激勵(lì)配置文件編輯器,NI VeriStand工作區(qū)包括許多其他工具,當(dāng)與實(shí)時(shí)測試應(yīng)用程序協(xié)同工作時(shí),這些工具是很有用的。這些工具可用來檢測預(yù)警、校準(zhǔn)硬件I/O,和強(qiáng)制為通道賦值。還有一個(gè)實(shí)時(shí)控制瀏覽器,其能夠監(jiān)控您的實(shí)時(shí)執(zhí)行目標(biāo)的運(yùn)行狀態(tài)。

NI VeriStand引擎架構(gòu)

NI VeriStand 引擎是非可見執(zhí)行機(jī)制,負(fù)責(zé)執(zhí)行硬件I/O、模型、過程、預(yù)警和在系統(tǒng)定義文件中指定的其他測試系統(tǒng)任務(wù)。引擎不但控制整個(gè)系統(tǒng)的定時(shí),而且控制NI VeriStand 引擎和工作區(qū)的主機(jī)之間的通信。

NI VeriStand 引擎包括多個(gè)定時(shí)循環(huán),其執(zhí)行定時(shí)由硬件事件控制,精度為微妙。確定性內(nèi)存緩沖器在不同循環(huán)任務(wù)間提供通信,不會(huì)在引擎執(zhí)行中引起數(shù)據(jù)抖動(dòng)。采用多循環(huán)架構(gòu),NI VeriStand引擎自然利用了多核處理器并行處理能力的優(yōu)勢,提升了系統(tǒng)性能。創(chuàng)建系統(tǒng)定義時(shí),包括在高吞吐量、并行性和低延時(shí)、順序結(jié)構(gòu)間選擇的能力,可以配置各種不同的引擎執(zhí)行設(shè)置。此外,NI VeriStand引擎發(fā)布了各種系統(tǒng)參數(shù),您可以在運(yùn)行時(shí)訪問。或者您可以使用NI 實(shí)時(shí)執(zhí)行跟蹤工具更細(xì)致地查看您的應(yīng)用程序的執(zhí)行。

引擎的實(shí)時(shí)I/O任務(wù)使用硬件定時(shí),單點(diǎn)I/O結(jié)構(gòu),是仿真,控制,和逐點(diǎn)分析任務(wù)的理想選擇。然而,使用NI VeriStand定制設(shè)備可以添加對較高速率,緩沖信號(hào)生成和采集的支持,這些內(nèi)容將會(huì)在下一節(jié)進(jìn)行討論。

NI VeriStand引擎可以在NI PCI,NI PXI實(shí)時(shí)系統(tǒng),還有NI CompactRIO和具有128MB或更大 的DRAM RIO接口上的單板RIO上運(yùn)行。實(shí)時(shí)系統(tǒng)使您能夠結(jié)合同步I/O確定性地執(zhí)行您的測試——這對于實(shí)現(xiàn)閉環(huán)控制或與真實(shí)組件交互的系統(tǒng)仿真應(yīng)用程序來說是關(guān)鍵的能力。然而,對于低性能系統(tǒng)需求或?qū)崿F(xiàn)模型在環(huán)(MIL)或軟件在環(huán)(SIL)的測試,您還可以在同一臺(tái)計(jì)算機(jī)上將NI VeriStand 引擎作為您的用戶界面加以運(yùn)行。

自定義NI VerStand

NI VeriStand通過使用基于配置的開發(fā)方法,為創(chuàng)建實(shí)時(shí)測試應(yīng)用程序提供軟件架構(gòu)。實(shí)時(shí)測試應(yīng)用程序所需要的所有常見任務(wù)已經(jīng)在NI VeriStand引擎內(nèi)部進(jìn)行了實(shí)現(xiàn)與優(yōu)化。然而,您還可以使用LabVIEW和其他軟件工具添加功能到您的NI VeriStand應(yīng)用程序中。

自定義設(shè)備

您可以使用NI VeriStand自定義設(shè)備,通過客戶自定義時(shí)間經(jīng)驗(yàn),向NI Veristand引擎中添加運(yùn)行時(shí)功能。創(chuàng)建NI VeriStand自定義設(shè)備的LabVIEW使用的模板庫中,包含針對NI VeriStand數(shù)據(jù)和定時(shí)資源的接口。這使得自定義設(shè)備能夠向NI VeriStand 引擎中的本地任務(wù)一樣運(yùn)行。該接口使用方式的示例包括:對第三方硬件I/O接口添加支持,或執(zhí)行緩沖信號(hào)采集,以提供高速率測量。

模型

NI VeriStand能夠?qū)肽贚abVIEW、MathWorks公司的Simulink?、ITI公司的SimulationX、Gamma技術(shù)公司的GT-POWER,和其他建模和編程環(huán)境中創(chuàng)建的編譯代碼。具有該功能,您可以添加實(shí)時(shí)閉環(huán)控制、系統(tǒng)仿真、信號(hào)處理和信號(hào)發(fā)生器到NI VeriStand應(yīng)用程序中。盡管許多軟件環(huán)境已在NI VeriStand下支持,您還是可以添加產(chǎn)品提供的NI VeriStand模型框架所產(chǎn)生C代碼的從而支持其他環(huán)境。

FPGA特性

當(dāng)添加實(shí)時(shí)I/O硬件接口到NI VeriStand中,您可以快速配置各種不同的標(biāo)準(zhǔn)模擬,數(shù)字和通信總線接口;然而,NI VeriStand還提供LabVIEW基于FPGA可重配置I/O(RIO)設(shè)備的用戶定義I/O 硬件。您可以使用該功能來創(chuàng)建用戶定義I/O硬件接口,實(shí)現(xiàn)自定義信號(hào)處理、仿真、觸發(fā)和/或 控制任務(wù),并以25納秒的速率執(zhí)行,不占用任何您實(shí)時(shí)應(yīng)用程序的處理帶寬。此外,因?yàn)镮/O 接口是基于FPGA的,您可以很容易地重新配置特性或設(shè)備的行為,以適應(yīng)新的需求,或者創(chuàng)建能夠用于多個(gè)應(yīng)用程序的測試系統(tǒng),而不需要改變I/O接口硬件。

工作區(qū)工具

NI VeriStand 提供了許多工具,您可以使用這些工具來監(jiān)測NI VeriStand引擎,并與之進(jìn)行互動(dòng)。您可以使用LabVIEW 來創(chuàng)建您自己的運(yùn)行工具,將它們添加到NI VeriStand工作區(qū)中。例如,您可以創(chuàng)建一個(gè)自定義運(yùn)行工具,該工具與數(shù)字萬用表或示波器交互,提供專門測試數(shù)據(jù)作為驗(yàn)證程序的一部分。

工作區(qū)對象

當(dāng)與運(yùn)行可編輯工作區(qū)協(xié)同工作時(shí), 您可以添加各種不同的輸入和輸出控制和指示到工作區(qū)上,并將它們與NI VeriStand通道連接。盡管NI VeriStand包含各種不同的工作區(qū)對象,您仍需使用LabVIEW來創(chuàng)建能夠在運(yùn)行時(shí)被加入NI VeriStand工作區(qū)的自定義控制和指示。其中的一些實(shí)例包括添加更接近系統(tǒng)界面的UI對象,或用自定義功能創(chuàng)建UI對象,如順序處理或預(yù)警。

API庫

NI VeriStand為工作區(qū)和系統(tǒng)資源管理器 提供基于.NET的API,您可以使用該API來創(chuàng)建NI VeriStand自定義接口,或?qū)崿F(xiàn)配置和/或NI VeriStand應(yīng)用程序操作的自動(dòng)化。例如,您可以使用系統(tǒng)資源管理器API庫來創(chuàng)建一個(gè)自定義配置窗口,限制用戶對NI VeriStand應(yīng)用程序作出改變,或使應(yīng)用程序參數(shù)指定在表格中,以簡化配置過程。此外,您可以使用工作區(qū)API 庫使NI VeriStand應(yīng)用程序操作進(jìn)行自動(dòng)化,或使用LabVIEW軟件創(chuàng)建一個(gè)完全的自定義運(yùn)行接口。