前言

在大容量高速采集系統(tǒng)項目的開發(fā)過程中,FPGA作為可編程邏輯器件,設(shè)計靈活、可操作性強,是高速數(shù)字電路設(shè)計的核心器件。由于FPGA內(nèi)嵌存儲器的容量有限,通常不能夠滿足實際設(shè)計電路的需求,需要外接SRAM、SDRAM、磁盤陣列等大容量存儲設(shè)備。本文主要介紹高速FIFO電路在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用,相關(guān)電路主要有高速A/D轉(zhuǎn)換器、FPGA、SDRAM存儲器等。圖1為本方案的結(jié)構(gòu)框圖。A/D輸出的數(shù)據(jù)流速度快,經(jīng)過FPGA降速后,位數(shù)寬,速度仍然很高,不能直接存儲到外部存儲器。在設(shè)計時,要經(jīng)過FIFO緩存,然后才能存儲到外部存儲器。本設(shè)計的FIFO容量小、功能強,充分利用了FPGA內(nèi)部FIFO電路的特點,結(jié)合實際電路,優(yōu)化了整個電路模型的設(shè)計。

異步FIFO生成

FIFO占用的內(nèi)存資源為FPGA內(nèi)嵌的block RAM,由Xilinx公司提供的ISE開發(fā)平臺自動生成。讀寫時鐘有通用時鐘和獨立時鐘可選,我們采用獨立時鐘,rd_clk和wr_clk獨立,為了保證在高速采集時數(shù)據(jù)不丟失,rd_clk頻率不低于wr_clk。FIFO讀模式采用標準FIFO,每次啟動采集時都要對FIFO進行復(fù)位,為異步復(fù)位,初始化內(nèi)部指針和輸出寄存器。在FIFO生成過程中,我們啟用almost_full 和almost_empty選項,以及prog_full 和prog_empty選項,prog_full和prog_empty要進行參數(shù)設(shè)置,具體設(shè)置參數(shù)如圖2所示。

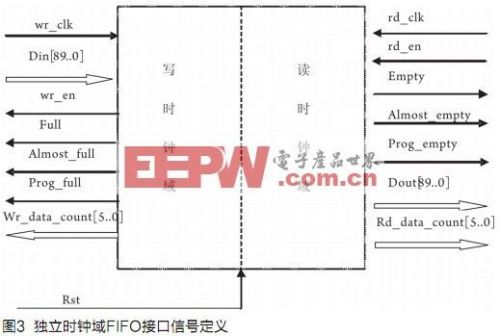

FIFO接口信號定義

根據(jù)FIFO的生成過程,在圖3中給出了讀寫時鐘域的信號定義,所有的在寫時鐘域的輸入信號都必須經(jīng)過寫時鐘同步,所有的在讀時鐘域的輸入信號都要經(jīng)過讀時鐘同步。信號經(jīng)過時鐘同步后,可以確保在讀寫過程中不會出現(xiàn)亞穩(wěn)態(tài),導(dǎo)致讀寫操作出現(xiàn)錯誤。

下面對讀寫時鐘域定義信號給予說明:

rst:復(fù)位信號,高有效,異步復(fù)位,每次啟動采集都要首先對FIFO進行復(fù)位;

wr_clk:寫時鐘;

wr_en:與寫時鐘同步;

din:輸入數(shù)據(jù)總線;

rd_clk:讀時鐘;

dout:輸出數(shù)據(jù)總線;

full:FIFO全滿標志;

empty:FIFO全空標志;

almost_full:高有效,如果為高電平,在寫一個數(shù)據(jù)FIFO將全滿;

almost_empty:高有效,如果為高電平,在讀一個數(shù)據(jù)FIFO將全空;

prog_full:可編程滿標志,根據(jù)需要,可以設(shè)定FIFO內(nèi)部有多少數(shù)據(jù),該標志信號有效;

prog_empty:可編程空標志,根據(jù)需要,可以設(shè)定FIFO內(nèi)部有多少數(shù)據(jù),該標志信號有效;

wr_data_count:說明FIFO內(nèi)部已經(jīng)寫了多少數(shù)據(jù);

rd_data_count:說明FIFO內(nèi)部有多少數(shù)據(jù)可以讀。

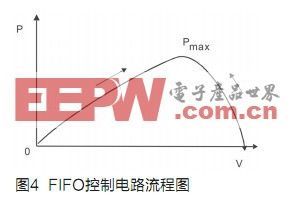

FIFO控制電路設(shè)計

實際電路設(shè)計不考慮讀寫時鐘的頻率和相位的異同,讀寫時鐘域的電路基于同步電路設(shè)計的理念來進行設(shè)計,在設(shè)計過程中,滿足讀時鐘頻率不低于寫時鐘頻率即可。在圖4中給出了FIFO控制電路的流程圖,下面將對低速傳輸和高速傳輸進行詳細介紹。

低速采集數(shù)據(jù)傳輸過程

在圖5給出了低速采集時傳輸周期時序仿真時序圖,在低速采集時,寫時鐘頻率小于讀時鐘,每次觸發(fā)長度為FIFO長度的一半。采集結(jié)束即剩余數(shù)據(jù)傳輸?shù)拈L度不到FIFO的一半。根據(jù)prog_full的設(shè)置,在prog_full有效,同時采集門控信號有效時啟動觸發(fā)請求,由于prog_full為寫時鐘域信號,必須要經(jīng)過rd_clk同步,源代碼如下:

process(rd_clk,acq_start_rst)

begin

if acq_start_rst='1'then

prog_full_dly<='0';

prog_full_dly1<='0';

elsif rd_clk'event and rd_clk='1'

then

if acq_gate= '1' then

prog_full_dly<=prog_full;

prog_full_dly1<=prog_

full_dly;

else

prog_full_dly<='0';

prog_full_dly1<='0';

end if;

end if;

end process;

當(dāng)FIFO半滿時觸發(fā)讀請求有效,acq_frame_l為低電平,啟動采集數(shù)據(jù)傳輸請求,地址和數(shù)據(jù)同時有效,sdram控制器給出應(yīng)答信號acq_trdy_l,長度由FIFO讀寫控制電路決定,觸發(fā)一次的長度為32,即FIFO半滿的長度,傳輸完畢,給出傳輸結(jié)束標志信號acq_blast,一次傳輸周期結(jié)束。采集門控信號結(jié)束后,F(xiàn)IFO剩余數(shù)據(jù)長度不足32,這時候啟動門控結(jié)束傳遞進程,觸發(fā)結(jié)束標志由almost_empty決定,當(dāng)alomost_empty有效時,停止觸發(fā)。

高速采集數(shù)據(jù)傳輸過程

在高速采集時,讀時鐘頻率等于寫時鐘頻率,當(dāng)啟動觸發(fā)傳輸時,觸發(fā)傳輸長度為門控信號長度,直到將FIFO內(nèi)部數(shù)據(jù)傳輸完畢,觸發(fā)結(jié)束標志由almost_empty決定,當(dāng)alomost_empty有效時,停止觸發(fā)傳輸,觸發(fā)傳輸過程如圖6所示。

結(jié)語

采用高速異步FIFO作為數(shù)據(jù)采集緩存,應(yīng)用范圍十分廣泛。特別是在高速數(shù)據(jù)采集系統(tǒng)中,在外接存儲器時,采集數(shù)據(jù)首先要經(jīng)過緩存才能存入外部存儲器,采用FPGA自生成FIFO就能夠滿足要求。本方案充分利用FIFO的特點,通過控制電路優(yōu)化設(shè)計,解決了讀寫時鐘的異同問題,提高了電路的工作效率。