在現(xiàn)有的民用、軍用通信系統(tǒng)的眾多應(yīng)用領(lǐng)域中,為了實(shí)現(xiàn)高速率數(shù)據(jù)傳輸,提高頻譜利用率,必須采用帶寬效率更高的編碼、調(diào)制技術(shù)。在眾多的調(diào)制方式中,連續(xù)相位調(diào)制信號(hào)(CPM 信號(hào))具有恒包絡(luò)特性,它用于承載信息的相位軌跡連續(xù)變化,因此該類(lèi)信號(hào)擁有較高的帶寬效率。基于CPM信號(hào)的恒包絡(luò)、帶寬緊湊和能量利用率高等優(yōu)點(diǎn),近幾年來(lái),它受到廣泛的研究與應(yīng)用。

文中分析了二進(jìn)制,部分響應(yīng)L=2 的連續(xù)相位調(diào)制方式,提出了一種該調(diào)制方式下解調(diào)器的FPGA 設(shè)計(jì)方法,并運(yùn)用VHDL 硬件描述語(yǔ)言實(shí)現(xiàn)。

1 CPM 的基本原理

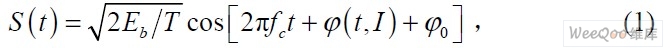

連續(xù)相位調(diào)制信號(hào)可以用式(1)表示:

式(1)中, b E 表示信號(hào)的碼元能量,T 是碼元間隔, 即表示信號(hào)幅度。c f 是載波頻率,φ (t, I )是帶有傳輸信息的信號(hào)相位函數(shù),其中I 表示發(fā)生的符號(hào)序列。φ (t, I )的表達(dá)式如下:

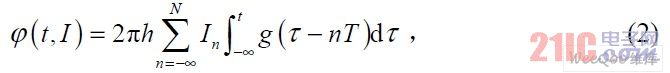

即表示信號(hào)幅度。c f 是載波頻率,φ (t, I )是帶有傳輸信息的信號(hào)相位函數(shù),其中I 表示發(fā)生的符號(hào)序列。φ (t, I )的表達(dá)式如下:

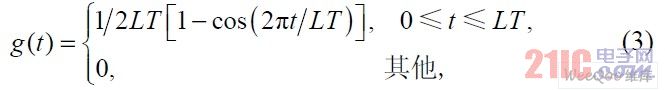

其中n I 是M (M = 2,4,8,16……) 進(jìn)制的符號(hào)信息,取值為{±1,±3,……,±(M -1)}。文中M 為二進(jìn)制調(diào)制, n I 的取值為+1、-1。h 是調(diào)制指數(shù),g(t)是成形脈沖函數(shù)。脈沖函數(shù)g(t)采用升余弦脈沖RC:

式(3)中, L 又稱(chēng)為關(guān)聯(lián)長(zhǎng)度。

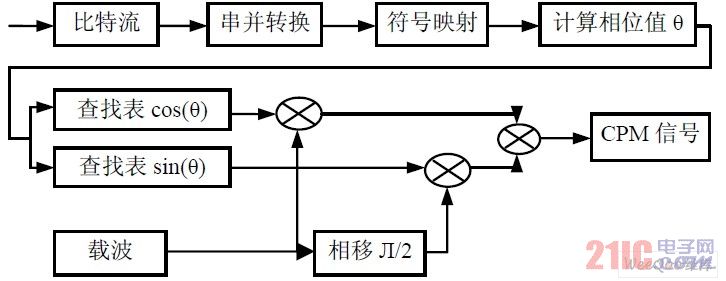

根據(jù)式(2)計(jì)算CPM 信號(hào)的基帶相位,根據(jù)相位計(jì)算基帶信號(hào)的I/Q 兩路,之后使用兩路信號(hào)相加就可以得到調(diào)制后的CPM 信號(hào),見(jiàn)圖1。

圖1 CPM 信號(hào)調(diào)制

2 CPM 解調(diào)模塊的原理及其實(shí)現(xiàn)

2.1 解調(diào)器實(shí)現(xiàn)原理

對(duì)CPM 信號(hào)的接收、解調(diào),常采取的步驟為:解調(diào)-最大似然序列估計(jì)-Viterbi 譯碼-判決。首先將接收到的復(fù)包絡(luò)信號(hào)分為I,Q兩路,下變頻為基帶信號(hào),分別與cos(ψ (t, a))和sin(ψ (t, a))相關(guān)后相加,從而得到節(jié)點(diǎn)的度量值。對(duì)于t時(shí)刻每個(gè)狀態(tài),可以根據(jù)其輸入值的不同,計(jì)算來(lái)自前一級(jí)節(jié)點(diǎn)的兩條路徑的路徑度量,并分別加上前一級(jí)節(jié)點(diǎn)的節(jié)點(diǎn)度量,然后從中選擇一個(gè)最小的度量值作為節(jié)點(diǎn)度量,并存儲(chǔ)前一級(jí)節(jié)點(diǎn)的信息。

2.2 解調(diào)器實(shí)現(xiàn)框圖

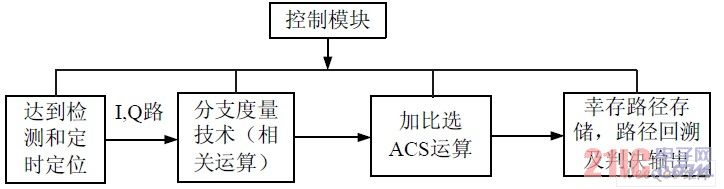

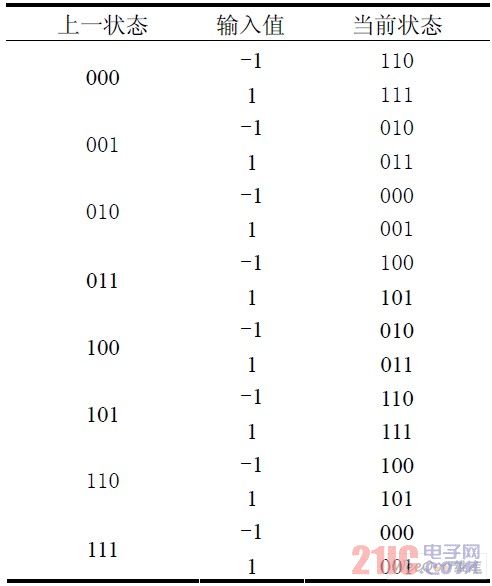

這里仿真采用二進(jìn)制2RC 的調(diào)制方式,根據(jù)Viterbi 譯碼方式可知,調(diào)制信號(hào)共有8 個(gè)狀態(tài),將這些狀態(tài)分別編碼為000,001,010,011,100,101,110,111。輸入數(shù)據(jù)與狀態(tài)間轉(zhuǎn)移關(guān)系見(jiàn)表1。筆者在設(shè)計(jì)中將其分為四個(gè)模塊:分支度量模塊、加比選模塊、回溯模塊和控制模塊。其結(jié)構(gòu)設(shè)計(jì)如圖2 所示。

圖2 解調(diào)過(guò)程

(1)分支度量模塊

此模塊根據(jù)輸入數(shù)據(jù)計(jì)算分支度量值。在FPGA設(shè)計(jì)中,預(yù)先將每種基準(zhǔn)狀態(tài)抽樣時(shí)刻的值存入STD 寄存器中,在計(jì)算分支度量時(shí)通過(guò)查表得到基準(zhǔn)狀態(tài)的值。將輸入I,Q 兩路數(shù)據(jù)進(jìn)行串/并轉(zhuǎn)換,得到一個(gè)碼元持續(xù)時(shí)間內(nèi)的調(diào)制信號(hào)后,與每種基準(zhǔn)狀態(tài)的抽樣值相乘并相加,從而得到I,Q 兩路的路徑度量值。最后將I,Q 兩路度量值相加,便可以得到各狀態(tài)的分支度量值。

(2)加比選ACS 模塊

此模塊分為兩部分:①計(jì)算路徑度量值;②選擇當(dāng)前時(shí)刻最佳路徑。當(dāng)前狀態(tài)的路徑度量值為該狀態(tài)下所有可能的路徑度量值中的最大值。最佳路徑為最大路徑度量值對(duì)應(yīng)的上一狀態(tài)。在設(shè)計(jì)中采用確定CPM 調(diào)制的起始狀態(tài)的方法。

復(fù)位時(shí)將起始狀態(tài)的路徑度量值賦值為0;將其他狀態(tài)的路徑度量值賦值為一個(gè)較小的負(fù)數(shù)。采用這種方式有效避免解調(diào)時(shí)起始狀態(tài)的不確定性。

CPM 的解調(diào)在一定的譯碼數(shù)量后,路徑度量值的存儲(chǔ)器便會(huì)飽和溢出。該設(shè)計(jì)采用一種簡(jiǎn)單方法防止溢出:每次路徑度量值計(jì)算完成后,判斷其最大值,如果最大值超過(guò)某一確定的正值,則所有的路徑度量值減去一個(gè)正值。再判斷是否有度量值小于一個(gè)確定的負(fù)數(shù),如果有,則將其值重新賦值為一個(gè)較小的負(fù)數(shù)。仿真中,證明了這種方法的可行性。

表1 輸入數(shù)據(jù)與狀態(tài)間轉(zhuǎn)移關(guān)系

(3)回溯模塊

此模塊包括幸存路徑存儲(chǔ)和判決輸出。在模塊中比較當(dāng)前時(shí)刻各狀態(tài)的路徑度量值,求得最大路徑度量值,以及對(duì)應(yīng)的當(dāng)前狀態(tài)。從表1 可知,狀態(tài)的最低位可以表現(xiàn)上一時(shí)刻的輸入值,最低位為0 時(shí),表示上一時(shí)刻的輸入碼字為-1;最低位為1 時(shí)表示上一時(shí)刻的輸入碼字為1。

3 硬件實(shí)現(xiàn)、時(shí)序仿真和性能

這里選擇的FPGA 是Xilinx 公司的Virtex5 系列的XC5VSX95T 芯片,設(shè)計(jì)軟件為ISE, Synplify, Modelsim,Matlab,設(shè)計(jì)語(yǔ)言采用VHDL 硬件描述語(yǔ)言。

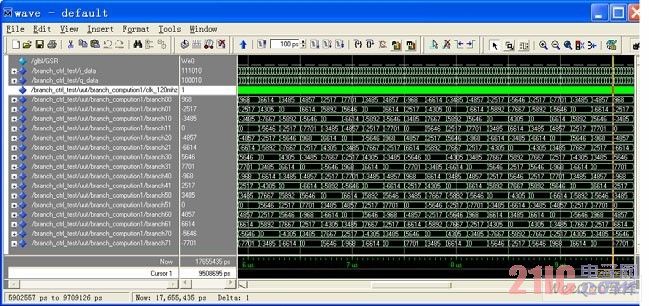

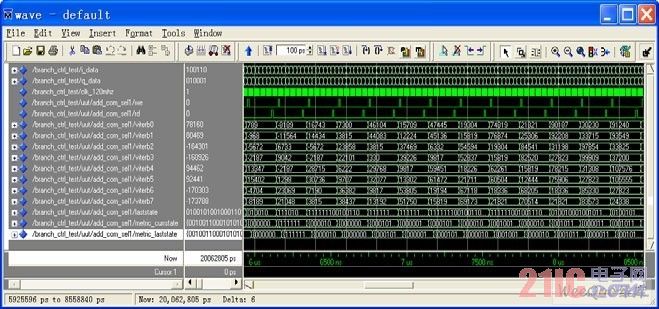

仿真中選擇二進(jìn)制,關(guān)聯(lián)長(zhǎng)度L 取2,升余弦脈沖的調(diào)制方式。仿真中波特率為5 MHz, 采用8 倍采樣,系統(tǒng)時(shí)鐘為120 MHz。假設(shè)輸入到調(diào)制器的雙極性比特流為{ } n b :1,1,1,-1,1,1,-1,-1,1,1,1,-1,1,1,-1,1……分支度量仿真結(jié)果如圖3 所示。

圖3 分支度量仿真結(jié)果

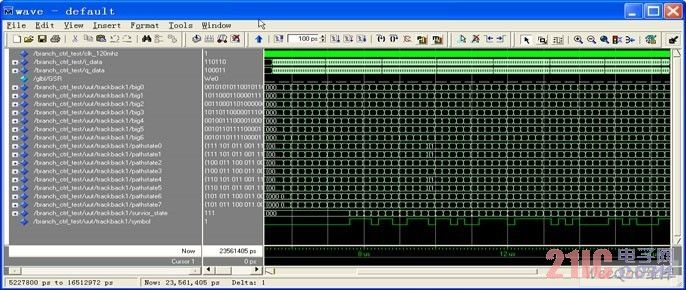

加比選模塊仿真結(jié)果如圖4 所示。

圖4 加比選模塊仿真結(jié)果

幸存路徑存儲(chǔ)和判決輸出模塊仿真結(jié)果如圖5 所示。

圖5 幸存路徑存儲(chǔ)和判決輸出模塊仿真結(jié)果

譯碼碼字:1,1,1,-1,1,1,-1,-1,1,1,1,-1,1,1,-1,1……當(dāng)調(diào)制信號(hào)不加高斯白噪聲時(shí),實(shí)現(xiàn)了誤碼率為0 的解調(diào)。仿真結(jié)果表明這里所設(shè)計(jì)的性能達(dá)到設(shè)計(jì)的要求。

4 結(jié)語(yǔ)

文中主要設(shè)計(jì)了該二進(jìn)制2RC CPM 信號(hào)基于FPGA 的解調(diào)器。該方法針對(duì)Viterb 譯碼方法,提出了一種新的防止路徑度量值溢出方法。該設(shè)計(jì)的優(yōu)點(diǎn)是:幸存路徑存儲(chǔ)器中存入的只是路徑信息,不需要存儲(chǔ)路徑度量值,節(jié)省了存儲(chǔ)空間;當(dāng)譯碼輸出時(shí)只需要讀出最大路徑度量值的狀態(tài)所對(duì)應(yīng)的幸存路徑存儲(chǔ)單元的最低位狀態(tài)值,提高了譯碼速度。該方法有效地防止路徑度量值溢出。