0 引言

隨著便攜式消費電子產(chǎn)品應(yīng)用的持續(xù)增長,降低功耗和低電源電壓成為CMOS運算放大器的設(shè)計趨勢。在低壓下工作時,一般采用互補差分輸入對來實現(xiàn)軌至軌的信號輸入,但是,其電源電壓被限制在必須大于兩倍閾值電壓與兩倍過驅(qū)動電壓之和。

為了使運算放大器能工作在更低電源電壓下,現(xiàn)有的方法是,采用體驅(qū)動晶體管、雙p溝道差分輸入對、輸入信號重整、弱反型區(qū)和輸入共模電平偏移技術(shù)。體驅(qū)動晶體管和弱反型區(qū)晶體管的跨導(dǎo)較小且頻率響應(yīng)性能較差。對當(dāng)輸入共模電平低時,2個P溝道差分輸入對都同時開啟,這樣會導(dǎo)致差分對的尾電流在共模電平高和低時不相等,因此,這種電路在軌至軌輸入信號下很難實現(xiàn)恒定增益。輸入信號重整電路用來控制共模(CM)電平,但是由于反饋的引入,可能會導(dǎo)致信號的非線性。共模電平偏移是采用標(biāo)準(zhǔn)CMOS工藝制程來實現(xiàn)軌至軌輸入信號的好方法,但是要在超低電源電壓下工作(例如0.6 V),該還電路需要進行一些改進。

1 路結(jié)構(gòu)和工作原理

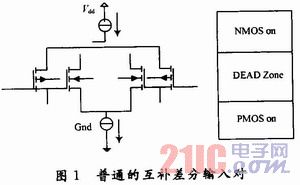

如圖1所示,普通的互補差分輸入對雖然能夠獲得軌至軌輸入信號,但是,其電源電壓不能低于2(VTH+VOD),其中表示VTH閾值電壓,VOD表示過驅(qū)動電壓,可以看出在中間部分,會出現(xiàn)截至區(qū)(Dead Zone)。

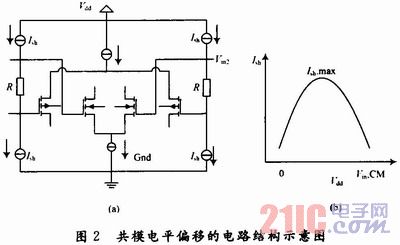

圖2是動態(tài)共模電平偏移(Level Shft)的電路結(jié)構(gòu)示意圖,其與文獻的不同之處是,對輸入共模電平在中間或者低電平時,僅僅PMOS差分對開啟,對輸入共模電平在高電平時,NMOS差分對開啟。在設(shè)計過程中,表明這種電路結(jié)構(gòu)更加適合于超低電源電壓下工作。互補差分對的輸入共模電平可以表示為:

![]()

其中Vin,n,cm和Vin,p,cm分別是內(nèi)部NMOS和PMOS差分對輸入端的共模電平,Vin,cm是外部輸入端Vin1和Vin2的共模電平。

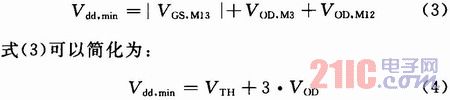

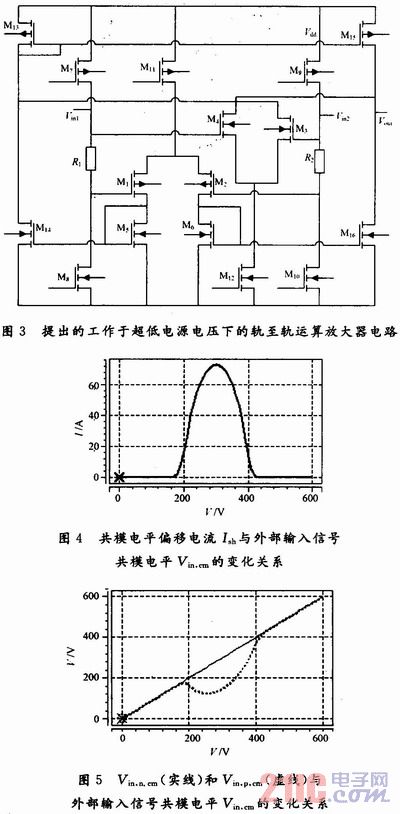

本文設(shè)計的低壓運算放大器的核心電路如圖3所示,該電路由電平偏移互補差分對(R1,R2,M1~M4)和對稱運算放大器(M5,M6,M13~M16)組成。圖3中,電平偏移電流產(chǎn)生電路(Level-shift Current Generator)與文獻中相同,其中Ish供給M7~M10。但在文獻中,采用了共源共柵結(jié)構(gòu),其在超低電源電壓下工作是不適合的。從圖3可以看出,該電路能夠工作的最小電源電壓是:

本設(shè)計中,對于0.6 V的電源電壓,在0.13μm CMOS工藝制程下,閾值電壓約為0.4 V,過驅(qū)動電壓設(shè)計為0.06 V。

2 模擬結(jié)果與討論

圖4為共模電平偏移電流Ish與外部輸入信號共模電平Vin,cm的變化關(guān)系。

圖5為內(nèi)部NMOS差分對輸入端的共模電平Vin,n,cm和PMOS差分對輸入端的共模電平Vin,p,cm與外部輸入信號共模電平Vin,cm的變化關(guān)系。可以看出,當(dāng)外部輸入信號共模電平處于中間區(qū)域時,Vin,p,cm會降低,此時PMOS輸入差分對會導(dǎo)通。因此該共模電平偏移輸入級實現(xiàn)了在低和中Vin,cm時PMOS輸入差分對導(dǎo)通,高Vin,cm時NMOS輸入差分對導(dǎo)通,即實現(xiàn)了軌至軌輸入。

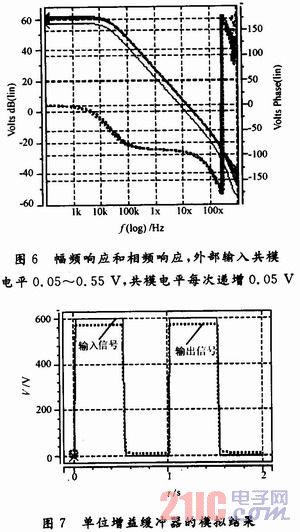

如圖6所示,在0.6 V電源電壓下,采用0.13 μmCMOS工藝制程,模擬得到的頻率響應(yīng)曲線,帶10pF電容負(fù)載時其性能為,功耗390μW,直流增益60 dB,單位增益帶寬22 MHz,相位裕度80°。圖7為單位增益緩沖器的模擬結(jié)果。結(jié)果表明,該運算放大器可以實現(xiàn)軌至軌輸入和輸出。

3 結(jié)語

在電源電壓為0.6 V下,模擬實現(xiàn)了軌至軌輸入和輸出運算放大器。采用0.13 μm CMOS工藝制程,其閾值電壓約為0.4 V和-0.4 V。設(shè)計過程中用到了輸入共模電平偏移技術(shù)和對稱運算放大器結(jié)構(gòu)設(shè)計。