摘要:介紹一種基于四通道ADC的高速交錯(cuò)采樣設(shè)計(jì)方法以及在FPGA平臺(tái)上的實(shí)現(xiàn)。著重闡述四通道高速采樣時(shí)鐘的設(shè)計(jì)與實(shí)現(xiàn)、高速數(shù)據(jù)的同步接收以及采樣數(shù)據(jù)的校正算法。實(shí)驗(yàn)及仿真結(jié)果表明,同步數(shù)據(jù)采集的結(jié)構(gòu)設(shè)計(jì)和預(yù)處理算法,能良好抑制并行ADC輸出信號(hào)因相位偏移、時(shí)鐘抖動(dòng)等造成的失配誤差。

關(guān)鍵詞:交錯(cuò)采樣;高速采樣時(shí)鐘;同步接收;信號(hào)處理

0 引言

高速、超寬帶信號(hào)采集技術(shù)在雷達(dá)、天文和氣象等領(lǐng)域應(yīng)用廣泛。高采樣率需要高速的模/數(shù)轉(zhuǎn)換器(ADC)。目前市場(chǎng)上單片高速ADC的價(jià)格昂貴,分辨率較低,且采用單片超高速ADC實(shí)現(xiàn)的數(shù)據(jù)采集對(duì)FPGA的性能和PCB布局布線技術(shù)提出了嚴(yán)峻的挑戰(zhàn)。

利用時(shí)間交叉采樣原理,對(duì)同一信號(hào)用多個(gè)相對(duì)較低速的ADC并行采樣是可行的。本文針對(duì)某項(xiàng)目要求構(gòu)建了四路采樣率為400 MHz的ADC和高性能FPGA接口處理平臺(tái),實(shí)現(xiàn)1.6 GHz數(shù)據(jù)采集。著重討論了ADC采樣時(shí)鐘的設(shè)計(jì)、數(shù)據(jù)同步接收和校正預(yù)處理等關(guān)鍵技術(shù),并提出軟硬件優(yōu)化方案。

1 采樣系統(tǒng)設(shè)計(jì)

1.1 多ADC并行采樣原理

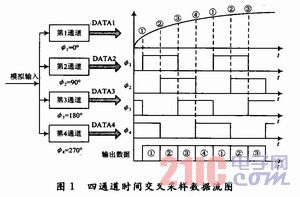

時(shí)間交叉采樣原理基于使用多片相對(duì)低速的并行ADC實(shí)現(xiàn)高速數(shù)據(jù)采集。m路ADC中每一片ADC的采樣頻率是整個(gè)系統(tǒng)采樣頻率的1/m,通過(guò)算法調(diào)整可使每一路通道時(shí)鐘具有固定相位差,采樣數(shù)據(jù)經(jīng)多路排序合并后,可達(dá)到一路ADC采樣速率m倍的效果。圖1是四路采樣時(shí)序結(jié)構(gòu),理想條件下各路時(shí)鐘相位依次相差90°。

1.2 時(shí)鐘設(shè)計(jì)

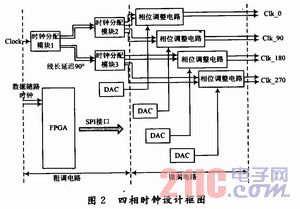

外部時(shí)鐘信號(hào)經(jīng)“時(shí)鐘分配模塊1”轉(zhuǎn)換成兩路同相差分時(shí)鐘信號(hào),一路送“時(shí)鐘分配模塊2”,另一路經(jīng)PCB走線移相90°后送“時(shí)鐘分配模塊3”。模塊2,3各輸出兩路180°相差時(shí)鐘信號(hào),最終得到依次相差近似90°的四路ADC采樣時(shí)鐘。

四路時(shí)鐘信號(hào)并非嚴(yán)格均勻相差90°,各路獨(dú)立進(jìn)入“相位調(diào)整電路”微調(diào)。相位微調(diào)電路由可編程移相LC網(wǎng)絡(luò)組成,F(xiàn)PGA獨(dú)立控制四路調(diào)整電路,使相位時(shí)延控制在200~300 ps范圍。時(shí)鐘分配及調(diào)整電路結(jié)構(gòu)如圖2所示。

1.3 數(shù)據(jù)接收和存儲(chǔ)

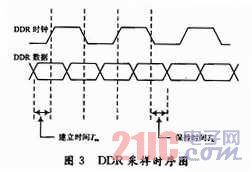

ADC輸出數(shù)據(jù)速率為400 MHz,與之相對(duì)應(yīng)的隨路時(shí)鐘為200 MHz,利用DDR方式接收數(shù)據(jù)。FPGA內(nèi)部PLL產(chǎn)生的四路時(shí)鐘信號(hào)的上升沿和下降沿都對(duì)輸入數(shù)據(jù)進(jìn)行實(shí)時(shí)采樣,數(shù)據(jù)與采樣時(shí)鐘之間保持一定的相位差,以滿足同步時(shí)序的數(shù)據(jù)建立時(shí)間(Tsu)和保持時(shí)間(Th),如圖3所示。

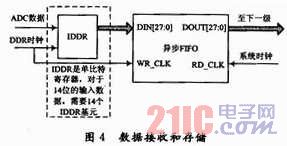

通過(guò)FPGA輸入模塊IDDR映射生成內(nèi)部寄存器接收數(shù)據(jù),并由異步FIFO實(shí)現(xiàn)內(nèi)部時(shí)序同步和存儲(chǔ)。ADC采樣數(shù)據(jù)的有效位是14 b,利用FPGA軟核生成的FIFO寬度和深度可分別設(shè)置為28 b和128,其中高14位[27:14]存儲(chǔ)奇數(shù)時(shí)刻的采樣數(shù)據(jù),低14位[13:0]存儲(chǔ)偶數(shù)時(shí)刻的采樣數(shù)據(jù),數(shù)據(jù)存儲(chǔ)如圖4所示。

2 數(shù)據(jù)預(yù)處理

2.1 時(shí)間交叉采樣引起的誤差

在圖1所示的多通道并行時(shí)間交叉采樣的數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)中,各個(gè)子通道間數(shù)據(jù)不可能完全匹配,主要會(huì)產(chǎn)生三種誤差:

(1)由于各個(gè)子通道ADC的增益不一致而引起的增益誤差(Gain Error);

(2)多相時(shí)鐘設(shè)計(jì)不完全理想以及PCB板線路走線延遲不一致引起的采樣時(shí)刻偏離帶來(lái)的時(shí)間相位誤差(Time Skew Error);

(3)各通道ADC基準(zhǔn)電壓不一致而引起的偏置誤差(Offset Error)。

以正弦信號(hào)為例,令輸入信號(hào)S=Acos(2πfint)+θ。其中:A,fin,θ分別為輸入信號(hào)的幅度、頻率和初始相位。若系統(tǒng)總采樣率為fs,經(jīng)m片ADC時(shí)間交叉采樣后第k個(gè)子通道的輸出為:

![]()

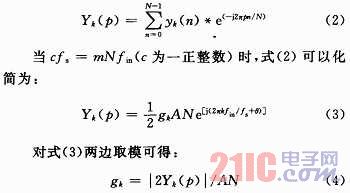

式中:0≤n

在本文的設(shè)計(jì)中,經(jīng)過(guò)模擬前端多相時(shí)鐘電路設(shè)計(jì),時(shí)間相位誤差可以忽略,且ADC的基準(zhǔn)電壓由同一電源供電,偏置誤差也可忽略,在此,利用DFT變換校正增益誤差。對(duì)于只有增益誤差的第k個(gè)子通道的輸出信號(hào)yk(n)=gkAcos[2πfin(mn+k)/fs+θ],做N點(diǎn)DFT得:

以第一個(gè)子通道的增益go為校正的起始標(biāo)準(zhǔn),則第k個(gè)子通道的相對(duì)增益誤差為,因此,經(jīng)過(guò)增益誤差校正輸出信號(hào)為:

3 實(shí)驗(yàn)仿真結(jié)果

圖5是經(jīng)過(guò)FPGA內(nèi)部映射之后的時(shí)序仿真圖,可以看到經(jīng)過(guò)精心設(shè)計(jì)的多相時(shí)鐘技術(shù)以及合理的同步接收使信號(hào)的采集效果良好。

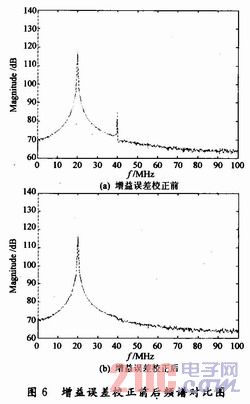

圖6是采集得到的數(shù)據(jù)經(jīng)過(guò)增益誤差校正前后的頻譜對(duì)比圖,可以看到在40 MHz處,雜散得到了明顯的抑制。其中,模擬輸入信號(hào)的頻率為20 MHz。

4 結(jié)語(yǔ)

針對(duì)高速并行ADC時(shí)間交叉采樣技術(shù)對(duì)多相時(shí)鐘信號(hào)的高要求以及采集數(shù)據(jù)的誤差,介紹了多相時(shí)鐘設(shè)計(jì)的一種方法和利用FFT技術(shù)實(shí)現(xiàn)對(duì)增益誤差的校正。通過(guò)實(shí)驗(yàn)仿真證明,該設(shè)計(jì)能夠有效提升數(shù)據(jù)采集系統(tǒng)的性能。