TFT液晶顯示器(LCD)具有功耗低、體積小、工作電壓低、使用壽命長、可以顯示復(fù)雜的文字及彩色圖像等優(yōu)點,在嵌入式設(shè)備中得到了廣泛的應(yīng)用,成為人機交互的重要方式。但是TFT液晶顯示器驅(qū)動具有數(shù)據(jù)量大、占用引腳多等特點,采用傳統(tǒng)的單片機驅(qū)動方式不僅會耗費大量的系統(tǒng)運行時間,降低系統(tǒng)效率,而且也會占用大量的I/O引腳。針對這種情況,本文提出了一種基于PicoBlaze軟核的TFT液晶顯示控制方案,能夠方便地實現(xiàn)FPGA對TFT液晶的顯示控制,具有較強的通用性和實用性。

1 PicoBlaze的體系結(jié)構(gòu)

8位嵌入式處理器PicoBlaze是Xilinx公司為Virtex系列FPGA、Spartan系列FPGA和CoolRunnerII系列CPLD設(shè)計的嵌入式處理器軟核,具有效率高、占用資源少等優(yōu)點,可以方便地嵌入到硬件系統(tǒng)設(shè)計中,實現(xiàn)與其他功能模塊的無縫連接。PicoBlage僅占用Spartan系列FPGA的96個Slice,占用XC3S50器件12.5%的資源,占用XC3S5000器件不到0.3%的資源;具有高達44~100 MIPS的指令執(zhí)行速度,具體速度取決于所選用的FPGA系列和器件速度等級。

PicoBlaze 8位嵌入式處理器提供了豐富、靈活的I/O口,它的外設(shè)也可以通過用戶自己配置,以滿足不同的系統(tǒng)設(shè)計要求。由于PicoB-laze提供了可綜合的HDL代碼,可以方便地移植到將來的FPGA架構(gòu)上,因此完全不用擔(dān)心當(dāng)前使用的器件淘汰后難以尋求替代產(chǎn)品。另外,PicoBlaze完全集成在FPGA中,減少了電路板空間和設(shè)計*費。

如圖1所示,PicoBlaze微處理器主要由以下幾個單元組成:16個8位通用寄存器;1 KB程序存儲單元;8位算術(shù)邏輯單元,帶有CARRY和ZERO標(biāo)志位;64字節(jié)內(nèi)部暫存RAM;256個輸入和256個輸出端口,方便擴展應(yīng)用;中斷控制單元。

圖1 PicoBlaze微處理器結(jié)構(gòu)圖

2 TFT液晶顯示模塊

TFT液晶模塊為320×240像素26萬色彩色圖形點陣式液晶,不僅可以顯示數(shù)字、字符等內(nèi)容,還可以顯示漢字和任意圖形。該模塊的控制芯片為SSD1289,與外部的連接只有16位數(shù)據(jù)線、5根控制線及電源。液晶模塊引腳功能如表1所列。TFT液晶模塊的讀寫時序滿足標(biāo)準(zhǔn)的8080并行時序,F(xiàn)PGA只要通過這些數(shù)據(jù)線和控制線按照相應(yīng)的時序進行讀寫,即可實現(xiàn)對模塊的顯示控制。

表1 液晶模塊引腳功能

3 軟硬件設(shè)計

3.1 PicoBlaze匯編程序設(shè)計

由于TFT液晶模塊內(nèi)置了SSD1289控制芯片,并且其讀寫時序滿足標(biāo)準(zhǔn)的8080并行時序,因此,在PicoBlaze程序設(shè)計中模擬其讀寫時序即可實現(xiàn)對TFT液晶模塊的控制。要通過軟件模擬8080并行讀寫時序,主要有兩項關(guān)鍵技術(shù):一項是對端口的高低電平進行控制;另一項是編寫軟件延時子程序。

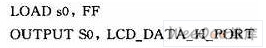

對端口的電平控制,可以通過OUTPUT命令方便地實現(xiàn)。比如:

可以向LCD_DATA_H端口輸出數(shù)據(jù)0xFF。

PieoBlaze沒有提供相應(yīng)的位操作指令,因此,對PieoBlaze端口的位操作可以通過下列程序?qū)崿F(xiàn):

上述程序?qū)崿F(xiàn)了對LCD_CTRL_PORT的bit0進行置“1”和清“0”操作,且不影響其他位。每次進行端口輸出前,將端口狀態(tài)從寄存器sF中讀出;而每次端口輸出完成后,將當(dāng)前端口狀態(tài)保存到寄存器sF中。

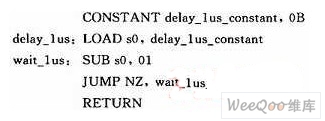

軟件延時子程序可以通過循環(huán)來實現(xiàn)。PicoBlaze的所有指令均為雙周期指令,當(dāng)系統(tǒng)工作頻率為50 MHz時,每條指令的執(zhí)行時間為40 ns。因此,通過調(diào)用下面的子程序即可實現(xiàn)1μs延時:

其中,delay_lus_constant=(clock_rate-6)/4,這里clock_rate為50。實現(xiàn)了端口位操作和軟件延時功能,即可按照8080并行讀寫時序編寫發(fā)送命令子程序。其程序代碼如下:

3.2 PicoBlaze與FPGA的邏輯接口

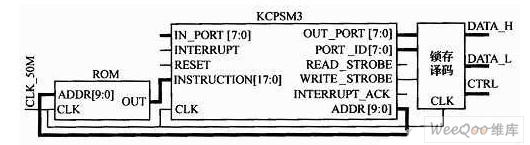

PicoBlaze與FPGA的邏輯接口主要在FPGA邏輯設(shè)計中例化PicoBlaze單元,將其與程序ROM相連,并完成輸入、輸出端口的鎖存譯碼。其接口示意圖如圖2所示。

圖2 接口示意圖

PicoBlaze的匯編程序經(jīng)匯編工具KCPSM3.exe編譯后,將其程序代碼填充到由BLOCK RAM組成的程序ROM中,在FPGA邏輯設(shè)計中,將程序ROM和PicoBlaze模塊KCPSM3的對應(yīng)引腳相連即可。鎖存譯碼單元在每個有效時鐘沿,在WRITE_STROBE的使能控制下對PORT_ID進行譯碼,并將OUT_PORT上的數(shù)據(jù)鎖存到相應(yīng)的寄存器中。本設(shè)計包含3個端口,分別是數(shù)據(jù)線高8位DATA_H、數(shù)據(jù)線低8位DATA_L和控制線CTRL,其中CTRL的bit0~bit4分別表示RS、RD、RESET、WR和CS。

在FPGA邏輯中完成PieoBlaze的例化和相關(guān)邏輯設(shè)計后,即可用Xilinx的集成開發(fā)工具ISE進行綜合、實現(xiàn)和下載驗證。綜合結(jié)果顯示,本設(shè)計共占用了102個Slice和1個RAMBl6S單元,僅占XC2VP30-7FF896總Slice數(shù)和BRAM單元的1%。最后,將生成的比特流下載到Xilinx XUP Virtex-II PRO開發(fā)板上進行驗證。結(jié)果表明,能夠正確驅(qū)動TFT液晶顯示單種或多種顏色,達到了預(yù)期目標(biāo)。經(jīng)測算,當(dāng)系統(tǒng)時鐘為50 MHz時,全屏刷新一次約需55.4 ms,具有較高的實時性。如果將系統(tǒng)時鐘提高到100 MHz,還可以進一步加快刷新速度。

結(jié)語

本文設(shè)計的基于PicoBlaze軟核的TFT液晶顯示控制方案,已在XilinxXUP Virtex-II PRO開發(fā)板上進行了驗證,取得了良好的效果。通過本設(shè)計方案可以看出,PicoBlaze是一個功能強大、應(yīng)用靈活的8位嵌入式軟核處理器,可用于實現(xiàn)非關(guān)鍵時序的復(fù)雜控制功能,而其他關(guān)鍵時序和數(shù)據(jù)通道功能則需FPGA邏輯來實現(xiàn),二者有機結(jié)合將使得系統(tǒng)設(shè)計更加方便、靈活。