0.引言

由于具有高功率增益#高效率及低成本等優(yōu)點(diǎn),射頻LDMOS(lateral diffused metal oxide semicONductor traNSiSTor)器件被廣泛應(yīng)用于移動(dòng)通信基站、雷達(dá)、導(dǎo)航等領(lǐng)域。為了提高LDMOS擊穿電壓!增大輸出功率,采用了各種各樣的改進(jìn)結(jié)構(gòu),如SUPER-JUNCTION、漂移區(qū)變摻雜、RESURF和表面形成G降場(chǎng)層技術(shù)等,其中最為常用且簡(jiǎn)單有效的工藝方法就是在漂移區(qū)上部使用金屬場(chǎng)極板。場(chǎng)極板電容作為L(zhǎng)DMOS器件寄生電容的主要組成部分,是決定器件功率增益及截止頻率的一個(gè)重要因素。

為了解決常規(guī)金屬場(chǎng)極板結(jié)構(gòu)LDMOS(CFP-LDMOS)器件寄生電容大的缺點(diǎn)!本文提出分布式金屬源場(chǎng)極板結(jié)構(gòu)LDMOS器件(DFP-LDMOS)分布式源場(chǎng)極板結(jié)構(gòu)在工藝上易于實(shí)現(xiàn),并在不影響器件擊穿電壓的前提下,能有效減小器件寄生電容,提升器件射頻性能。

1.器件結(jié)構(gòu)及工藝流程

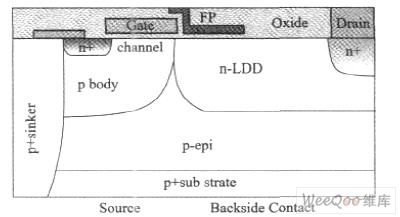

圖1所示為射頻LDMOS器件剖面圖,本文所設(shè)計(jì)的DFP-LLDMOS器件以傳統(tǒng)LDMOS器件結(jié)構(gòu)為基本框架,并應(yīng)用了分布式金屬源場(chǎng)極板技術(shù)。

圖1 射頻LDMOS器件剖面圖

全文PDF下載:分布式源場(chǎng)極板結(jié)構(gòu)射頻LDMOS器件的設(shè)計(jì).pdf