隨著諸如無線、有線和醫(yī)療/圖像處理應(yīng)用的帶寬需求不斷提高,設(shè)計師們必須依賴必要的工具集來獲得其所需的實(shí)時信號處理功能。在無線領(lǐng)域,例如現(xiàn)有的3G 網(wǎng)絡(luò)覆蓋,如HSPA+和EV-DO(即3G+)以及現(xiàn)在新興的4G部署,主要的關(guān)注焦點(diǎn)在于數(shù)據(jù)吞吐量和回傳的要求。它們要能夠支持迅速增長的用戶群,以及使用這些技術(shù)實(shí)現(xiàn)的無數(shù)視頻和數(shù)據(jù)應(yīng)用。因此就需要高速處理能力,以及同樣重要的高度可靠、高吞吐量和低延遲的接口協(xié)議,來支持這些應(yīng)用中所必需的各種DSP(DSP farm)、協(xié)同處理和橋接應(yīng)用的需要。并且與大多數(shù)系統(tǒng)相同,成本和功耗也同樣非常重要。DSP和網(wǎng)絡(luò)處理單元(NPU)器件,加上支持第二代串行RapidIO(SRIO)的低成本、低功耗FPGA,可以為滿足這些挑戰(zhàn)提供一個理想的平臺。

第二代SRIO

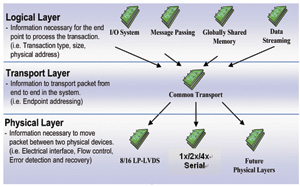

RapidIO規(guī)范是為各種終端定義的一種基于分組的技術(shù),它最初是用于連接其他終端的數(shù)據(jù)包和交換的處理。如圖1所示,該協(xié)議棧是一個三層協(xié)議規(guī)范,分為物理層協(xié)議、數(shù)據(jù)包傳輸(路由)層協(xié)議,以及邏輯層中的多種傳輸類型。

圖1 RapidIO協(xié)議棧

總體來看,第二代規(guī)范主要增加了對5/6Gb/s串行數(shù)據(jù)速率(SERDES)和用于高速串行通道的2x線路配置(與之前v1.3版本規(guī)范中僅支持1x/4x相比)的支持。正如前文所述,重點(diǎn)是在不犧牲設(shè)計的成本或功耗預(yù)算的情況下,提高性能,因此本文的重點(diǎn)在于介紹第二代規(guī)范的2x功能。這是一個關(guān)鍵的增強(qiáng)功能,因?yàn)樵谠S多情況下,系統(tǒng)需要比一條3.125Gb/s線路提供更大的吞吐量,但是使用4x 線路配置又顯得多余了。這就是現(xiàn)在2x SERDES 線路配置可以提供的一個有效解決方案,讓設(shè)計人員選擇仍然使用一個低成本、低功耗的FPGA解決方案,例如Lattice ECP3,并且還能支持大多數(shù)的應(yīng)用高達(dá)4x的線路配置,速率高達(dá)3.125Gb/s。

FPGA的可編程性和靈活性在邏輯層發(fā)揮了很大的作用,可以實(shí)現(xiàn)多種通信技術(shù)。如圖1所示,有4種數(shù)據(jù)傳輸協(xié)議。它們是直接I/O訪問、消息傳遞、GSM和數(shù)據(jù)流。邏輯層可以進(jìn)行定制,這取決于系統(tǒng)架構(gòu)/要求,以確定SRIO終端如何進(jìn)行數(shù)據(jù)交換。圖1顯示了RapidIO規(guī)范表示的協(xié)議棧。

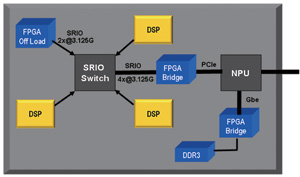

圖2顯示了如何使用低成本的可編程平臺來實(shí)現(xiàn)協(xié)議棧。物理層和傳輸層使用標(biāo)準(zhǔn)的軟IP核實(shí)現(xiàn),但邏輯層還剩下許多可供用戶定制的特性,以滿足特定的設(shè)計要求。

圖2 FPGA實(shí)現(xiàn)示例

低成本、低功耗擁有SRIO功能的FPGA的作用和優(yōu)勢

如上所述,許多處理都由于DSP和NPU而失敗,而通常情況下,它們兩者的分工不同。DSP應(yīng)用,盡管也進(jìn)行密集型處理,但往往需要更多的中斷驅(qū)動(如門鈴),因?yàn)樗鼈兪窃谔幚黻嚵兄袑?shí)現(xiàn)的,或者要接口到一個SRIO開關(guān)或終端——可能甚至要提供從SRIO到另一個基于SERDES的協(xié)議,如GbE或PCIe的橋接機(jī)制。而NPU更多地扮演了一個警察的角色來進(jìn)行數(shù)據(jù)處理,主要負(fù)責(zé)通信量和隊列處理。如圖3中的示例所示,說明了低成本、低功耗FPGA可以如何協(xié)助實(shí)現(xiàn)一個成功且有效的系統(tǒng)解決方案。

圖3 FPGA應(yīng)用示例

FPGA因其固有的靈活性和快速的產(chǎn)品上市時間的優(yōu)勢,超越了ASIC而長期受到市場歡迎,但是最近,這些優(yōu)勢只能通過使用高級的高端器件才能實(shí)現(xiàn),這就提高了成本和功耗預(yù)算。之前,低成本、低功耗FPGA僅限于“接口邏輯”和“錯誤修正”應(yīng)用。然而,隨著FPGA的價值定位大大地擴(kuò)展,現(xiàn)在已不再是如此。為了支持處理需求,保持嚴(yán)格的成本和功耗預(yù)算,F(xiàn)PGA的架構(gòu)已經(jīng)經(jīng)歷了發(fā)展變化,顯著地提高了性能、特性和邏輯密度,并且以比傳統(tǒng)FPGA更低的功耗和價格來實(shí)現(xiàn)。增強(qiáng)的功能,如集成的SERDES、高速嵌入式DSP塊、DDR3存儲器支持和嵌入式存儲器功能,已成為處理設(shè)計中的關(guān)鍵組成部分。系統(tǒng)工程師和設(shè)計工程師現(xiàn)在能夠利用這些可編程平臺實(shí)現(xiàn)復(fù)雜的信號路徑應(yīng)用,支持RRH和基帶處理功能,以及有線和圖像處理應(yīng)用,并且與傳統(tǒng)、高端的帶有SERDES功能的FPGA產(chǎn)品相比,具有更低的功耗和成本。

小結(jié)

系統(tǒng)設(shè)計人員將繼續(xù)面臨設(shè)計更高性能系統(tǒng)并同時保持較低的系統(tǒng)構(gòu)建和運(yùn)營成本的壓力。而這種壓力還將繼續(xù)延續(xù)下去。

過去,F(xiàn)PGA在系統(tǒng)設(shè)計中發(fā)揮了重要作用,但現(xiàn)在還需要新的性能,同時需要降低整個系統(tǒng)的構(gòu)建和運(yùn)營成本。功能豐富、低成本的FPGA實(shí)現(xiàn)了快速的產(chǎn)品上市時間與較短的投資回報周期,并且擁有能夠適應(yīng)不斷發(fā)展的標(biāo)準(zhǔn)的靈活性和性能。系統(tǒng)/設(shè)計工程師現(xiàn)在還擁有了一個令人興奮的、改進(jìn)的工具集來解決不斷演進(jìn)的信號處理市場的挑戰(zhàn)。