摘 要: 介紹一種可在現(xiàn)代小衛(wèi)星上應(yīng)用的高(低)位交叉并行存儲系統(tǒng),并給出了該存儲系統(tǒng)控制器的FPGA實現(xiàn)。該系統(tǒng)的應(yīng)用將極大地增強星上計算機的數(shù)據(jù)通信和圖象處理的能力,并提高整個系統(tǒng)的可靠性。

關(guān)鍵詞: 現(xiàn)代小衛(wèi)星 星載計算機 并行存儲系統(tǒng) FPGA 硬件描述語言

現(xiàn)代小衛(wèi)星,通常指80年代以后發(fā)展起來的小衛(wèi)星。它建立在微電子技術(shù),計算機(包括軟件)、微型光學(xué)和機械、輕型復(fù)合材料及高精機械加工的基礎(chǔ)上,是航天高技術(shù)發(fā)展的產(chǎn)物。雖然現(xiàn)代小衛(wèi)星的體積和重量很小,成本和風(fēng)險都很低,但由于選用了高新技術(shù),整個小衛(wèi)星的容量和性能,即小衛(wèi)星的功能密度是很高的。而且小衛(wèi)星組成星座可拓寬全新的應(yīng)用領(lǐng)域,能滿足通訊、遙感、對地觀測、科學(xué)技術(shù)試驗及軍事等各方面的需求。因此,現(xiàn)代小衛(wèi)星已作為大衛(wèi)星的必要補充在上述領(lǐng)域顯示出特有的優(yōu)勢,引起了世界各國,包括許多發(fā)展中國家和尚無衛(wèi)星研制能力的中小國家的普遍重視。

然而,近地空間和大氣環(huán)境影響著空間系統(tǒng)的規(guī)模、質(zhì)量、復(fù)雜性、可應(yīng)用的高科技技術(shù)和成本,強烈地影響空間系統(tǒng)的運行性能和工作壽命。一些空間環(huán)境的相互影響也限制了空間系統(tǒng)技術(shù)潛力的發(fā)揮,使部件或分系統(tǒng)工作不正常,甚至損壞。等離子環(huán)境,特別是處于對地靜止軌道的等離子環(huán)境,能使裝在衛(wèi)星外表面的設(shè)備和部件不均勻帶電,這些表面電荷產(chǎn)生的電壓可能超過擊穿電壓,從而導(dǎo)致靜電放電,足以毀壞電子元器件。許多高能空間輻射甚至深入到絕緣器件內(nèi)部,在絕緣電纜和線路板中產(chǎn)生靜電放電。這種體電荷能干擾分系統(tǒng)信號或中斷電子器件的正常工作。輻射帶中的俘獲粒子、太陽耀斑質(zhì)子和銀河宇宙射線能在微電子器件中誘發(fā)單粒子翻轉(zhuǎn)事件。這種高能輻射的總劑量效應(yīng)降低了微電子器件、太陽電池陣和敏感器件的性能。因此,為保證整個系統(tǒng)的正常運轉(zhuǎn)和壽命,很多地方都必須選用宇航級的器件和進行冗余設(shè)計。

單就星載計算機而言,到目前為止,高集成密度、高性能的CPU和內(nèi)存還沒有相應(yīng)的宇航級器件,在星上用的最多的還是8086和1750A等核加固的、抗輻射的、低帶寬、低MIPS的CPU,靠單片CPU很難滿足現(xiàn)代和未來小衛(wèi)星星上自主管理、自主定規(guī)、對地觀測圖象的壓縮和傳輸、硬件功能軟件化等諸多要求;而且單片CPU一旦損壞,將導(dǎo)致整個衛(wèi)星失效,又由于其價格極其昂貴,采用冗余的方案勢必大大提高小衛(wèi)星的成本。而在采用多CPU并行處理技術(shù)后,不僅可以滿足星上計算機數(shù)據(jù)處理能力的要求,而且增加了整個系統(tǒng)的可靠性。一到兩片CPU的損壞不致引起整個衛(wèi)星的失效,至多在系統(tǒng)重配置后損失一些性能,甚至可以在保證一定可靠性的前提下,考慮采用軍用級的、價格相對便宜,密度和性能都較高的CPU。

圍繞小衛(wèi)星體積小、重量輕和價格低廉的特點,一個多CPU共享內(nèi)存的系統(tǒng)(CPU仍然采用有相應(yīng)宇航級器件的8086)將是比較合適的選擇。同時為了提高共享內(nèi)存的數(shù)據(jù)通信帶寬,使其不成為整個系統(tǒng)的瓶頸,本文提出了一個用ASIC設(shè)計一個共享總線開關(guān)網(wǎng)絡(luò)(簡稱SBSN,下同),組合成Omega網(wǎng)絡(luò)的方案,以消除對某一組內(nèi)存的總線競爭,實現(xiàn)多CPU對共享分組存儲系統(tǒng)的低位交叉并行訪問。

1 SBSN實現(xiàn)的Omega網(wǎng)絡(luò)

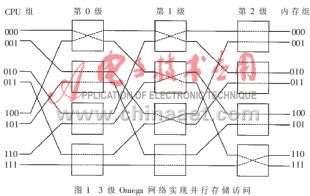

SBSN是一個2×2的開關(guān),可以級聯(lián)使用以實現(xiàn)2n個CPU和2n個內(nèi)存組的連接,這樣的連接共有N級,從輸入到輸出依次編為0~N-1,通過對二進制目的內(nèi)存組的編碼來控制數(shù)據(jù)路徑:從高位開始的第I位為0時,第I級的2×2開關(guān)的輸入端與上輸出端連接,否則輸入端與下輸出端連接(參見圖1)。

從理論上說,采用SBSN,N(=2k,k為正整數(shù))個CPU一次訪問通過只能占10.16%,所有其它的置換將引起阻塞。但盡管如此,N個CPU的Omega網(wǎng)絡(luò)實現(xiàn)非阻塞連接最多需要通過的次數(shù)為log2N=k,從總體上講,Omega網(wǎng)絡(luò)的采用能增加內(nèi)存總線的帶寬,大大提高總線數(shù)據(jù)的吞吐能力。

2 SBSN的設(shè)計與實現(xiàn)

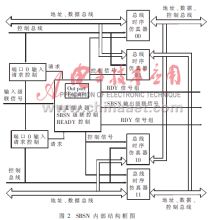

作為共享總線開關(guān)網(wǎng)絡(luò),SBSN主要是解決總線之間的共享競爭與沖突死鎖,將來自多個CPU的內(nèi)存讀寫信號分配到相應(yīng)的內(nèi)存模塊組。其內(nèi)部結(jié)構(gòu)框圖如圖2所示。

為了描述CPU間的共享與競爭,我們把CPU對內(nèi)存組的訪問分為HOLD,READY,RUN這三種關(guān)系。當(dāng)一個CPU進入總線讀寫之后,SBSN在總線周期的前兩個時鐘將CPU發(fā)送到總線上的數(shù)據(jù)進行鎖存:如果數(shù)據(jù)通路已被占用,當(dāng)前CPU就會進入HOLD狀態(tài),直到數(shù)據(jù)通路釋放。也就是說,如果有兩個或兩個以上的CPU要求同時對同一內(nèi)存組進行訪問的話,則只能有一個CPU獲得訪問權(quán),其它的必須等待該CPU總線讀寫周期的結(jié)束,在此之后,處于HOLD狀態(tài)的優(yōu)先級最高的CPU才會被釋放;如果通路暢通,SBSN經(jīng)過一個短暫的READY狀態(tài)后,在輸出端口仿真出CPU總線周期前兩個時鐘的時序信號,向下一級傳遞。在理想情況下,8個CPU可以同時對內(nèi)存進行訪問,即8個CPU都處在RUN狀態(tài)。

因為系統(tǒng)在運行過程中,總是由CPU主動向內(nèi)存發(fā)出讀或?qū)懙恼埱螅⒉淮嬖谝粋€環(huán)狀閉合的數(shù)據(jù)通路,所以不會有沖突死鎖的情況出現(xiàn)。

SBSN可以支持高位交叉和低位交叉這兩種對存儲系統(tǒng)的訪問方式:對20位地址總線來說,如果采取低位交叉尋址方式,那么系統(tǒng)目標(biāo)模塊的編碼由地址總線的A2,A1給出,A0和BHE信號用來對低8位和高8位尋址;如果采取高位交叉尋址方式,那么系統(tǒng)目標(biāo)模塊的編碼由地址總線的高四位決定,具體采用哪兩位,則取決于內(nèi)存的編址。低位交叉主要用于對共享內(nèi)存的并行訪問,高位交叉則主要用于一CPU對另一CPU的局部內(nèi)存(雙口)進行訪問。

采用硬件描述語言(HDL)的輸入方法進行SBSN的設(shè)計,雖然有可能會犧牲一些FPGA資源,但方便了在不同廠家的FPGA上進行邏輯綜合和實現(xiàn)的過程。因為宇航級的FPGA在XILINX和ACTEL都有生產(chǎn),但兩者實現(xiàn)的機理不同:XILINX的FPGA是SRAM型的,因此使用時還必須配備相應(yīng)的SROM以實現(xiàn)對FPGA片子的加電下載,但它可以進行多次刷新和修改,便于在設(shè)計階段進行調(diào)試;ACTEL的宇航級FPGA采用的熔斷絲技術(shù),只能一次編程下傳,實際應(yīng)用時不需任何輔助器件,但缺點是設(shè)計的每一次修改都必須換用新的FPGA片子。對于原理樣機階段而言,主要著眼于功能和時序的實現(xiàn),因此本文采用XILINX公司的商業(yè)級FPGA(XCS20-4PQ208C)進行設(shè)計與調(diào)試。XCS20-4PQ208C屬于SPARTAN系列,是XILINX公司新近推出的產(chǎn)品。與4000系列相比,SPARTAN中去掉了許多不常用的資源,在價格上可以便宜很多,對于SBSN來講,最重要的是滿足其多達140個用戶的I/O,因此采用XCS20-4PQ208C是融合了性能、容量和價格的一個綜合選擇。

對于其它將來可能在星上采用的高性能CPU,例如80386,由于其32位地址總線和32位數(shù)據(jù)總線是分開的,做在同一塊FPGA內(nèi)部將會面臨I/O數(shù)不足的問題。因此必須將地址總線、數(shù)據(jù)總線、控制總線分在兩塊相互耦合的片子上實現(xiàn),但其實現(xiàn)原理與SBSN是完全相同的。

SBSN是我們在提高星上計算機處理能力方面一個有益的嘗試。如果能以一個相對簡單、便宜而又高可靠性的系統(tǒng),達到3~4倍的加速比因子,那么,對小衛(wèi)星事業(yè)來說,將是一件很有意義的事情。

參考文獻

1 鄭緯民,湯志忠.計算機系統(tǒng)結(jié)構(gòu).清華大學(xué)出版社.1998

2 戴梅萼.微型計算機技術(shù)及應(yīng)用.北京:清華大學(xué)出版社,1991

3 Barry B.Brey著,陳誼譯.Intel系列微處理器結(jié)構(gòu)、編程和接口技術(shù)大全. 北京:機械工業(yè)出版社,1998

4 Victor P.Nelson,H.Troy Nagle, etc.Digital Logic Circuit Analysis & Design. Prentice-Hall International, Inc.1997

5 XILINX Inc.The Programmable Logic Data Book. 1999