1 DDR NAND閃存的特性

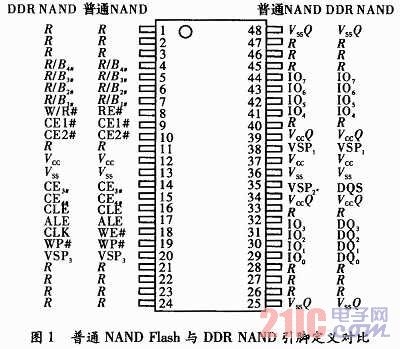

與傳統(tǒng)的48腳NAND Flash引腳定義不同,DDRNAND閃存不再分別劃分讀時鐘(RE#)和寫時鐘(WE#),而是將讀寫合為1個時鐘,即CLK,而用W/R引腳的高低來區(qū)分這次是讀操作還是寫操作,如圖1所示。數(shù)據(jù)I/O接口也改為正負(fù)雙沿采集的DQ數(shù)據(jù)線。如圖1中DDR NAND閃存部分所示,各引腳功能說明如下:

CE1#~CE4#:片選信號,低為使能。一個48腳的物理NAND Flash片子最多能同時包含(封裝)4個NAND Flash。

CLE:命令鎖存使能信號,高為使能。

ALE:地址鎖存使能信號,高為使能

CLK:時鐘信號。

W/R#:區(qū)分讀寫操作信號,高為寫,低為讀。

DQ0~DQ7:數(shù)據(jù)/地址/命令復(fù)用數(shù)據(jù)線。

R/B1#~R/B4#:NAND狀態(tài)信號線。

VCC,VCCQ:接電源。

VSS,VSSQ:接地。

R:無定義。

2 對DDR NAND閃存的軟件驅(qū)動操作

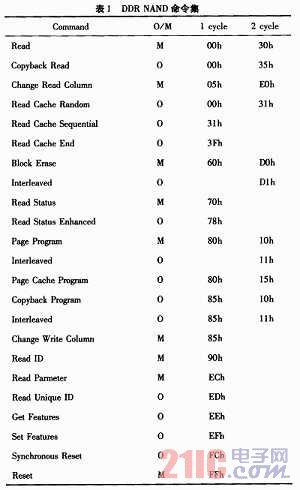

DDR NAND與普通NAND Flash一樣,遵從ONFI協(xié)議的命令集合,如表1所示。其中,O/M項為M的必選,為O的可選,也就是說標(biāo)有M的命令所有NAND Flash都支持,而標(biāo)有O的命令則為部分支持部分不支持。

下面分別以NAND Flash最重要最為常用的驅(qū)動接口:讀,寫,擦為例,分別說明DDR NAND的操作流程。

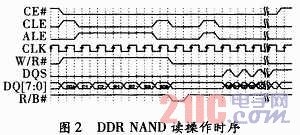

2.1 讀操作

DDR NAND的讀操作和寫操作一般都是以頁為單位操作的,與傳統(tǒng)的NAND Flash一樣,它允許在1個頁讀寫周期內(nèi)讀取1 Byte到data區(qū)與spare區(qū)大小之和這么多字節(jié)。讀取數(shù)據(jù)過程為:(1)先向DDRNAND發(fā)送讀命令00h。(2)然后接著發(fā)送需要讀取的DDR NAND的位置row地址和column地址。(3)接著發(fā)送讀確認(rèn)命令30 Hz,DDR NAND收到這個命令后會拉低RB信號線,然后開始工作,將相應(yīng)的一頁數(shù)據(jù)讀取到DDR NAND里的頁緩沖,讀完后把RB信號線拉高,產(chǎn)生一個RB中斷。(4)主控程序接收到RB中斷后,發(fā)送同步時鐘準(zhǔn)備信號,即CLE和ALE同時產(chǎn)生一個cycle。(5)接著就可以發(fā)送讀數(shù)據(jù)的clock cycle,每發(fā)送一個clock cycle就會在DDR NAND的頁緩沖FIFO中送出2 Byte數(shù)據(jù),上升沿一個,下降沿一個,因為DDR NAND是雙沿采數(shù)的,同時DDR NAND也會控制DQS信號線與data同步。(6)主控程序發(fā)送完讀數(shù)據(jù)的clock,讀操作結(jié)束。如圖2所示。

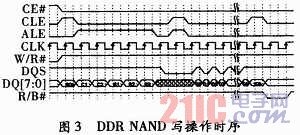

2.2 寫操作

在DDR NAND中,寫操作也叫編程。寫操作的單位也是頁,它的操作過程如下:(1)先向DDRNAND發(fā)送寫命令80 Hz。(2)然后接著發(fā)送需要寫入的DDR NAND的位置row地址和column地址。(3)發(fā)送同步時鐘準(zhǔn)備信號,即CLE和ALE同時產(chǎn)生一個cycle。(4)接著就可以發(fā)送讀數(shù)據(jù),發(fā)送數(shù)據(jù)是根據(jù)clock產(chǎn)生DQS信號,在DQS信號上下沿分別發(fā)送數(shù)據(jù)到DDR NAND。(5)發(fā)完一個page的數(shù)據(jù)后,接著發(fā)送寫確認(rèn)命令10 Hz,DDR NAND收到這個命令后會拉低RB信號線,然后開始工作,將相應(yīng)的一頁數(shù)據(jù)從DDR NAND里的頁緩沖中正式編程到DDR NAND中,待編程完畢后把RB信號線拉高,產(chǎn)生一個RB中斷,如圖3所示,此時寫操作已完成。

2.3 擦除操作

DDR NAND的擦除操作單位為block,擦操作比較特殊,它不涉及任何數(shù)據(jù),沒有用雙沿操作的地方,所以它的操作過程和時序跟普通NAND Flash是一樣的,操作過程如下:(1)先向DDR NAND發(fā)送擦命令60 Hz。(2)接著發(fā)送需要擦除的DDR NAND的位置,3 Byte的row地址。(3)發(fā)送擦確認(rèn)命令d0h,DDR NAND收到這個命令后會拉低RB信號線,然后開始工作,待擦除完畢后再把RB信號線拉高,產(chǎn)生一個RB中斷,一個block擦除完畢。

3 結(jié)束語

從市場方面了解到DDR NAND這種雙沿采數(shù)的新型NAND Flash有逐步取代原高端16 bit NANDFlash之勢,成為新的高端閃存。它具有更高的讀寫速率,不需要優(yōu)化代碼就能輕松突破存儲速度的瓶頸限制。