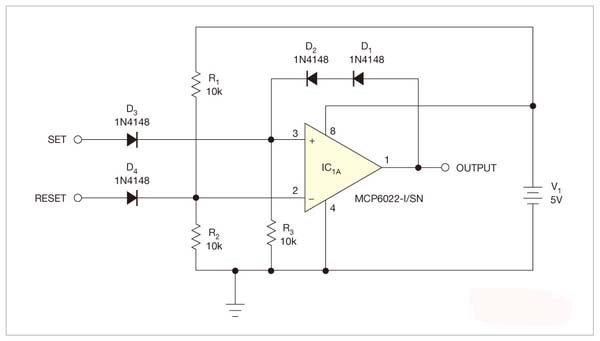

用兩個(gè)NAND或NOR門,可以做出一個(gè)置位/復(fù)位觸發(fā)器,或者也可以使用現(xiàn)成的置位/復(fù)位觸發(fā)IC,如74HC279四置位/復(fù)位鎖存器。這些方法的缺點(diǎn)是,它們需要占用大量的空間來(lái)組成觸發(fā)器。即使你只需要一只觸發(fā)器,也必須在方案中使用一只大IC封裝。不過(guò),如果你有一只空閑的軌至軌運(yùn)放,也能完成所需要的鎖存功能(圖1)。

這種方案對(duì)空間的需求低,因?yàn)檐壷淋壿斎?輸出的MCP6022是雙運(yùn)放封裝,這意味著可以用少量空間做出兩個(gè)置位/復(fù)位鎖存電路。如有必要,通過(guò)選擇適當(dāng)?shù)倪\(yùn)放,還可以在非標(biāo)準(zhǔn)電源電壓下運(yùn)行該電路。

圖1,當(dāng)為置位或復(fù)位輸入端施加一個(gè)正向脈沖時(shí),正反饋與二極管控制著運(yùn)放輸出高或低的鎖存。

用R1/R2分壓器將運(yùn)放的反相輸入設(shè)為2.5V。由于D4被反偏,該輸入端不能拉到低于2.5V。但可以將輸入端驅(qū)動(dòng)至邏輯高。串聯(lián)二極管D1和D2為運(yùn)放的非反相輸入端加正反饋, 如果輸出和置位輸入均為低,則R3拉低。

輸出為低時(shí),置位輸入加一個(gè)5V脈沖,正偏D3;D1和D2保持反偏。運(yùn)放非反相輸入端獲得的4.4V將輸出驅(qū)動(dòng)為高,正偏D1和D2 ,將非反相輸入端鎖存在3.8V,此電壓遠(yuǎn)高于反相輸入端的電壓,即使置位輸入端返回了低。接下來(lái),如果將復(fù)位輸入端驅(qū)動(dòng)為高,則反相輸入(為4.4V)就高于非反相輸入端的3.8V,使輸出為低。當(dāng)復(fù)位輸入回到低時(shí),D4反偏,反相輸入端的2.5V使輸出保持為低。注意,輸入脈沖必須有足夠的持續(xù)時(shí)間,以適應(yīng)運(yùn)放的延遲與轉(zhuǎn)換速率。

與真正的置位/復(fù)位鎖存不同的是,兩個(gè)輸入端同時(shí)為高電平會(huì)得到未知的結(jié)果。這種情況下,可以在置位輸入或復(fù)位輸入處串聯(lián)一只電阻,引入少許的電壓差,從而確保需要的邏輯狀態(tài)。CMOS邏輯是軌至軌驅(qū)動(dòng),可以直接與本電路接口。而用TTL作驅(qū)動(dòng)則需要在TTL輸出端加上拉電阻,以確保有足夠的輸入電壓。可能需要增加10kΩ電阻的值,以避免上拉電阻作負(fù)載。

所選運(yùn)放必須有軌至軌的輸出能力。使用無(wú)此功能的運(yùn)放也可以,但要根據(jù)需要增加電源電壓,針對(duì)所需邏輯電平補(bǔ)償輸出電壓。通過(guò)調(diào)節(jié)R1和R2以及采用低壓降二極管(如鍺管或肖特基管)可以改變觸發(fā)器的電平。

本電路有相對(duì)較低的輸入阻抗,但一般不會(huì)有問(wèn)題,因?yàn)榇蠖鄶?shù)邏輯輸出信號(hào)都可以驅(qū)動(dòng)此負(fù)載。根據(jù)需要調(diào)節(jié)電阻值,就可以改變輸入阻抗。