摘要:論述了基于麥克風" title="麥克風">麥克風陣列的聲源定位" title="聲源定位">聲源定位技術的基本原理,給出了利用FPGA" title="FPGA">FPGA實現系統(tǒng)各模塊的設計方法。重點介紹了其原理和模塊的電路實現,給出的基于FPGA設計實驗結果表明,系統(tǒng)最大限度發(fā)揮了FPGA的優(yōu)勢、簡化了系統(tǒng)設計、縮短了設計周期、符合設計要求。

關鍵詞:聲源定位;時延估計;FFT" title="FFT">FFT;CORDIC" title="CORDIC">CORDIC

聲源定位,即確定一個或多個聲源在空間中的位置,是一個有廣泛應用背景的研究課題。基于麥克風陣列的聲源定位技術在視頻會議、聲音檢測及語音增強等領域有重要的應用價值。

聲源定位算法目前主要有3類:第一類算法是基于波束形成的方法。這種算法能夠用于多個聲源的定位,但是它存在著需要聲源和背景噪聲先驗知識以及對初始值比較敏感等缺點;第二類算法是基于高分辨率譜估計的方法。這種算法理論上能夠對聲源方向進行有效估計,但是計算量較大,且不適于處理人聲等寬帶信號;第三類算法是基于到達時間差的方法。由于這種方法原理簡單,計算量較小,且易于實現,在聲源定位系統(tǒng)中得到了廣泛應用。根據以上介紹,本文決定選擇第三類即基于到達時間差的定位方法。

基于到達時間差聲源定位算法包括2個步驟:

1)先進行時延估計,從中獲得傳聲器陣列中相應陣元對之間的聲音到達時延。常用的方法有最小均方自適應濾波法、互功率譜相位法和廣義互相關函數法。

2)利用時延估計進行方位估計,主要方法有角度距離定位法、球形插值法、線性插值法和目標函數空間搜索定位法。與其他幾種方法相比,基于廣義互相關函數的方法計算量小、計算效率高。優(yōu)點明顯,故時延估計采用此方法。方位估計則采用精度適中、易于實現的角度距離定位法。

FPGA具有高速處理能力,而且開發(fā)靈活,易于在線系統(tǒng)升級,能較大縮短系統(tǒng)的開發(fā)周期。為此,采用Ahera公司的FPGA處理器件實現本系統(tǒng)。

1 系統(tǒng)的基本原理及流程圖

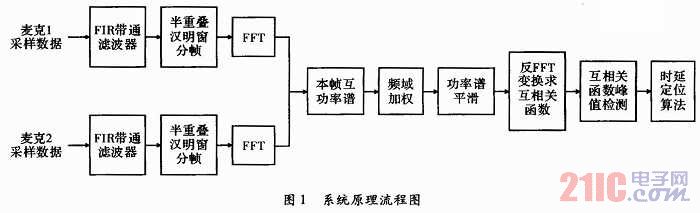

算法的結構流程如圖1所示,首先由麥克1和2獲得說話人的語音信號,再經過A/D采樣和低通濾波器,最后得到待處理輸入語音信號,可以分別記為x1(n)和x2(n)。

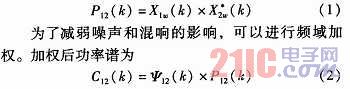

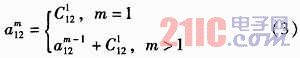

經過FIR帶通濾波器后,用半重疊漢明窗對x1(n)和x2(n)加窗可得X1w(n)和X2w(n),然后即可求得x1(n)和x2(n)的互功率譜為

為進一步突出峰值,在頻域加權后,可對麥克信號間的互功率譜平滑,得到

其中,m表示累加平滑的幀數。

接下來對求傅里葉反變換,即可以得到麥克1和2間的廣義互相關函數為

其峰值就是麥克1和2之間的時延。得到多對麥克間的時延后,由角度距離定位法,就可得到聲源位置。

2 各模塊設計實現

2.1 FIR帶通濾波模塊

為了消除噪聲和回聲干擾的影響,首先需要進行濾波。語音信號的帶寬是0.3~3.4 kHz,因而需要設計一個帶通濾波器濾除語音信號帶寬之外的噪聲。為了使處理過的信號相位不發(fā)生變化即保持線性相位,需要采用FIR濾波器。

這里采用切比雪夫逼近法,由Matlab濾波器設計工具求得濾波器的各系數,乘以1024進行量化,轉化為CSD編碼以提高其運行效率,最后由Verilog代碼實現。

2.2 半重疊漢明窗模塊

為了保證語音信號平穩(wěn)性,一幀信號的時間窗長度選為10~30 ms。而采樣器頻率為10 kHz,為了便于FFT處理選擇25.6 ms即幀長為256點。為了保證統(tǒng)計特征的連續(xù)性和得到更好的語音處理效果,各幀之間進行50%的重疊,即每次處理只更新12.8 ms的數據。這樣,一幀內的信號可以近似認為是平穩(wěn)的。

分幀是用可移動的有限長度窗口進行加權的方法實現,這就是用某窗函數w(n)乘以s(n),從而形成加窗的語音信號sw(n)=s(n)×w(n),其中窗函數的值存儲在內部存儲資源中。常用的窗函數有漢明窗與矩形窗,漢明窗比矩形窗的平滑效果更好,故選擇漢明窗,其表達式如式(5)所示

其中,N是幀長。

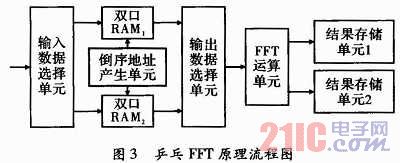

2.3 FFT運算模塊

由于語音信號是連續(xù)的實時采樣,為了能使傳來的語音信號連續(xù)不斷的處理,這里采用了乒乓結構,即采用兩個分別能存儲一幀數據的雙口RAM,第一個RAM在存儲新數據時,第二個RAM進行FFT運算,并存儲其結果。然后,第一個RAM進行FFT運算,并存儲其結果,第二個RAM存儲新的數據,這樣就保證了信號處理的連續(xù)性。

乒乓存儲時由倒序地址模塊產生倒序存儲地址,使RAM中存儲數據為倒序,為FFT運算做準備。為了加快運算速度,蝶形運算旋轉因子,先由Matlab軟件生成,量化為12位帶符號數,然后存儲在內部ROM里面。

整個FFT運算單元由狀態(tài)機設計完成,共由5個狀態(tài)完成;S1狀態(tài)輸出第一個操作數地址;S2狀態(tài)得到第一個操作數,輸出第二個操作數地址;S3狀態(tài)得到第2個操作數,計算出第一個結果;S4狀態(tài)寄存第一個結果,計算出第二個結果;S5狀態(tài)寄存第二個結果,產生下一級運算地址。

2.4 本幀互功率譜模塊

第一路信號FFT結果與第二路信號FFT結果的共軛相乘得到本幀互功率譜。

若第一路是r1+i1,第二路是r2+i2,其共軛為r2-i2,相乘時可用式(6),式(7)所示的計算方法,這樣可以減少一次乘法運算,節(jié)省內部資源

![]()

其中,R和I是本幀互功率譜的實部和虛部;r1和r2是FFT結果的實部;i1和i2是FFT結果的虛部。

2.5 頻域加權模塊

本幀互功率譜乘以存放在ROM中的加權函數,使互相關函數峰值更加突出。調用內部乘法器模塊即可完成。

2.6 功率譜平滑模塊

對加權模塊結果,進行連續(xù)數幀的累加以平滑互功率譜,使峰值便于檢測。調用內部加法器模塊即可完成。

2.7 反FFT模塊

對平滑結果進行反FFT運算,求得互相關函數。根據FFT原理,反FFT運算可借助于FFT模塊計算。即將FFT運算中旋轉因子取倒數,最后的輸出乘以1/N就可以用來計算反FFT。為防止運算過程中發(fā)生溢出,可將1/N分配到每一級蝶形運算中。由于1/N=(1/2)M,所以每級的每個蝶形輸出支路均有一相乘因子1/2,即右移一位即可。

2.8 峰值檢測模塊

對FFT結果求模即是求![]() 的值,然后求出其模值的峰值,即相應的語音信號時延值。

的值,然后求出其模值的峰值,即相應的語音信號時延值。

2.9 定位算法模塊

根據角度距離定位法,聲源相對原點的水平角θazimuth為

![]()

其中,a是麥克之間的間距;d是聲源到麥克對的距離差。

聲源相對原點的仰角φelevation為

![]()

其中,a是麥克之間的間距;d是聲源到麥克對的距離差。

由上可知,需要計算反余弦函數值確定出相應的角度值。反余弦函數是超越函數,可以用泰勒級數近似計算這個函數,但較為麻煩且精度不高,而CORDIC算法是由移位和加減運算組成,所以比較適合FPGA的實現,速度較快且具有較高的迭代精度。本系統(tǒng)使用高速9級流水線結構實現CORDIC算法。迭代關系如下

式(10)是迭代的初始條件,式(11)是根據本次坐標值判定下次迭代方向,式(12)~式(14)是下次迭代公式。

算法經過數次迭代后θ的值即是*****。實際中使用9級迭代,可以得到7位精度。最小角度精度為0.111 905。

3 模塊仿真和綜合報告

Quartus II是Altera公司開發(fā)的綜合性PLD軟件,內嵌綜合器和仿真器,可以完成從設計輸入到硬件配置的完整PLD設計流程。而且具有運行速度快、界面統(tǒng)一、功能集中、易學易用等特點。

本設計使用Quartus II8.0對各個模塊進行仿真驗證。通過仿真,驗證了各個系統(tǒng)模塊可以準確的工作,并完成了整個設計功能。選取Alte-ra公司Cyclone II系列中的EP2C35F484C8器件對整個程序進行時序仿真,其主要資源消耗為:總邏輯單元為3740/3 3216,總存儲單元為74 240/483 840,總管腳為387/475。總乘法器為16/35。仿真結果表明,本文所述實現方法結構可行,可以獲得良好的性能,其最高速率可以達到87.3 MHz,完全滿足系統(tǒng)要求。

4 結束語

本設計通過FPGA來實現整個系統(tǒng),充分利用了Altera公司FPGA產品高速大容量開發(fā)靈活方便等優(yōu)點,并使用QuartusⅡ開發(fā)環(huán)境所提供的庫資源,同時最大限度地利用和發(fā)揮了FPGA的優(yōu)勢,從而簡化了系統(tǒng)設計,縮短了設計周期。