本文的目的是設(shè)計(jì)一個(gè)生物信號(hào)傳感器的控制系統(tǒng),。在一些信號(hào)采集回路中,某些傳感器的最佳工作電壓隨著環(huán)境的變化而變化,,這就要求系統(tǒng)在正式采集有效信號(hào)前將傳感器調(diào)到最佳工作電壓,。這時(shí)系統(tǒng)不僅要求高速的數(shù)字信號(hào)處理能力,而且要求對(duì)前端多路傳感器的適時(shí)控制,,于是選擇由C5416和5633所組成的生物信號(hào)采集控制系統(tǒng),。以下重點(diǎn)分析SPI口的配置以及DSP通過(guò)SPI對(duì)進(jìn)行數(shù)據(jù)傳輸?shù)拇a實(shí)現(xiàn)。

2 芯片介紹

C5416屬于TI公司TMS320C54X系列DSP芯片,,是一種低功耗,、高性能的定點(diǎn)DSP芯片。它的主要特點(diǎn)有:運(yùn)算速度快,,可達(dá)160 MIPS,。優(yōu)化的CPU結(jié)構(gòu):內(nèi)部有1個(gè)40位的算術(shù)邏輯單元(ALU)、2個(gè)40位的累加器,、2個(gè)40位的加法器,、1個(gè)乘法器和1個(gè)40位的桶型移位器、有4條內(nèi)部總線和2個(gè)地址發(fā)生器,。多總線結(jié)構(gòu):包括3條獨(dú)立的16位數(shù)據(jù)總線和1條23位的地址總線,。低功耗方式:TMS320C5416DSP可以在3.3 V,1.6 V的低電壓下工作,,3種低功耗方式(IDLE1,,IDLE2和IDLE3)可以節(jié)省DSP功耗。智能外設(shè):包括軟件可編程等待狀態(tài)寄存器,、可編程PLL時(shí)鐘發(fā)生器,、1個(gè)16位的計(jì)數(shù)器,、6個(gè)DMA控制器、3個(gè)多通道緩沖串行口(McBSP0-2)和與外部處理器通信的HPI(Host Post Interface)接口,。

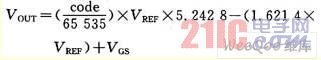

美國(guó)MAXIM公司生產(chǎn)的一種32通道高精度采樣保持D/A轉(zhuǎn)換器,。它內(nèi)含1個(gè)16位DAC、1個(gè)帶內(nèi)部時(shí)鐘的時(shí)序控制器,、1個(gè)片內(nèi)RAM以及32路采樣保持放大器,。其中DAC電路由2部分組成。在16位DAC中,,高4位可通過(guò)15個(gè)同值電阻組成的權(quán)電阻網(wǎng)絡(luò)完成相應(yīng)的轉(zhuǎn)換,,其余位的轉(zhuǎn)換則由1個(gè)12位R-2R梯形網(wǎng)絡(luò)來(lái)完成。其32路帶緩沖的采樣保持電路通過(guò)內(nèi)部保持電容來(lái)使輸出壓降維持在每秒1 mV的范圍內(nèi),,且不需要配置外部增益和偏置電路,。能提供最大200μV的分辨率和0.015%FSR的高精度轉(zhuǎn)換,其輸出電壓范圍為-4.5~9.2 V,。其理論輸出電壓由參考電壓,、增益以及輸入的編碼共同決定:

其中:code是5633輸入的16位二進(jìn)制代碼;VREF是MAX 5633的輸入?yún)⒖茧妷?;VGS是地的敏感輸入電壓,,通常直接接地。具有工作溫度范圍寬以及串行接口靈活等特點(diǎn),,適用于處理大量模擬數(shù)據(jù)輸出的場(chǎng)合。

3 系統(tǒng)工作模式

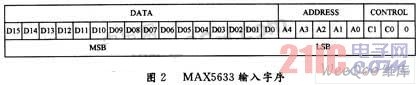

MAX 5633的轉(zhuǎn)換過(guò)程是先從串行數(shù)據(jù)端DIN送進(jìn)要轉(zhuǎn)換的16位數(shù)據(jù)D15~D0(高位在前,,低位在后),,然后送進(jìn)5位地址A4~A0(用這5位地址編碼來(lái)選擇輸出的通道號(hào))。地址的后2位是控制字C1和C0,,其中C1為1是立即更新模式,,為0則為觸發(fā)模式;C0為1表示選擇外部時(shí)鐘序列,,為0則選擇內(nèi)部時(shí)鐘序列,。C1,C0之后應(yīng)補(bǔ)1位0,。當(dāng)片選CS變低后,,系統(tǒng)將在每一個(gè)時(shí)鐘的上升沿送進(jìn)一位數(shù)據(jù)。送完最后一位數(shù)據(jù)(即第24個(gè)數(shù)據(jù)后)后片選CS變高,。而當(dāng)CS為高電平時(shí),,任何輸入數(shù)據(jù)都無(wú)效。

MAX 5633有3種工作方式分別為順序模模式,、立即更新模式和碎發(fā)模式,。其中順序模式為默認(rèn)工作模式,。通過(guò)設(shè)定C1=1將MAX 5633配置成立即更新模式。立即更新模式用于更新單個(gè)SRAM的內(nèi)容,,同時(shí)更新相應(yīng)的采樣保持放大器輸出,。在這種模式下,所選擇的通道輸出會(huì)在順序操作恢復(fù)前更新,。用戶可以通過(guò)設(shè)置IMMED或使C1為高電平選擇立即更新模式,。當(dāng)片選CS為低電平時(shí),原訪問(wèn)順序被打斷,。輸入字被存儲(chǔ)在對(duì)應(yīng)于被選擇通道的SRAM中,。此時(shí)DAC轉(zhuǎn)換和相應(yīng)的采樣保持對(duì)輸入串口完全透明。相應(yīng)的輸出通道將得到立即更新,。更新后,,時(shí)序?qū)⒒氐皆瓉?lái)中斷的SRAM地址重新開始順序更新。立即更新操作需要占用2個(gè)時(shí)序周期,,其中一個(gè)周期用來(lái)使時(shí)序控制器繼續(xù)完成正在進(jìn)行的操作,,另一個(gè)用來(lái)進(jìn)行新數(shù)據(jù)的更新。

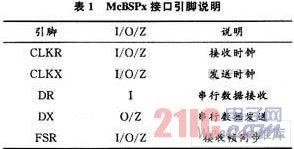

MAX 5633的輸入口為SPI接口,,要實(shí)現(xiàn)與DSP通信,,需將C5416的MCBSP0口配置成SPI口。MCBSP在結(jié)構(gòu)上可分為1個(gè)數(shù)據(jù)通道和1個(gè)控制通道,。表1給出了有關(guān)引腳的信號(hào)定義,。DX引腳負(fù)責(zé)數(shù)據(jù)的發(fā)送,DR引腳負(fù)責(zé)數(shù)據(jù)的接收,,另外4個(gè)引腳提供控制信號(hào)(時(shí)鐘和幀同步),。C5416通過(guò)片內(nèi)的外設(shè)總線訪問(wèn)串口的控制寄存器實(shí)現(xiàn)與MCBSP的通信和控制。

數(shù)據(jù)通道完成數(shù)據(jù)的收發(fā),。CPU和DMA控制器向數(shù)據(jù)發(fā)送寄存器(DXR)中寫入要發(fā)送的數(shù)據(jù),,從數(shù)據(jù)接收寄存器(DRR)讀取接收到的數(shù)據(jù)。寫入DXR的數(shù)據(jù)通過(guò)發(fā)送移位寄存器(XSR)移位輸出至DX引腳,。同樣,,DR引腳上接收到的數(shù)據(jù)先移位進(jìn)入接收轉(zhuǎn)換寄存器(RSR)中,然后被復(fù)制到接收緩沖寄存器(RBR),,RBR再將數(shù)據(jù)復(fù)制到DRR中,,最后等待CPU和DMA控制器讀取數(shù)據(jù)。這種多級(jí)緩沖方式使得片內(nèi)的數(shù)據(jù)搬移和外部數(shù)據(jù)的通信可以同時(shí)進(jìn)行,。

4 硬件連接電路

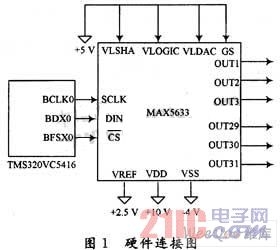

MAX 5633與C5416的硬件連接如圖1所示,。片選CS可控制MAX 5633是否被選中。CS為低后,,所有的轉(zhuǎn)換開始有效,。DIN為串行數(shù)據(jù)輸入,,SCLK為外部時(shí)鐘輸入。CLKSEL為時(shí)鐘選擇端,,當(dāng)C0或者該腳為高電平時(shí),,系統(tǒng)選擇外部時(shí)鐘模式,此時(shí)內(nèi)部時(shí)鐘模式將被關(guān)閉,。所給出的硬件連接圖為外部時(shí)鐘模式,。ECLK為外部時(shí)鐘模式控制引腳,可用于控制外部時(shí)鐘,。RST為輸入復(fù)位端,。DSP的BCLK0口與D/A的SCLK相連作為MAX 5633的外部時(shí)鐘,DSP的BDX0口與D/A的DIN相連作為MAX 5633的數(shù)據(jù)輸入,,DSP的BFSX0口與D/A的/CS相連作為MAX 5633芯片選擇端,。由于MAX 5633輸入?yún)⒖茧妷狠^多,為了盡量減小電壓的波紋對(duì)其精度的影響,,需要根據(jù)實(shí)際情況進(jìn)行濾波,。

5 軟件程序設(shè)計(jì)

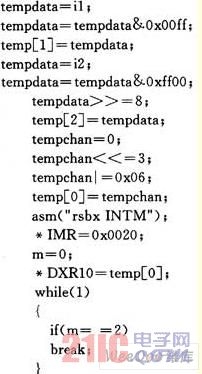

下面是針對(duì)硬件連接電路給出相應(yīng)的C語(yǔ)言程序。該程序?qū)CBSP0配置成時(shí)鐘停止模式(SPI)的主模式,。其中SPI的時(shí)鐘設(shè)置成1 MHz,,幀數(shù)據(jù)長(zhǎng)度為24位(如圖2所示)。幀的24位中C0,,C2為控制方式選擇位,;A0~A4為通道選擇位,可以選擇0~31共32個(gè)通道,;D0~D15為需要傳輸?shù)?6位數(shù)據(jù),。

由于SPI每次傳8位數(shù)據(jù),故傳輸16位數(shù)據(jù)需要傳3次,,先傳控制字,再傳數(shù)據(jù)的低8位,,最后傳數(shù)據(jù)的高8位,。系統(tǒng)可以通過(guò)改變tempchan選擇需要傳輸?shù)耐ǖ馈O旅媸莻鬏?6位數(shù)據(jù)的代碼

系統(tǒng)在while(1)循環(huán)過(guò)程中,,等待MCBSP0口的發(fā)送中斷,,再將剩下的2個(gè)字節(jié)發(fā)送出去。

6 結(jié)語(yǔ)

本文所介紹的方案已經(jīng)取得了預(yù)期的效果,,D/A的數(shù)據(jù)傳輸速率可達(dá)1 Mb/s,,并且還可以根據(jù)實(shí)際需要進(jìn)行提高。該方案已經(jīng)成功地運(yùn)用于系統(tǒng)中,,使傳感器穩(wěn)定在它的最佳工作電壓處工作,。該系統(tǒng)中DSP對(duì)D/A的控制傳輸無(wú)論從精度上還是速度上均完全能夠滿足系統(tǒng)的要求,。本系統(tǒng)所采用的模式以其高精度、多通道等特點(diǎn)將對(duì)以后的傳感器工作電壓隨環(huán)境變化的系統(tǒng)設(shè)計(jì)具有指導(dǎo)意義,,并對(duì)其他形式的信號(hào)采集控制系統(tǒng)的設(shè)計(jì)有借鑒作用,。