相較于透射式LCD,,LCoS具有光利用率高,、體積小、開口率高,、器件尺寸小等特點(diǎn),,可以很容易地實(shí)現(xiàn)高分辨率和微顯示投影。采用彩色LCoS屏顯示基于RGB的彩色圖像,,經(jīng)過光學(xué)成像系統(tǒng)投影到接收屏上,,實(shí)現(xiàn)計(jì)算全息圖像的三維顯示。

基于FPGA的顯示系統(tǒng)有以下優(yōu)勢(shì):第一,,LCoS尺寸小,,便于實(shí)現(xiàn)微投影,利用可靈活編程的FPGA器件作為驅(qū)動(dòng)控制器,,這樣就可以將其做成像普通投影儀一樣的微型投影設(shè)備,,使計(jì)算全息三維顯示擺脫了計(jì)算機(jī)和復(fù)雜光路的束縛,具有了更高的靈活性,,為其走出實(shí)驗(yàn)室提供了條件,。第二,因?yàn)樵趥鹘y(tǒng)空間光調(diào)制器上得到的圖像里含有物波和參考光的復(fù)共軛像,,形成了噪聲,,在FPGA上可以實(shí)現(xiàn)圖像濾波去噪,使得到的圖像更清晰,。第三,,F(xiàn)PGA是基于可編程邏輯單元的器件,,當(dāng)經(jīng)過綜合、布局布線,、時(shí)鐘約束的代碼燒錄到FPGA器件后,,F(xiàn)PGA就將算法代碼硬件化了,可以作為專用芯片工作,,其內(nèi)部信號(hào)延時(shí)完全是硬件級(jí)傳輸延時(shí),。在處理數(shù)據(jù)搬移和復(fù)雜的數(shù)學(xué)運(yùn)算以及一些循環(huán)操作時(shí),例如圖像的FFT變換,,F(xiàn)PGA硬件運(yùn)算要比軟件運(yùn)算快得多,,即利用FPGA器件實(shí)現(xiàn)對(duì)軟件算法的硬件加速。

基于以上原因,,本文設(shè)計(jì)了基于FPGA的LCoS驅(qū)動(dòng)代碼及圖像的FFT變換系統(tǒng),,為計(jì)算全息三維顯示圖像處理和顯示提供了硬件平臺(tái)。

1 系統(tǒng)設(shè)計(jì)

1.1 系統(tǒng)模塊框圖:

該系統(tǒng)采用CycloneⅢ EP3C5E144C8,,該芯片有5 136個(gè)LE,,95個(gè)用戶I/O,2個(gè)PLL,,以及46個(gè)嵌入式乘法器和423 936 b的內(nèi)部邏輯寄存器,。以它豐富的資源,完全可以作為L(zhǎng)CoS的驅(qū)動(dòng)控制器件,。顯示屏采用Himax的反射式LCoS屏HX7308,其分辨率為1 024×768,,可以支持256級(jí)灰度顯示,,具有內(nèi)置的行場(chǎng)驅(qū)動(dòng)電路,在外部輸入時(shí)鐘的上升沿和下降沿分別接收8b×4dots圖像數(shù)據(jù),,這保證了場(chǎng)頻可高達(dá)360 Hz,。

系統(tǒng)的整體框圖如圖1所示。

1.2 PLL及系統(tǒng)復(fù)位模塊

采用Altera的鎖相環(huán)IP核,,外部輸入時(shí)鐘為20 MHz,,經(jīng)倍頻后得到其他各模塊的驅(qū)動(dòng)時(shí)鐘,以及LCoS的驅(qū)動(dòng)時(shí)鐘信號(hào),。為防止系統(tǒng)異步復(fù)位時(shí)寄存器出現(xiàn)亞穩(wěn)態(tài),,設(shè)計(jì)了PLL的前級(jí)和后級(jí)D觸發(fā)器。因?yàn)殒i相環(huán)的locked引腳在鎖相環(huán)穩(wěn)定輸出后才會(huì)跳變?yōu)楦唠娖?,所以為保證其他模塊得到穩(wěn)定的時(shí)鐘信號(hào),,將locked引腳和外部輸入復(fù)位信號(hào)rst_n相與后作為整個(gè)系統(tǒng)的復(fù)位信號(hào)。

1.3 單口ROM模塊

利用FPGA內(nèi)部的M9K存儲(chǔ)器資源實(shí)現(xiàn)的單口ROM作為源圖像的數(shù)據(jù)存儲(chǔ)器,。將分辨率為176×144(QCIF)的256階灰度位圖圖像初始化到單口ROM里,,所需數(shù)據(jù)深度為25 344 B,。當(dāng)異步FIFO沒寫滿時(shí),單口ROM將按圖像存儲(chǔ)地址依次輸出圖像數(shù)據(jù)給FFT核做快速傅里葉變換,。經(jīng)過處理的圖像數(shù)據(jù)暫存到FIFO)里,,等待行場(chǎng)時(shí)序控制器模塊取用。

1.4 異步FIFO模塊

按其數(shù)據(jù)地址最高2位分為4個(gè)區(qū)間,,讀/寫指針分別對(duì)某一區(qū)間操作,,當(dāng)讀/寫指針相等時(shí)通過譯碼器產(chǎn)生FIFO已讀空或者已寫滿標(biāo)志信號(hào)。為避免地址信號(hào)變化時(shí)出現(xiàn)冒險(xiǎn)競(jìng)爭(zhēng)現(xiàn)象,,寫地址和讀地址指針都采用格雷碼編碼,。在讀空比較子模塊和寫滿比較子模塊里加入了FI-FO“將空”和“將滿”檢驗(yàn)機(jī)制,有效地保證了FIFO正確無誤的工作,。在寫時(shí)鐘wrclk的上升沿,,異步FIFO每個(gè)地址對(duì)應(yīng)的存儲(chǔ)單元里被寫入8bits數(shù)據(jù),在讀時(shí)鐘rdclk的上升沿,,F(xiàn)IFO四塊連續(xù)地址上的32bits數(shù)據(jù)輸出,,即讀FIFO的速率相當(dāng)于寫FIFO速率的4倍速。

1.5 I2C狀態(tài)機(jī)模塊

沒有滿足I2C配置條件時(shí),,狀態(tài)機(jī)處于空閑狀態(tài),,當(dāng)滿足I2C配置條件時(shí),狀態(tài)機(jī)在狀態(tài)標(biāo)志位的控制下依次輸出配置地址和配置數(shù)據(jù),。當(dāng)數(shù)據(jù)配置結(jié)束時(shí),,狀態(tài)機(jī)產(chǎn)生停止信號(hào),并拉高輸出引腳iic_config,,通知行場(chǎng)時(shí)序控制器模塊開始工作,,這樣保證了LCoS屏能在正確配置下工作。狀態(tài)機(jī)工作原理如圖2所示,。

1.6 行場(chǎng)時(shí)序控制器模塊

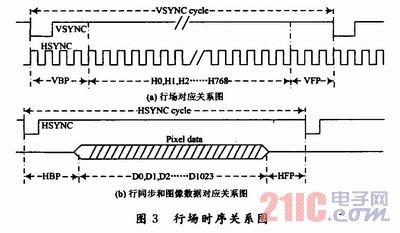

內(nèi)設(shè)水平計(jì)數(shù)器hcnt和垂直計(jì)數(shù)器vcnt,。由于顯示屏每個(gè)時(shí)鐘周期鎖存8個(gè)像素值,所以顯示1 024個(gè)像素值所需行周期為128個(gè)Tclk(行時(shí)鐘周期),。當(dāng)hcnt計(jì)數(shù)器值為HBP時(shí)表示行有效顯示區(qū)域開始,,hcnt計(jì)數(shù)器值為HBP128時(shí)表示行有效顯示區(qū)域結(jié)束,hent計(jì)數(shù)器值為HSYN-Ccycle時(shí),,完成一行顯示,,vcnt計(jì)數(shù)器加1。當(dāng)vcnt計(jì)數(shù)器值為VBP時(shí),,垂直有效顯示區(qū)域開始,,當(dāng)vcnt計(jì)數(shù)器值為VBP768時(shí),垂直有效顯示區(qū)域結(jié)束,當(dāng)vcnt計(jì)數(shù)器值為VSYNC cycle時(shí),,完成一幀圖像顯示,。行場(chǎng)時(shí)序關(guān)系如圖3所示。

1.7 FFT模塊

FFTV 9.1 IP核采用Cooley-Tukey基-2 DIF算法,,其FFT變換原始公式為:

![]()

因?yàn)椴捎昧藬?shù)據(jù)流模式,,經(jīng)過變換的數(shù)據(jù)可以連續(xù)輸出,即輸出數(shù)據(jù)不會(huì)因?yàn)閳D像數(shù)據(jù)的輸入而停止數(shù)據(jù)輸出,,同時(shí)輸入數(shù)據(jù)也不會(huì)因?yàn)樘幚砗蟮臄?shù)據(jù)正在輸出而停止繼續(xù)輸入,,保證了數(shù)據(jù)轉(zhuǎn)換和傳輸?shù)倪B續(xù)性,提高了數(shù)據(jù)處理的速度和效率,。因?yàn)镕FT通過異步FIFO向屏幕輸出數(shù)據(jù),,而FIFO的讀數(shù)據(jù)是寫數(shù)據(jù)的4倍速,假如讀時(shí)鐘和寫時(shí)鐘都為100 MHz,,那么有可能會(huì)在某一行里出現(xiàn)FIFO被取空,,而無法向屏幕輸出有效數(shù)據(jù)的情況。為保證FIFO向屏幕輸出圖像數(shù)據(jù)的連續(xù)性,,就要充分利用VBP,,VFP,HBP和HFP的時(shí)間,,在每一行的開始,,如果FIFO沒滿,那么啟動(dòng)FFT進(jìn)行數(shù)據(jù)轉(zhuǎn)換,。若圖像的分辨率為M×N并且在VBP期間FIFO已被寫滿,,則FIFO,F(xiàn)FT核,、行場(chǎng)周期以及圖像分辨率間關(guān)系的計(jì)算公式如下:

式中:Deepth是異步FIFO的數(shù)據(jù)深度,,單位為B;THSYNC cycle是行周期,;Tclk是異步FIFO,F(xiàn)FT核,、行場(chǎng)時(shí)序控制器模塊的驅(qū)動(dòng)時(shí)鐘周期,。當(dāng)△>O時(shí),系統(tǒng)會(huì)連續(xù)實(shí)時(shí)地處理圖像,;當(dāng)△

2 實(shí)驗(yàn)仿真結(jié)果和測(cè)量結(jié)果分析

圖4是采用Modelsim 6.5b進(jìn)行功能仿真的結(jié)果,。利用QuartusⅡV9.1自帶的TimeQuest Timing Analyzer進(jìn)行時(shí)序約束后,在實(shí)驗(yàn)板上的場(chǎng)信號(hào)測(cè)量結(jié)果如圖5所示,,場(chǎng)掃描頻率已達(dá)到368 Hz,,經(jīng)測(cè)量其他引腳輸出信號(hào)也均滿足時(shí)序要求。由于FPGA器件資源限制,,對(duì)圖像做了256點(diǎn)FFT變換,,經(jīng)實(shí)驗(yàn)驗(yàn)證,該設(shè)計(jì)能夠?qū)崿F(xiàn)圖像的實(shí)時(shí)處理,,代碼達(dá)到了預(yù)期設(shè)計(jì)效果,。

3 結(jié)語

采用Himax的LCoS屏HX7308BTJFA作為顯示器件,其尺寸為14.43mm×10.69mm,,大小可跟1枚1元硬幣相比擬,,很容易實(shí)現(xiàn)三維投影微顯示。因VerilogHDL有很強(qiáng)的可移植性,,便于以后對(duì)代碼的升級(jí)和維護(hù),。FPGA內(nèi)部資源畢竟有限,文中敘述可知,,若顯示分辨率較大的圖像,,光靠?jī)?nèi)部資源實(shí)現(xiàn)異步FIFO是不可能的,所以在此提出兩種方案:第一,,換一片性能較高的芯片,,滿足寫FIFO速率等于讀FIFO速率的要求,這樣就能達(dá)到讀/寫數(shù)據(jù)的動(dòng)態(tài)平衡,,保證了圖像的連續(xù)顯示,;第二,采用外部存儲(chǔ)器SDRAM存儲(chǔ)源圖像和FFT處理后的數(shù)據(jù),采用DDRII技術(shù)讀取數(shù)據(jù),,使讀/寫FIFO的速率匹配,。受FPGA芯片資源限制,該設(shè)計(jì)采用分辨率為176×144的圖像進(jìn)行了系統(tǒng)功能驗(yàn)證,,尚未實(shí)現(xiàn)圖像濾波以及FFT逆變換,,未來可將代碼移植在高端的FPGA芯片上繼續(xù)開發(fā)數(shù)據(jù)處理功能。