摘要:在FPGA" title="FPGA">FPGA設(shè)計(jì)中,,為了成功地操作,可靠的時(shí)鐘" title="時(shí)鐘">時(shí)鐘是非常關(guān)鍵的,。設(shè)計(jì)不良的時(shí)鐘在極限的溫度,、電壓下將導(dǎo)致錯(cuò)誤的行為。在設(shè)計(jì)PLD/FPGA時(shí)通常采用如下四種類型時(shí)鐘:全局時(shí)鐘,、門控時(shí)鐘,、多級(jí)邏輯時(shí)鐘和波動(dòng)式時(shí)鐘。多時(shí)鐘系統(tǒng)包括上述四種時(shí)鐘類型的任意組合,。

關(guān)鍵詞:FPGA,;時(shí)鐘;邏輯時(shí)鐘,;險(xiǎn)象

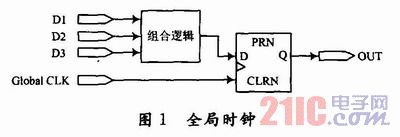

對(duì)于一個(gè)設(shè)計(jì)項(xiàng)目來說,,全局時(shí)鐘是最簡單和最可預(yù)測(cè)的時(shí)鐘,。在PLD/FPGA設(shè)計(jì)中最好的時(shí)鐘方案是由專用的全局時(shí)鐘輸入引腳驅(qū)動(dòng)的單個(gè)主時(shí)鐘去鐘控設(shè)計(jì)項(xiàng)目中的每一個(gè)觸發(fā)器。只要可能就應(yīng)盡量在設(shè)計(jì)項(xiàng)目中采用全局時(shí)鐘,。PLD/FPGA都具有專門的全局時(shí)鐘引腳,,它直接連到器件中的每一個(gè)寄存器。這種全局時(shí)鐘提供器件中最短的時(shí)鐘到輸出的延時(shí),。

1 全局時(shí)鐘

全局時(shí)鐘的實(shí)例如圖1所示,。圖1中定時(shí)波形示出觸發(fā)器的數(shù)據(jù)輸入D[1..3]應(yīng)遵守建立時(shí)間和保持時(shí)間的約束條件。建立和保持時(shí)間的數(shù)值在PLD數(shù)據(jù)手冊(cè)中給出,,也可用軟件的定時(shí)分析器計(jì)算出來,。如果在應(yīng)用中不能滿足建立和保持時(shí)間的要求,則必須用時(shí)鐘同步輸入信號(hào),。

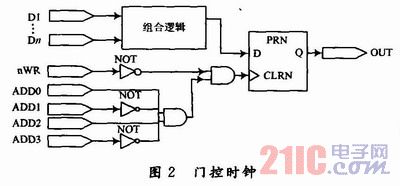

2 門控時(shí)鐘

在許多應(yīng)用中,,整個(gè)設(shè)計(jì)項(xiàng)目都采用外部的全局時(shí)鐘是不可能或不實(shí)際的。PLD具有乘積項(xiàng)邏輯陣列時(shí)鐘(即時(shí)鐘是由邏輯產(chǎn)生的),,允許任意函數(shù)單獨(dú)地鐘控各個(gè)觸發(fā)器,。然而,當(dāng)你用陣列時(shí)鐘時(shí),,應(yīng)仔細(xì)地分析時(shí)鐘函數(shù),,以避免毛刺。

通常用陣列時(shí)鐘構(gòu)成門控時(shí)鐘,。門控時(shí)鐘常常同微處理器接口有關(guān),,用地址線去控制寫脈沖。然而,,每當(dāng)用組合函數(shù)鐘控觸發(fā)器時(shí),,通常都存在著門控時(shí)鐘。如果符合下述條件,,門控時(shí)鐘可以象全局時(shí)鐘一樣可靠地工作,,圖2所示是一個(gè)可靠的門控時(shí)鐘電路。

(1)驅(qū)動(dòng)時(shí)鐘的邏輯必須只包含一個(gè)“與”門或一個(gè)“或”門,。如果采用任何附加邏輯在某些工作狀態(tài)下,,會(huì)出現(xiàn)競爭產(chǎn)生的毛刺。

(2)邏輯門的一個(gè)輸入作為實(shí)際的時(shí)鐘,,而該邏輯門的所有其他輸入必須當(dāng)成地址或控制線,,它們遵守相對(duì)于時(shí)鐘的建立和保持時(shí)間的約束。

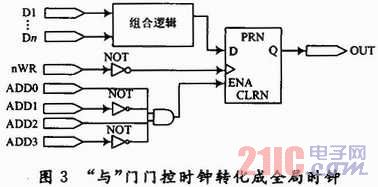

在設(shè)計(jì)中可以將門控時(shí)鐘轉(zhuǎn)換成全局時(shí)鐘以改善設(shè)計(jì)項(xiàng)目的可靠性,。圖3示出如何用全局時(shí)鐘重新設(shè)計(jì)圖2所示的電路,。地址線在控制D觸發(fā)器的使能輸入,許多PLD設(shè)計(jì)軟件,,如Max+PlusⅡ軟件都提供這種帶使能端的D觸發(fā)器,。當(dāng)ENA為高電平時(shí),,D輸入端的值被鐘控到觸發(fā)器中:當(dāng)ENA為低電平時(shí),維持現(xiàn)在的狀態(tài),。

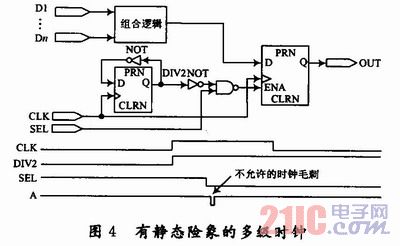

3 多級(jí)邏輯時(shí)鐘

當(dāng)產(chǎn)生門控時(shí)鐘的組合邏輯超過一級(jí)(即超過單個(gè)的“與”門或“或”門)時(shí),,驗(yàn)證設(shè)計(jì)項(xiàng)目的可靠性變得很困難。即使樣機(jī)或仿真結(jié)果沒有顯示出靜態(tài)險(xiǎn)象,,但實(shí)際上仍然可能存在著危險(xiǎn),。通常,不應(yīng)該用多級(jí)組合邏輯去鐘控PLD設(shè)計(jì)中的觸發(fā)器,。

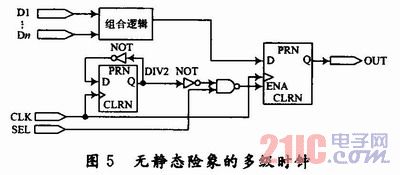

圖4給出一個(gè)含有險(xiǎn)象的多級(jí)時(shí)鐘的例子,。時(shí)鐘是由SEL引腳控制的多路選擇器輸出的。多路選擇器的輸入是時(shí)鐘(CLK)和該時(shí)鐘的2分頻(DIV2),。多級(jí)邏輯的險(xiǎn)象可以去除,。例如,可以插入“冗余邏輯”到設(shè)計(jì)項(xiàng)目中,。然而,,PLD/FPGA編譯器在邏輯綜合時(shí)會(huì)去掉這些冗余邏輯,使得驗(yàn)證險(xiǎn)象是否真正被去除變得困難了,。為此,,必須應(yīng)尋求其他方法來實(shí)現(xiàn)電路的功能。

圖5給出圖4電路的一種單級(jí)時(shí)鐘的替代方案,。圖中SEL引腳和DIV2信號(hào)用于使能D觸發(fā)器的使能輸入端,,而不是用于該觸發(fā)器的時(shí)鐘引腳。采用這個(gè)電路并不需要附加PLD的邏輯單元,,工作卻可靠多了,。

4 行波時(shí)鐘

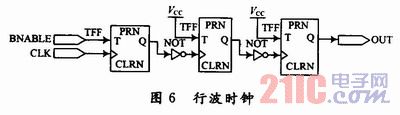

另一種流行的時(shí)鐘電路是采用行波時(shí)鐘,即一個(gè)觸發(fā)器的輸出用作另一個(gè)觸發(fā)器的時(shí)鐘輸入,。如果仔細(xì)地設(shè)計(jì),行波時(shí)鐘可以像鐘一樣地可靠工作,。然而,,行波時(shí)鐘使得與電路有關(guān)的定時(shí)計(jì)算變得很復(fù)雜。行波時(shí)鐘在行波鏈上各觸發(fā)器的時(shí)鐘之間產(chǎn)生較大的時(shí)間偏移,,并且會(huì)超出最壞情況下的建立時(shí)間,、保持時(shí)間和電路中時(shí)鐘到輸出的延時(shí),使系統(tǒng)的實(shí)際速度下降,,如圖6所示,。

5 多時(shí)鐘系統(tǒng)

許多系統(tǒng)要求在同一個(gè)PLD內(nèi)采用多時(shí)鐘。最常見的例子是兩個(gè)異步微處理器之間的接口,,或微處理器和異步通信通道的接口,。由于兩個(gè)時(shí)鐘信號(hào)之間要求一定的建立和保持時(shí)間,,所以,上述應(yīng)用引進(jìn)了附加的定時(shí)約束條件,。它們也會(huì)要求將某些異步信號(hào)同步化,。

圖7給出一個(gè)多時(shí)鐘系統(tǒng)的實(shí)例。CLK_A用以鐘控REG_A,,CLK_B用于鐘控REG_B,,由于REG_A驅(qū)動(dòng)著進(jìn)入REG_B的組合邏輯,故CLK_A的上升沿相對(duì)于CLK_B的上升沿有建立時(shí)間和保持時(shí)間的要求,。由于REG_B不驅(qū)動(dòng)饋到REG_A的邏輯,,CLK_B的上升沿相對(duì)于CLK_A沒有建立時(shí)間的要求。此外,,由于時(shí)鐘的下降沿不影響觸發(fā)器的狀態(tài),,所以CLK_A和CLK_B的下降沿之間沒有時(shí)間上的要求。電路中有兩個(gè)獨(dú)立的時(shí)鐘,,可是,,在它們之間的建立時(shí)間和保持時(shí)間的要求是不能保證的。在這種情況下,,必須將電路同步化,。圖8給出REG_A的值(如何在使用前)同CLK_B同步化。新的觸發(fā)器REG_C由GLK_B觸控,,保證REG_G的輸出符合REG_B的建立時(shí)間,。然而,這個(gè)方法使輸出延時(shí)了一個(gè)時(shí)鐘周期,。

在許多應(yīng)用中只將異步信號(hào)同步化還是不夠的,,當(dāng)系統(tǒng)中有兩個(gè)或兩個(gè)以上非同源時(shí)鐘的時(shí)候,數(shù)據(jù)的建立和保持時(shí)間很難得到保證,,將面臨復(fù)雜的時(shí)間問題,。最好的方法是將所有非同源時(shí)鐘同步化。使用PLD內(nèi)部的鎖項(xiàng)環(huán)(PLL或DLL)是一個(gè)效果很好的方法,,但不是所有PLD都帶有PLL,,DLL,而且?guī)в蠵LL功能的芯片大多價(jià)格昂貴,,所以除非有特殊要求,,一般場合可以不使用帶PLL的PLD。這時(shí)需要使用帶使能端的

D觸發(fā)器,,并引入一個(gè)高頻時(shí)鐘,。

6 結(jié)語

穩(wěn)定可靠的時(shí)鐘是系統(tǒng)穩(wěn)定可靠的重要條件,所以不能將任何可能含有毛刺的輸出作為時(shí)鐘信號(hào),并且盡可能只使用一個(gè)全局時(shí)鐘,,對(duì)多時(shí)鐘系統(tǒng)要注意同步異步信號(hào)和非同源時(shí)鐘,。