?

??? 器件供應(yīng)商降低制造成本的一個(gè)方法是中止老產(chǎn)品,,這樣做就導(dǎo)致微處理器過時(shí),。那些微處理器核的多個(gè)版本與集成外圍器件的混合使情況更加復(fù)雜,對(duì)于特殊處理器的結(jié)構(gòu)引起器件過剩,。通過把外圍設(shè)備整合至有微處理器的裸片,,供應(yīng)商可以把微處理器用于大批量的專門應(yīng)用,。(文中提到的“微處理器”指整個(gè)元件,包括處理器核與集成的外圍設(shè)備),。由于應(yīng)用和標(biāo)準(zhǔn)隨著時(shí)間的推移而發(fā)展,,微處理器設(shè)計(jì)的狹窄市場(chǎng)使得微處理器更加容易過時(shí)。本文闡述設(shè)計(jì)者面對(duì)微處理器(微控制器)過時(shí)的情況,,采用FPGA的可選方案,。

?

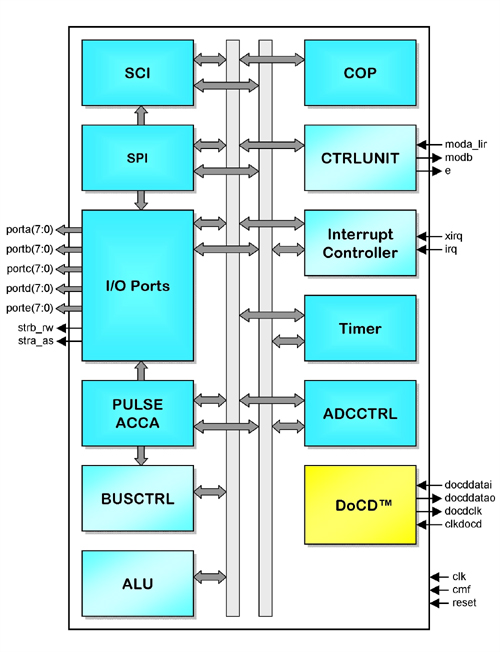

??? 考慮這個(gè)選擇之前,首先考慮FPGA作為應(yīng)對(duì)微處理器過時(shí)的挑戰(zhàn)是很有用的,。例如LatticeXP2 FPGA,可以實(shí)現(xiàn)68HC11兼容的CPU核,完全可綜合的代碼只要2600 個(gè)slice,。如圖1所示的68HC11兼容的微處理器,,把所有外設(shè)集成到這個(gè)器件將增加幾百個(gè)slice。此外,,容易適配至當(dāng)今的FPGA,,這個(gè)實(shí)現(xiàn)方案可以比原來的8-12 MHz 運(yùn)行快5倍。

?圖1? 實(shí)現(xiàn)D68HC11微處理器?

技術(shù)曲線

?

??? FPGA使設(shè)計(jì)者利用技術(shù)曲線,,以防止微處理器的過時(shí),。外圍設(shè)備,或者把它們組合在一起或許也會(huì)過時(shí),。除了處理過時(shí)的微處理器,,針對(duì)把周圍的功能整合到FPGA,F(xiàn)PGA技術(shù)曲線提供了選擇,。因此降低了整個(gè)系統(tǒng)的成本,,并解除了對(duì)其它元件不能繼續(xù)供應(yīng)的擔(dān)憂?;赟oC的微處理器和FPGA遵從的技術(shù)曲線如圖2所示,,用可綜合的RTL,F(xiàn)PGA設(shè)計(jì)者免于受到將來器件過時(shí)的影響,,在大批量ASIC的NRE里未提及,。

?????????????????????????? ?????????

?????????

圖2?? 技術(shù)曲線增加了整合空間?

?

??? 圖2中的技術(shù)曲線展示了微處理器和微控制器的相關(guān)等效邏輯復(fù)雜性與FPGA里軟實(shí)現(xiàn)的比較。原來的微控制器過時(shí)的時(shí)候,,可用的FPGA邏輯密度遠(yuǎn)多于實(shí)現(xiàn)微處理器和外設(shè)所需的邏輯,。這個(gè)額外的邏輯稱為外設(shè)整合空間,將隨著FPGA密度繼續(xù)增加而增長(zhǎng),。圖1中的D86HC11包括了DoCD塊,,提供了實(shí)時(shí),非插入系統(tǒng)調(diào)試,,以及沒有整合到原來微控制器的功能,。

?

??? FPGA提供了對(duì)設(shè)計(jì)的折衷方法,因此實(shí)現(xiàn)解決方案時(shí)設(shè)計(jì)者有多種選擇,。各種選擇方案如下:

?

選擇方案1:完成再設(shè)計(jì)(將來驗(yàn)證設(shè)計(jì))

?

??? 在此方案中,,器件供應(yīng)商也許提供替代元件,或許不是相同的指令集結(jié)構(gòu)(ISA),。這個(gè)選擇需要完成硬件和軟件的再設(shè)計(jì),,使用另外的基于元件的微處理器解決方案,或者基于FPGA的解決方案,。如果選擇這個(gè)方案,,將來驗(yàn)證這個(gè)設(shè)計(jì)是理想的,,采用開放源代碼軟處理器Harvard結(jié)構(gòu)的32位LatticeMico32。不像GNU公用許可證(GPL),,軟件團(tuán)體是相同的,,用于LatticeMico32的創(chuàng)新開放源代碼許可證是用硬件實(shí)現(xiàn)的。它可以移植到任何FPGA或者免費(fèi)的ASIC,。

選擇方案2:相同的ISA,,較高的整合

??? 原來微處理器元件的軟實(shí)現(xiàn)(μP核和集成外設(shè))編程至FPGA。軟處理器實(shí)現(xiàn)和外圍設(shè)備比原來的元件運(yùn)行速度高,。采用這個(gè)選擇,,外設(shè)或者時(shí)序環(huán)有任何變化,軟件只要做較小的改動(dòng),。這個(gè)選擇的優(yōu)點(diǎn)是軟件變化最小,,降低了電路板的成本,因?yàn)殡娐钒宓钠渌δ芏颊现罠PGA,。

?

選擇方案3:二進(jìn)制兼容,,較高的整合

?

??? 原來微處理器元件的軟實(shí)現(xiàn)(μP核和集成外設(shè))及精確的時(shí)序編程至FPGA。目標(biāo)是用原始的二進(jìn)制代碼而不需要修改,。通過整合其它電路板的功能至FPGA,,這個(gè)選擇降低了電路板的成本。

?

選擇方案4:二進(jìn)制兼容,,插座兼容(典型方案)

?

??? 這個(gè)選擇使用中間層電路板實(shí)現(xiàn)FPGA,,針對(duì)原來的微控制器,最小化相關(guān)的邏輯有準(zhǔn)確的引腳對(duì)引腳的替換,。除了中間層電路板之外,,這個(gè)方法不用改變軟件和硬件。

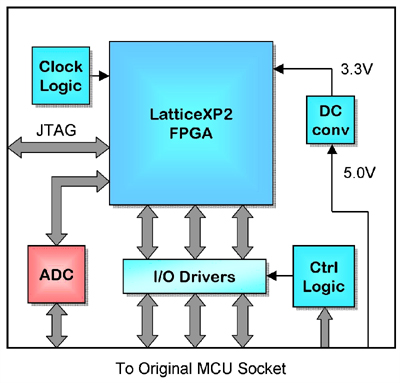

例如,,供應(yīng)商停止68HC11 MCU生產(chǎn),。對(duì)這個(gè)問題評(píng)估可能的方法,客戶也許會(huì)規(guī)定替代的部件必須與原來的功能和時(shí)序一樣,,運(yùn)行相同的二進(jìn)制程序而無需修改,。客戶決定將DCD的 D68HC11 IP核用在LatticeXP2 FPGA中,。LatticeXP2的片上Flash能用于較少部件的簡(jiǎn)單設(shè)計(jì),,見圖3,因?yàn)榉且资atticeXP2不需要外部的Flash存儲(chǔ)器,,或者其它的電路下載FPGA配置,。

圖3? 針對(duì)選擇方案4的實(shí)現(xiàn)方案?

?

??? 最初客戶考慮用完全不同的處理器代替68HC11,,但是這個(gè)方法要求取代應(yīng)用軟件,。這是一個(gè)很困難的任務(wù),因?yàn)檐浖c68HC11指令和內(nèi)部的外設(shè)緊密相關(guān),。因此轉(zhuǎn)到新的處理器需要為軟件的再設(shè)計(jì)付出大量的時(shí)間和精力,。結(jié)果大多數(shù)解決方案是用FPGA取代68HC11,。這個(gè)選擇將專注FPGA里D68HC11 IP核的確認(rèn),,避免改變系統(tǒng)的任何部分(軟件應(yīng)用,,外部電路板元件),,系統(tǒng)已完好地運(yùn)行了15年多。

?

??? 最重要的要求是能夠得到與原來的微處理器完全兼容的軟件,。必須是運(yùn)行在D68HC11上相同的二進(jìn)制代碼,,對(duì)二進(jìn)制代碼的任何改變都是不可接受的,。在這樣的情況下,,另外的限制是保持指令周期的精確性,。這是很關(guān)鍵的,,因?yàn)檐浖?huì)使用指令循環(huán)構(gòu)成的時(shí)序延時(shí),。此外,,有些功能或外圍接口也許會(huì)依賴精確根據(jù)指令和時(shí)鐘周期確定的執(zhí)行時(shí)間,。

?

??? 使用這個(gè)方法時(shí),,很難達(dá)到外設(shè)兼容。然而在此情況,,所有的數(shù)字部分都容易實(shí)現(xiàn),,并具有相同的功能和時(shí)序,。大多數(shù)現(xiàn)成的IP核都是設(shè)計(jì)好的,,并在DCD核庫(kù)中驗(yàn)證過,。

?

??? 通常的問題是替代微控制器的模擬元件,例如模數(shù)轉(zhuǎn)換器(ADC),,上電/電源故障復(fù)位產(chǎn)生和時(shí)鐘振蕩器,。數(shù)字可編程器件FPGA可以實(shí)現(xiàn)與這些功能相關(guān)的任何數(shù)字接口邏輯,,但不是模擬電路,。

?

??? 用FPGA取代先前整合的ADC數(shù)字功能是可能的。采用外部ADC轉(zhuǎn)換器和設(shè)計(jì)D68HC11接口是必須的。因?yàn)槟壳皼]有ADC具有和原來的元件有相同的精度,,要選擇性能好的,。要求是有寄存器功能,與原來的ADC接口相同,,包括ADC和CPU之間控制和狀態(tài)信號(hào)的翻譯,。轉(zhuǎn)換時(shí)序必須是相同的。這是ADC接口的主要功能,,D68HC11的附加模塊在FPGA中實(shí)現(xiàn),。

?

??? 因此,用FPGA,、ADC、時(shí)鐘發(fā)生器和PLCC插座取代了老的器件,,構(gòu)成了小的印刷電路板并直接與客戶的系統(tǒng)相連,。對(duì)原來的電路板無需開發(fā)軟件或改變。

?

??? 用這個(gè)FPGA實(shí)現(xiàn)的大多數(shù)IP核源于DCD庫(kù),,且已完全經(jīng)過驗(yàn)證,。任何新的外設(shè)都要設(shè)計(jì)成與68HC11的要求相匹配。對(duì)照舊的外設(shè)時(shí)序和功能,,要仔細(xì)地驗(yàn)證新的外設(shè),。對(duì)驗(yàn)證來說FPGA是理想的,,可以在FPGA中立即驗(yàn)證改變的HDL,。

?

結(jié)論?

?

??? 本文中我們強(qiáng)調(diào)了微處理器的過時(shí)問題,。提出了基于FPGA的選擇方案,向涉及到過時(shí)微處理器問題的設(shè)計(jì)者提出了基于FPGA的選擇,提供了將來驗(yàn)證需要微處理器的新設(shè)計(jì)方法,。說明了FPGA如何針對(duì)過時(shí)問題的解決方案,,以及整合功能、降低電路板成本的一些選擇,,并提高了調(diào)試設(shè)計(jì)的可見性,。

?

?