摘要:出租車計(jì)費(fèi)系統(tǒng)大多利用單片機(jī)進(jìn)行控制,較易被改裝,且故障率較高。針對(duì)這一問(wèn)題,設(shè)計(jì)了一種基于FPGA的出租車計(jì)費(fèi)系統(tǒng),可模擬汽車行駛、暫停等待,停止等過(guò)程,并可同時(shí)顯示金額、乘車總路程。設(shè)計(jì)采用層次化設(shè)計(jì)方法,用VHDL語(yǔ)言進(jìn)行編程,開發(fā)軟件為MAX+plusⅡ。經(jīng)測(cè)試,波形與仿真結(jié)果都滿足設(shè)計(jì)要求。

關(guān)鍵詞:出租車計(jì)費(fèi)系統(tǒng);VHDL語(yǔ)言;MAX+PLUSⅡ;FPGA

隨著城市化水平的提高和人民生活水平的改善,出租車的服務(wù)顯得越來(lái)越重要。因此出租車計(jì)費(fèi)器也就應(yīng)運(yùn)而生了。出租車計(jì)費(fèi)器是一種專用的計(jì)量?jī)x器,它安裝在出租車上,指示出載客路程數(shù),以及乘客應(yīng)付費(fèi)用的總數(shù)。

出租車計(jì)價(jià)系統(tǒng)較多的是利用單片機(jī)進(jìn)行控制,但較易被私自改裝,且故障率相對(duì)較高,且不易升級(jí);而FPGA具有高密度、可編程及有強(qiáng)大的軟件支持等特點(diǎn),所以設(shè)計(jì)的產(chǎn)品具有功能強(qiáng)、可靠性高、易于修改等特點(diǎn)。

本文正是基于FPGA,設(shè)計(jì)了一種出租車的計(jì)費(fèi)系統(tǒng),它可以直觀地顯示出租車行駛的里程和乘客應(yīng)付的費(fèi)用。

1 系統(tǒng)功能設(shè)計(jì)

所設(shè)計(jì)的計(jì)價(jià)器的計(jì)費(fèi)標(biāo)準(zhǔn)為:車在行駛3 km以內(nèi),只收起步價(jià)9.0元;車行駛超過(guò)3 km后,按每公里2元計(jì)費(fèi)。行駛路程達(dá)到或超過(guò)9 km后,車費(fèi)按每公里3.0元開始計(jì)費(fèi)。車遇紅燈或中途暫停時(shí),每3分鐘計(jì)0.5元。若停止(rst)則車費(fèi)清零,等待下一次計(jì)費(fèi)的開始。要求能夠顯示里程數(shù)和乘客應(yīng)付的費(fèi)用,其中里程數(shù)精確到0.01 km,乘客應(yīng)付的費(fèi)用精確到0.1元,顯示范圍為:里程為0~99.99公里,費(fèi)用為0~999.9元。

2 系統(tǒng)設(shè)計(jì)方案

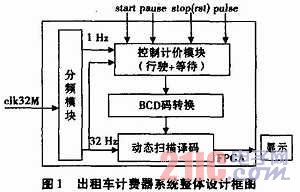

基于FPGA的出租車計(jì)費(fèi)系統(tǒng)的組成如圖1所示。由外部輸入、FPGA控制部分以及數(shù)碼顯示三部分組成。其中FPGA部分又由分頻模塊、計(jì)價(jià)模塊、BCD轉(zhuǎn)換模塊以及動(dòng)態(tài)譯碼掃描模塊組成;外部輸入包括啟動(dòng)按鍵(start)、暫停按鍵(pause)、停止按鍵(stop即rst)以及兩個(gè)脈沖信號(hào)(分別是每20 m一個(gè)脈沖的路程脈沖信號(hào)pulse和32 MHz的工作脈沖信號(hào)clk32M)。顯示模塊用8個(gè)LED數(shù)碼管分別顯示行駛里程和車費(fèi),行駛里程顯示2位整數(shù)和2位小數(shù),車費(fèi)顯示3位整數(shù)和1位小數(shù)。

3 各模塊設(shè)計(jì)

設(shè)計(jì)FPGA控制部分,包括控制計(jì)價(jià)模塊,BCD轉(zhuǎn)換模塊,動(dòng)態(tài)掃描譯碼模塊以及分頻模塊。采用混合設(shè)計(jì)的方法,各子部分用VHDL編程,頂層部分用原理圖進(jìn)行設(shè)計(jì)。

3.1 控制計(jì)價(jià)模塊(jijia)

控制計(jì)價(jià)模塊由里程計(jì)費(fèi)模塊、等待計(jì)費(fèi)模塊、總價(jià)模塊組成。

里程計(jì)費(fèi)模塊,主要對(duì)傳感器公里脈沖信號(hào)pulse計(jì)數(shù)(20m一個(gè)脈沖),計(jì)算出租車本次交易行駛的路程以及里程費(fèi)用。每數(shù)到50個(gè)pulse為1 km,總路程由lucheng端輸出。在3 km內(nèi)時(shí),里程車費(fèi)cf1為9元不變,當(dāng)超過(guò)3 km時(shí),p=1,開始里程費(fèi)用計(jì)數(shù),當(dāng)計(jì)費(fèi)停止,即start端口置“0”或出租車停止行駛,即rst端口置“0”時(shí),相關(guān)數(shù)據(jù)復(fù)位,清零。

等待計(jì)費(fèi)模塊,在3 km之后(p=1),每當(dāng)pause=1時(shí),則開始計(jì)時(shí),當(dāng)秒脈沖數(shù)到180個(gè)時(shí)(即3分鐘),此時(shí)等待車費(fèi)cf2加5,表示車費(fèi)加0.5元。

總價(jià)模塊是將里程計(jì)費(fèi)和等待計(jì)費(fèi)相加,計(jì)算出總費(fèi)用,從chefei端輸出。

3.2 BCD轉(zhuǎn)換模塊(zhuanhuan)

該模塊將計(jì)費(fèi)模塊的車費(fèi)和路程轉(zhuǎn)換成4位十進(jìn)制數(shù),便于數(shù)碼管顯示。輸入口acf,bcf分別為總路程數(shù)的輸入口和總費(fèi)用的輸入口,兩者都是二進(jìn)制碼進(jìn)行十進(jìn)制編碼計(jì)數(shù),通過(guò)該編碼器生成BCD碼,輸出口分別以BCD碼表示個(gè),十,百,千位的數(shù)據(jù)。Aclk是工作脈沖,即32MHz。

3.3 動(dòng)態(tài)掃描模塊(dtxianshi)

該模塊由動(dòng)態(tài)掃描模塊以及譯碼模塊組成。動(dòng)態(tài)掃描模塊,該模塊利用視覺(jué)暫留效應(yīng),采用動(dòng)態(tài)掃描電路,將8進(jìn)制轉(zhuǎn)換后的路程數(shù)和車費(fèi)的4位十進(jìn)制數(shù)顯示在數(shù)碼管上,節(jié)約了硬件資源和能源。該模塊經(jīng)過(guò)8進(jìn)制掃描模塊將路程和車費(fèi)輪流顯示出來(lái)。端口d是選通地址碼的輸入端口,A1,A2,A3,A4,B1,B2,B3,B4分別是個(gè),十,百,千位的數(shù)值輸入端口。根據(jù)輸入的地址碼,模塊每次只有一位數(shù)字向后傳輸?shù)捷敵隹趒,同時(shí)輸出小數(shù)點(diǎn)的顯示控制信號(hào)(dp),使路程顯示為00.00公里,費(fèi)用顯示為000.0元。

譯碼模塊,該模塊把0-9的BCD碼譯成數(shù)碼管顯示碼,輸入端口q輸入掃描模塊選出要顯示的BCD碼,譯成數(shù)碼管的顯示碼由g[6..0]輸出。本設(shè)計(jì)中數(shù)碼管是共陰數(shù)碼管。

3.4 分頻模塊(fenp)

本設(shè)計(jì)中輸入的系統(tǒng)時(shí)鐘為32 MHz,進(jìn)行分頻,再對(duì)數(shù)碼管的地址進(jìn)行掃描。輸入端口rse為出租車停運(yùn)信號(hào)輸入端口,當(dāng)出租車停止時(shí),該模塊停止工作,清零。當(dāng)出租車行駛時(shí)對(duì)輸入的32 MHz脈沖信號(hào)進(jìn)行分頻,分別從輸出端口cp1得到秒脈沖,cp32得到32 Hz工作脈沖。

3.5 整體電路

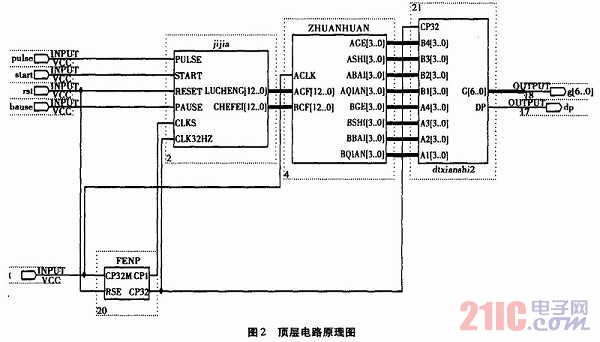

將各個(gè)模塊按照輸入輸出關(guān)系連接,頂層電路原理圖如圖2所示。g[6…0]為七段顯示碼輸出,通過(guò)動(dòng)態(tài)掃描依次控制8個(gè)數(shù)碼管的顯示,dp為小數(shù)點(diǎn)位。

4 系統(tǒng)仿真驗(yàn)證

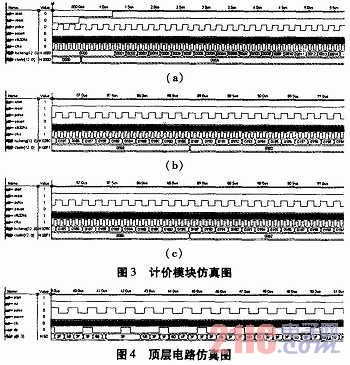

用MAX+plusⅡ軟件對(duì)各個(gè)子模塊及頂層原理圖進(jìn)行了時(shí)序仿真,仿真波形如圖3所示。

控制計(jì)價(jià)模塊仿真圖如圖3所示。由圖3(a)可得,當(dāng)reset=1,start=1,且pause=0時(shí),表示出租車處于行駛狀態(tài),此時(shí)路程開始遞增,當(dāng)不超過(guò)3 km時(shí),車費(fèi)為5A即90,起步價(jià)9.0元。由圖3(b)可得,當(dāng)超過(guò)3 km后,車費(fèi)每行駛1 km加20(即2元)。由圖3(c)可得,當(dāng)reset= 1,start=1,且pause=1時(shí),出租車處于等待狀態(tài),此時(shí)路程不再遞增,而時(shí)間遞增,當(dāng)時(shí)間達(dá)到3分鐘時(shí),車費(fèi)加5(即0.5元)。

頂層電路的仿真圖如圖4所示。從圖中可以看出,隨著輸入的變化,從g[6…0]輸出了共陰的數(shù)碼管顯示編碼,dp也在對(duì)應(yīng)的數(shù)碼管處,輸出高電平點(diǎn)亮小數(shù)點(diǎn)。

綜上分析,本設(shè)計(jì)的軟件仿真結(jié)果正確,與設(shè)計(jì)要求相符。