摘要:基于新一代圖像壓縮國際標準JPEG 2000,介紹一種快速、有效的多層5/3小渡變換的VLSI設計結(jié)構(gòu),該方法使用兩組一維變換實現(xiàn),用移位-相加代替乘法操作,整體設計采用了流水線設計。利用雙端口RAM和地址生成模塊的調(diào)度完成小波變換的分裂、邊界延拓工作,不需另外增加模塊。二維離散小波變換濾波器結(jié)構(gòu)的設計采用Verilog HDL進行RTL級描述,已經(jīng)通過了FPGA驗證,并可作為單獨的IP棱應用于圖像編解碼芯片中。

關鍵詞:JPEG 2000標準;離散小波變換;FPGA;RAM

0 引言

隨著多媒體應用領域的快速發(fā)展,新一代靜止圖像壓縮標準JPEG 2000己在2000年11月完成了標準的制定。與原有的JPEG標準相比,JPEG 2000具有許多優(yōu)勢。例如更高的壓縮性能,支持單分量或者多分量的有損和無損壓縮,可以提供質(zhì)量和分辨率漸進傳輸,以及感興趣區(qū)域編碼等。典型的JPEG 2000編碼中的傳統(tǒng)的離散小波變換由卷積完成,因此在實現(xiàn)中需要巨大的計算和存儲量。I.Daubechies和W.Sweldens等人提出的提升算法解決了這些問題,該算法采用采用移位-相加操作代替卷積操作,大大降低了DWT運算硬件實現(xiàn)的難度,因此JPEG 2000采用基于提升的DWT作為圖像壓縮的第一步。JPEG 2000推薦5/3及9/7小波分別用于無損和有損壓縮,本文針對5/3濾波器,提出了一種高效高速的二維三層小波變換的硬件平臺,整體結(jié)構(gòu)采用流水操作。

1 離散小波提升算法

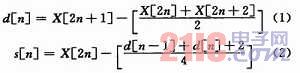

離散小波提升算法主要有三個步驟:分裂(Split)、預測(Predict)和更新(Update)。分裂是把輸入信號x(n)分成奇偶兩個子信號集,即由其采樣后的偶序列子信號組成xe=x(2n),奇序列子信號組成x0=x(2n+1)。預測是偶序列信號乘上一個預測參數(shù)P,來預測奇信號,原來的奇序列信號與預測值的差即為高頻系數(shù)d(n)。更新是高頻系數(shù)乘以更新系數(shù)Q與偶序列信號的和,獲得低頻系數(shù)s(n)。

5/3雙正交小波對應的提升方法如圖1所示,用于JPEG 2000中的無損壓縮過程,硬件實現(xiàn)可分為兩步,如式(1),式(2)所示:

2 5/3小波內(nèi)嵌延拓提升算法

由式(1)和式(2)可以看出,在圖像邊界處進行小波變換時需要進行延拓處理,否則無法正確進行小波變換,對原始圖像邊界數(shù)據(jù)的處理通常使用對稱周期延拓方式,5/3小波變換的延拓需要在序列前延拓兩個數(shù)據(jù),在序列后延拓一個數(shù)據(jù),圖2為5/3小波變換時8點數(shù)據(jù)序列周期對稱延拓示意圖。

本文是通過雙端口RAM的讀/寫實現(xiàn)分裂過程,在小波變換過程中通過對讀地址的操作實現(xiàn)對稱周期性數(shù)據(jù)延拓:用對計數(shù)器的計算操作實現(xiàn)邊界數(shù)據(jù)延拓和生成讀取地址與寫入地址,從原圖像中讀取,經(jīng)變換后寫入相應的地址,以8×8圖像為例,行方向上延拓后的讀取地址順序應該是2,1,0,1,2,3,4,5,6,7,6,10,9,8,9,10,…;列方向上延拓后讀取地址順序是16,8,0,8,16,24,32,40,48,56,48,17,9,…。

3 硬件設計

3.1 總體結(jié)構(gòu)框圖

二維DWT實質(zhì)上相當于先對圖像數(shù)據(jù)做一維行方向小波變換,再對變換后的結(jié)果進行一維列方向上的小波變換,總體結(jié)構(gòu)如圖3所示。輸入的圖像數(shù)據(jù)是在原始RAM上存儲,通過行地址模塊生成的行變換地址讀出圖像數(shù)據(jù),通過一維行向量的小波變換模塊處理,將中間數(shù)據(jù)放入中間RAM中,再通過列地址模塊生成的列變換地址讀出中間圖像數(shù)據(jù),通過一維列向量的小波變換模塊處理,最后將輸出的小波分解系數(shù)寫入外部存儲器,然后由控制單元判斷是否進行下一級小波分解,如果需要做下一層分解的話,將在上一層小波變換的結(jié)果中取出LL低頻子帶進行下一個循環(huán),每對圖像進行一次二維小波變換,產(chǎn)生的結(jié)果同樣存儲在外部存儲器IM—RAM上,即下一級的小波變換結(jié)果覆蓋在上一級的LL子帶上。

3.2 地址生成模塊的設計

對于做三層的離散小波變換,每層對RAM的(行/列)讀/寫地址都不相同,所以在地址生成模塊中分別做了三層各自的地址模塊,每個單層地址模塊產(chǎn)生2路讀地址信號、2路寫地址信號和1路寫地址使能信號。首先產(chǎn)生行變換的讀/寫地址,在行變換完成之后產(chǎn)生列變換的讀/寫地址,在列變換完成之后,給出一個EndOfBlock信號返回給圖4中的Control模塊。由Control模塊控制分層地址模塊的使能以及Select模塊選擇有效地址信號輸出,并且通過對讀地址計算算法的調(diào)度,實現(xiàn)分裂和邊界延拓功能,不需要另外設計單獨的處理模塊,地址生成模塊的總體框圖如圖4所示。

4.功能仿真及FPGA測試驗證

該設計采用了流水線技術即通過插入寄存器,使得一組輸入數(shù)據(jù)的計算分布在同一個時鐘周期中,從而提高資源利用率,增加電路的數(shù)據(jù)處理量,提高了性能,在此用Verilog HDL描述實現(xiàn)。

4.1 功能仿真

在ModelSim的測試模塊中設置時鐘為100 MHz,圖5為部分仿真結(jié)果,輸入數(shù)據(jù)在經(jīng)過3個時鐘周期后計算出LH分量輸出。由此可見,一維小波變換模塊的設計符合JPEG 2000標準規(guī)定,結(jié)果正確。

二維小波變換結(jié)果就是,在行變換結(jié)束之后對于行方向上面的LH分量再做列方向上的小波變換,得到LL,HL,LH,HH分量,對于多層小波變換就是在前一層變換的結(jié)果上對LL子帶再進行二維DWT變換,多層小波變換的示意圖如圖6所示。

4.2 FPGA測試驗證

該設計的FPGA驗證采用Altera的DE2開發(fā)板平臺,開發(fā)板采用CycloneⅡEP2C35作為主FPGA芯片,具有豐富的I/O接口與顯示存儲設備,可以滿足該設計的驗證工作。

本次FPGA的驗證中使用Altera的SignalTapⅡ嵌入式邏輯分析儀。SignalTapⅡ嵌入式邏輯分析儀集成到QuartusⅡ設計軟件中,能夠捕獲和顯示設計中實時信號的狀態(tài),這樣開發(fā)者就可以在整個設計過程中以系統(tǒng)級速度觀察硬件和軟件的交互作用。它支持多達1 024個通道,采樣深度達128 Kb,每個分析儀均有10級觸發(fā)輸入/輸出,使用SignalTapⅡ無需額外的邏輯分析設備,只需將一根JTAG接口的下載電纜連接到要調(diào)試的FPGA器件即可。

下載驗證結(jié)果如圖7所示,整個系統(tǒng)時鐘可以達到156 MHz,速度很快,耗用資源相對較少,運算結(jié)果正確。

5 結(jié)語

本文提出了一種快速、有效的JPEG 2000 5/3小波變換的VLSI設計結(jié)構(gòu),該結(jié)構(gòu)將數(shù)據(jù)的奇偶分裂、邊界延拓嵌入到地址產(chǎn)生單元對雙端口RAM的操作中,不需要額外的計算單元,采用移位-相加操作代替卷積操作,通過Verilog編寫RTL級代碼并進行功能仿真,最后完成了在FPGA上的驗證,最高時鐘頻率達到156 MHz,整體性能優(yōu)越。