摘要:為了滿足高速圖像處理系統(tǒng)中需要高接口帶寬和大容量存儲的目的,采用了FPGA外接DDR2-SDRAM的設計方法,,提出一種基于VHDL語言的DDR2-SDRAM控制器的方案,,針對高速圖像處理系統(tǒng)中的具體情況,在Xilinx的ML506開發(fā)板上搭建了簡單的圖像處理系統(tǒng)平臺并進行了連續(xù)讀/寫標準VGA格式圖像數(shù)據(jù)的實驗,,在顯示端得到了清晰不掉幀的圖像結果,,具有結構簡單和高速存取圖像的特點。

關鍵詞:圖像處理,;DDR2-SDRAM控制器,;FPGA;緩存設計

0 引言

隨著電子信息技術的快速發(fā)展,,數(shù)字信號處理技術的應用越來越廣泛,,一般而言,同屬于數(shù)字信號處理的圖像系統(tǒng)處理帶寬遠高于控制及雷達信號處理系統(tǒng),??刂祁I域的信號采樣頻率一般低于1 MHz,雷達信號采樣頻率可以高達幾百MHz,但經(jīng)過硬件(ASIC)下變頻處理后,,也不高于1 MHz,。而圖像系統(tǒng)的處理帶寬一般在幾十兆至幾百兆字節(jié)每秒。所以高處理帶寬是圖像處理系統(tǒng)設計中必須考慮的問題,,高處理帶寬帶來的另外一個問題是緩存設計,,顯然系統(tǒng)中的緩存也應該具有較高帶寬。同時在圖像處理系統(tǒng)中,,特別是高幀頻圖像處理系統(tǒng)中是需要大容量緩存的,。控制及雷達領域一般需要的緩存為幾KB到幾十KB,,而圖像處理至少需要2幀圖像以實現(xiàn)乒乓緩存,,在圖像處理時間超過幀獲取時間時,需要3幀緩存以保證系統(tǒng)累積丟幀而非一旦超時就發(fā)生丟幀,。

在實際工作中,,高幀頻圖像的高處理帶寬和大存儲需求往往需要結合起來考慮,集中體現(xiàn)在外掛緩存的選擇與設計上,,較成熟的方案有SRAM,,SDRAM,DDR,,DDR2,,DDR3等,其中DDR3有最高接口帶寬和存儲深度,,考慮到具體情況,,選用僅次于DDR3的DDR2與FPGA實現(xiàn)接口,,可以滿足高速圖像處理系統(tǒng)對高接口帶寬和大容量存儲的要求,。

DDR2 SDRAM是由JEDEC(電子設備工程聯(lián)合委員會)進行開發(fā)的內存技術標準,工作電壓是1.8 V,,采用了在時鐘的上升/下降沿同時進行數(shù)據(jù)傳輸?shù)幕痉绞?。DDR2具有4 b預讀取速度,即DDR2內存每個時鐘能夠以4倍外部總線的速度讀/寫數(shù)據(jù),,同時DDR2的數(shù)據(jù)傳輸可以支持400 MHz,,533 MHz,667 MHz的傳輸率,。

文中在介紹DDR2的工作原理的基礎上,,給出了一個用VHDL語言設計的DDR2 SDRAM控制器的方法,并且提出了一種在高速圖像處理系統(tǒng)中DDR2 SDRAM的應用方案,,同時在Virtex-5系列的FPGA上得到了實現(xiàn),。

1 DDR2-SDRAM控制器的操作原理與設計

1.1 DDR2-SDRAM的操作原理

DDR2 SDRAM是運用DDR結構來達到高速操作。本文采用的DDR2-SDRAM是Micron的MT4H3264HY-53ED3。這款DDR2的存儲空間為256 MB,,由4片容量為512 Mb的內存芯片構成,。每個芯片的數(shù)據(jù)位寬為16 b,有4 bank,,13條行地址線,,10條列地址線,因此每個內存芯片容量為8 192×

1 024×4×16 b,,即512 Mb,。4片組成起來就構成了MT4H3264HY-53ED3的64 b位寬。

DDR2 SDRAM的操作主要通過以下控制信號給出:行地址選擇信號(![]() ),,列地址選擇信號(

),,列地址選擇信號(![]() ),,寫使能信號(

),,寫使能信號(![]() ),時針使能信號(CKE),,片選擇信號(

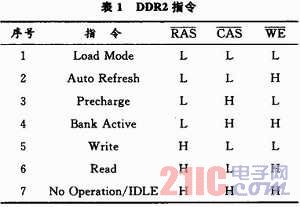

),時針使能信號(CKE),,片選擇信號(![]() ),。各種指令不同的組合方式完成不同的功能。表1為各種指令完成的組合方式,。

),。各種指令不同的組合方式完成不同的功能。表1為各種指令完成的組合方式,。

1.1.1 Load Mode指令

用來配置DDR2內存的模式寄存器,,包括一個主模式寄存器及3個擴展模式寄存器,它們被用來設定內存的工作方式,,包括突發(fā)長度的選擇,、突發(fā)的類型、CAS延遲,、CAS附加延遲,、DLL使能、ODT設置,、OCD設置以及DQS設置等,。

1.1.2 Precharge指令

預充電指令是用來重新激活bank中已經(jīng)打開的行。在預充電指令發(fā)出后,,當前bank必須等待一個特定的時間(tRP)后才可以再次激活,。

1.1.3 自動刷新指令

DDR2 SDRAM內存需要每7.8μs刷新一次。自動刷新不需要外部提供行地址信息,,DDR2 SDRAM內部有一個行地址生成器(也稱刷新計數(shù)器)用來自動的依次生成行地址,。由于刷新是針對一行中所有的存儲體進行,所以無需列地址,。在進入自動刷新模式前,,所有的bank必須都處于預充電狀態(tài),自動刷新指令在預充電指令后延遲tRP才能給出,。

1.1.4 Active指令

Active用來激活bank中的某一行,。在對DDR2內存進行讀/寫之前,都必須執(zhí)行該指令把bank中的某一行激活。激活命令到讀/寫命令之間的最小延遲由AL決定,,當AL為0時,,最小延遲由tRCD(RAS to CAS delay)決定。當AL不為0時,,激活命令到讀/寫命令之間的最小延遲就可以不受tRCD限制,,讀/寫命令可以提前,但其實最后數(shù)據(jù)的讀/寫并不提前,,這樣可以提高總線的利用率,。

需要注意的是,當要激活同一bank中不同的行時,,必須先對原來激活的行進行預充電,,才能激活新的行。同一bank中連續(xù)的active命令之間的間隔必須受tRC(RAS cycle time)的控制,。

1.1.5 Read指令

讀指令是用來對DDR2內存進行讀操作,,并對突發(fā)讀進行初始化。其中BA0和BA1給出bank地址,,A0~A1給出起始列地址,。突發(fā)讀結束后,激活的行在預充之前繼續(xù)保持有效,,直到該行被預充電,。從列選擇到數(shù)據(jù)輸出的延遲為CAS延遲(CL),整個讀延遲等于AL+CL,。讀操作時由內存給出一個與數(shù)據(jù)同步的數(shù)據(jù)濾波信號DQS,,它的邊沿與讀取的數(shù)據(jù)邊沿對齊。

1.1.6 Write指令

Write指令用來控制DDR2內存進行寫操作,,并給出burst寫的起始地址,。其中BA0和BA1給出bank地址,A0~A1給出起始列地址,。整個寫延遲為讀延遲減去一個時鐘周期,,即寫延遲等于AL+CL-1,。寫操作時,,控制器同樣給出一個與數(shù)據(jù)同步的數(shù)據(jù)濾波信號DQS,它的邊沿與寫數(shù)據(jù)的中間對齊,。

1.1.7 Idle指令

用來使DDR2內存處于空閑無操作狀態(tài),。

1.2 DDR2-SDRAM控制器的設計

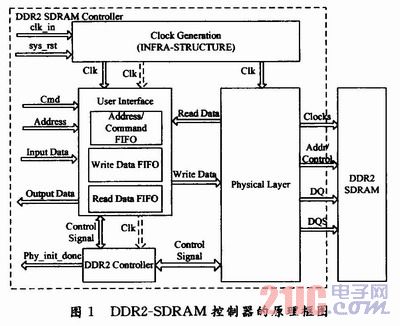

本文中的DDR2 SDRAM控制器是采用VHDL硬件描述語言設計的,主要由4部分組成:用戶界面模塊(User Interface),、基礎模塊(infrast-ructure),、物理層模塊(Physical layer)和存儲控制模塊(Controller)。DDR2-SDRAM控制器的設計原理框圖如圖1所示。

時鐘生成模塊用來產(chǎn)生控制器中所有模塊的時鐘信號,。外部用戶時鐘通過數(shù)字時鐘管理器(DCM)進行處理后,,輸出0度和90度的時鐘。同時該包括了一個延遲校準模塊,,是用來校準讀數(shù)據(jù)(DQ)對讀數(shù)據(jù)選通脈沖(DQS)的延遲,,以便DQS的邊沿能正確對齊DQ有效窗口的中間位置。

用戶接口模塊主要包括讀/寫數(shù)據(jù)和地址三類FIFO,,用來接收和存儲用戶的數(shù)據(jù),,命令和地址等信息,起到緩沖和同步數(shù)據(jù)的作用,??刂破髂K生成該模塊所需要的控制信號。

物理層模塊負責在控制信號的約束下完成用戶訪問地址與訪問指令的解釋與匹配,,產(chǎn)生DDR2 SDRAM所需的控制指令信號,,并保證指令與地址,數(shù)據(jù)的同步和信號的維持,。

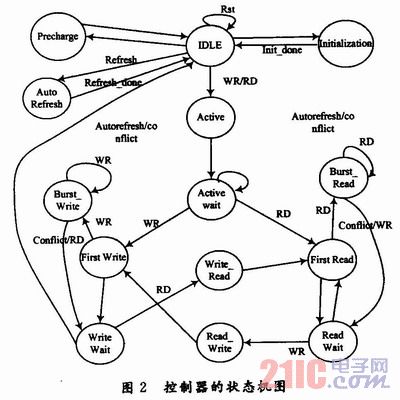

控制模塊主要實現(xiàn)的功能為:在系統(tǒng)上電過程及系統(tǒng)意外復位發(fā)生時,,與初始化模塊配合,對控制器和所控制的DDR2進行初始化設置,,復位延時保護等:在系統(tǒng)正常工作時,,進行系統(tǒng)讀/寫請求指令的接收、應答,,對系統(tǒng)訪問地址的采樣與同步,,完成所需的所有狀態(tài)轉換、任務調度,、總線仲裁,、時序同步,并為用戶接口模塊,、物理層模塊產(chǎn)生相應的控制信號,,為系統(tǒng)提供控制器狀態(tài)指示信號??刂破鞯臓顟B(tài)機結構如圖2所示,。

2 圖像處理系統(tǒng)中DDR2接口的設計

DDR2作為整個圖像處理系統(tǒng)的緩存,起著至關重要的作用,。它將外部輸入的圖像按幀存入DDR2中,,然后按幀將圖像數(shù)據(jù)送到外部繼續(xù)處理?;趩纹現(xiàn)PGA的控制邏輯所需要完成的功能可以簡單的概述如下:

(1)接收來自外部的圖像數(shù)據(jù),,并進行緩沖和數(shù)據(jù)重排,,產(chǎn)生符合DDR2-SDRAM控制器位寬的數(shù)據(jù)信號。

(2)產(chǎn)生對DDR2-SDRAM的讀/寫命令和地址,,并將它們寄存在FIFO中,,隨時供DDR2控制器提取,因此系統(tǒng)需要一個地址產(chǎn)生邏輯,。

(3)對DDR2-SDRAM進行直接控制,,將用戶產(chǎn)生的地址命令進行解析,產(chǎn)生讀/寫,、刷新等一系列操作,,對DDR2-SDRAM發(fā)出的各種命令要符合特定的時序要求。在上電的時候還必須完成對DDR2-SDRAM的初始化工作,。

(4)建立用戶與DDR2-SDRAM的數(shù)據(jù)通道,,在DDR2-SDRAM和用戶接口之間傳遞需要寫入或者讀出的數(shù)據(jù),并且調整對應讀/寫操作的DQS信號時序,,使其滿足DDR2-SDRAM的要求,。

(5)緩存從DDR2-SDRAM中讀出的數(shù)據(jù),由于直接讀出的速度非常高,,直接處理會對后端產(chǎn)生很大的壓力,,因此需要進行緩存之后才送到后續(xù)處理。

由上面的描述可以看出,,控制邏輯所要完成的功能是相當復雜的,,因此我們采用模塊化的設計方案。FPGA的控制邏輯功能劃分圖如圖3所示,。

2.1 時鐘生成模塊

時鐘生成模塊主要負責整個系統(tǒng)的所有時鐘,,包括DDR2控制器所需要的時鐘,外部圖像所需的時鐘,。全部由DCM來產(chǎn)生,。

2.2 數(shù)據(jù)接口模塊

數(shù)據(jù)接口模塊主要是負責不同數(shù)據(jù)之間格式的轉換,這個模塊主要是考慮到輸入端的數(shù)據(jù)的不同格式,,必須經(jīng)過格式轉換才能符合DDR2位寬的數(shù)據(jù),。

2.3 輸入/輸出緩存模塊

輸入/輸出緩存模塊是采用V5器件的DRAM來實現(xiàn)FIFO的,輸入緩存是由兩個DRAM來完成的,,DRAM配置為12×1 024,,12為數(shù)據(jù)寬度,1 024為存儲深度,,這個配置是根據(jù)具體圖像的位寬和每行的像素點來設定的,。在這里暫定的圖像源是標準的VGA圖像,,其大小為800×600,。數(shù)據(jù)源每寫入一行數(shù)據(jù)(800個數(shù)),,然后讀出一行數(shù)據(jù)??紤]到系統(tǒng)的穩(wěn)定性,,采用兩個FIFO交替的讀/寫數(shù)據(jù),也就是所謂的乒乓操作,,如圖4所示,,當一個FIFO在讀時,另一個FIFO就寫,,然后交替讀/寫,。在每一個FIFO讀完數(shù)據(jù)后,對其清零,。這樣就保證每一次寫入的數(shù)據(jù)不相互干擾,,保證了系統(tǒng)的穩(wěn)定性。其中的輸入/輸出選擇單元是通過判斷VGA圖像的行數(shù)來判斷寫和讀哪個FIFO的,。

除了緩存數(shù)據(jù),,F(xiàn)IFO在本模塊的另一個重要的作用就是時鐘域的轉換。外部的輸入數(shù)據(jù)和輸出數(shù)據(jù)的時鐘都是40 MHz,,而DDR2的讀/寫數(shù)據(jù)時鐘是100 MHz的,,這樣就存在著時鐘域的轉換問題,由于FIFO的讀/寫可以用不同的時鐘,。在輸入端,,就可以用40 MHz的時鐘把數(shù)據(jù)寫入FIFO,然后用100 MHz的時鐘從FIFO讀出數(shù)據(jù),。在輸出端可以用100 MHz的時鐘把從DDR2讀出的數(shù)據(jù)送入FIFO,,然后再用40 MHz的時鐘從FI-FO中讀出數(shù)據(jù),送到VGA顯示,。但是由于讀入與寫出的時鐘頻率不一樣,,很容易出現(xiàn)FIFO讀空和寫滿的問題。該問題的一般解決方法是利用FIFO的ALMOSTFULL和ALMOSTEMPTY來解決,。在這個系統(tǒng)中,,考慮到輸入的數(shù)據(jù)源和VGA顯示的時鐘頻率都是40 MHz,所以采用VGA數(shù)據(jù)有效信號來控制FIFO的寫,,行消隱信號來控制輸入FIFO的讀,,即每來一行數(shù)據(jù)才讀一行數(shù)據(jù),這樣就保證了輸入FIFO不會讀空,。而輸出FIFO的寫是通過DDR2內部的讀數(shù)據(jù)有效位來控制的,,因為DDR2內部的操作是寫1行,讀1行,,所以在寫入FIFO一行數(shù)據(jù)后,,要等到下一行到來后,,才會往輸出FIFO寫入數(shù)據(jù),所以也就解決了輸出FIFO寫滿的問題,。

2.4 DDR2-SDRAM控制模塊

DDR2-SDRAM的讀/寫控制是整個系統(tǒng)的關鍵,。由于要緩存圖像,所以就必須在DDR2里面開辟兩個大小相同的存儲單元,。這兩個存儲單元的大小是根據(jù)一幀圖像的大小來開辟的,,其大小為800×600個存儲單元。對DDR2的存儲操作為先向第一個存儲單元寫入第一行數(shù)據(jù),,讀出第二個存儲單元的第一行數(shù)據(jù),。當寫滿第一個存儲單片后,第二個存儲單元也被讀空,,這時候交換讀/寫地址,,讀一個存儲單元,寫第二個存儲單元,,依次輪換,。

由于圖像數(shù)據(jù)具有消隱時間,我們可以在場消隱的這段時間里來交換讀/寫地址,。讀/寫控制的具體操作如圖5所示,。

3 實驗結果

為了測試基于DDR2的圖像存儲性能,外部輸入圖像源選用標準VGA格式的圖像,,外部輸出端接到DVI接口,,DVI外接一般的CRT顯示器。D-VI接口的顯示芯片是CH7301,,通過配置這個芯片的寄存器選擇其VGA模式,。配置這個芯片寄存器的操作是通過I2C總線來達到的。這里選用Xi-linx公司的Virtex-5器件與Micron公司的DDR2 SDRAM顆粒MT4H3264HY-53ED3搭建了實驗的硬件平臺,。

在輸入端的VGA數(shù)據(jù)源產(chǎn)生的圖像為800×600,,幀頻為60/幀,底色為全黑,,5×5個像素點的白色正方形圖像,,其中白色正方形每幀以50個像素點距離移動,在CRT顯示端我們可以看見輸出端的圖像比輸入端的圖像延遲一幀,。實驗證明了設計是正確的,。實驗結果如圖6所示。

4 結語

通過具體的實測,,其DDR2的最高工作頻率為266MHz,,并且在200 MHz主頻下,其64位的數(shù)據(jù)傳輸速率達到了3.2 GB/s,,并且能正確的存儲圖像,,滿足了在高幀頻圖像處理系統(tǒng)中緩存的應用,。解決了基于FPGA的高速圖像處理系統(tǒng)中圖像緩存的難點,為基于FPGA的高幀頻圖像處理,,包括圖像旋轉,,圖像切割等的實現(xiàn)打下了良好的基礎,。