在工業(yè)生產(chǎn)和科研中,,通常要對信號進行長時間高速采樣,會產(chǎn)生大量采樣數(shù)據(jù),。在一些特殊環(huán)境下,,受體積和功耗的限制,不能添加過多存儲器,,需要引入數(shù)據(jù)壓縮技術來解決,。軟件壓縮算法的運算量較大,需要很高的CPU運算速度和數(shù)據(jù)緩存空間,,所以軟件壓縮一般應用在對時間要求不高的非實時壓縮場合,。而對運行速度有特殊要求的情況下,對數(shù)據(jù)的實時壓縮一般都要用硬件實現(xiàn),。有損壓縮之后數(shù)據(jù)進行重構,,與原來的數(shù)據(jù)有所不同。多數(shù)數(shù)據(jù)采集系統(tǒng)因被測對象的不確定性,,需要采用無損數(shù)據(jù)壓縮。由于LZW無損壓縮算法具有自適應特性,,在對信號統(tǒng)計特性不明確的情況下仍然有較好的壓縮效果,。結合FPGA的高集成度、低功耗,、靈活性及并行運算的特性,,該設計用FPGA硬件實現(xiàn)LZW算法,以提高系統(tǒng)的實時壓縮能力,。

1 LZW算法簡介

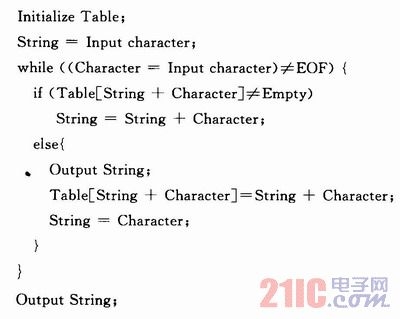

LZW算法是一種基于字典的壓縮算法,,由Lemple、Ziv,、Welch三人共同創(chuàng)造,。該算法在數(shù)據(jù)的壓縮過程中會根據(jù)輸入的數(shù)據(jù)動態(tài)地建立一個字典,后續(xù)輸入的數(shù)據(jù)都會在這個字典中匹配查找,,根據(jù)查找是否成功決定壓縮編碼的輸出,。該算法的巧妙之處在于,壓縮過程中動態(tài)建立的字典不需要與壓縮數(shù)據(jù)流一道進行傳輸和存儲,。在對數(shù)據(jù)進行解壓時,,也能夠通過壓縮數(shù)據(jù)流重新建立一個字典,來完成解壓縮,。算法粗略的描述如下:

![]()

算法首先進行字典的初始化,。然后輸入第一個字符數(shù)據(jù)賦給變量String(S)。數(shù)據(jù)逐個輸入壓縮器中,并賦給變量Character(C),。s和C生成一個索引,,與字典中的詞條數(shù)據(jù)進行匹配:如果匹配成功,將S和C的編碼值賦給S,,繼續(xù)進行下一輪的匹配,;如果匹配失敗,則將S輸出,,將S和C的編碼值存入字典,,并且將C的值賦給S,這一過程一直進行直到結束,。最后輸出S,,輸出結束標志。

由算法描述可見,,LZW算法過程并不是很復雜,,能夠得到較快的壓縮速度。并且其在對數(shù)據(jù)特征并不了解情況下,,也能有較好的壓縮效果,。同時,其對應的解壓縮算法也不復雜,,解壓速度也優(yōu)于其他一些算法,。

2 LZW算法的FPGA實現(xiàn)

CycloneII是Altera公司推出的新一代低成本系列FPGA器件,選用CycloneII系列的EP2C5T14418芯片來實現(xiàn)數(shù)據(jù)壓縮,。這款芯片有4 608個邏輯單元,、26塊M4K RAM塊、13個嵌入式乘法器,、2個鎖相環(huán),,用戶I/O引腳數(shù)目為89,完全能夠滿足設計對存儲器容量以及邏輯功能的要求,,并且有一定余量,,便于功能擴展。設計采用Quartus II為FPGA器件軟件開發(fā)平臺,,用VHDL+原理圖的混合輸入方式進行層次化描述,。系統(tǒng)的整體框圖如圖1所示。采集到的數(shù)據(jù)經(jīng)過壓縮后存儲到外部存儲器,,再讀入計算機,,用專用軟件對壓縮數(shù)據(jù)進行解壓還原,對原始數(shù)據(jù)進一步分析處理,。

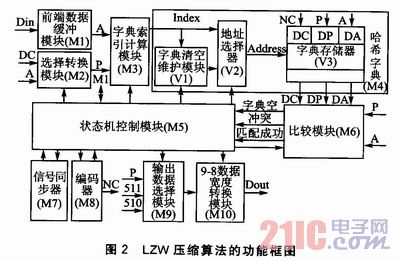

整個設計的核心是壓縮算法的實現(xiàn),。FPGA設計過程中模塊劃分非常重要,,好的模塊劃分能夠大大減少邏輯所消耗的面積并優(yōu)化功能的時序關鍵路徑。具體到LZW算法的FPGA實現(xiàn),,劃分了10個大模塊,,各個模塊相互之間的連接如圖2所示。圖中名字相同的箭頭,,表示是連接在一起的,。為了使框圖看起來比較清晰,圖中省略了一些控制信號的連接,。狀態(tài)機控制模塊(M5)是整個壓縮模塊的時序控制中心,,根據(jù)其他模塊反饋給它的信號,判斷壓縮的運行狀態(tài),,從而控制其他各個模塊的運行,。

用FPGA實現(xiàn)LZW算法要解決以下幾個問題:

①壓縮過程中字典的緩存問題,。因為所有數(shù)據(jù)處理和傳輸工作都是由FPGA完成,,且考慮到實時壓縮速度,字典的緩存使用FPGA內(nèi)部的RAM資源,。

?、谧值涞慕⑴c更新問題。字典的建立使用FPGA片內(nèi)資源來完成,,大容量字典雖然會提高壓縮比,,但必須考慮到FPGA內(nèi)部的資源量。因此選用9位的定長編碼方式對數(shù)據(jù)進行處理,。

③壓縮后輸出數(shù)據(jù)流傳輸和存儲問題,。由于壓縮后是9位的數(shù)據(jù)流,,不利于數(shù)據(jù)的存儲,因此將9位的數(shù)據(jù)轉(zhuǎn)換成8位的數(shù)據(jù)流進行傳輸和存儲,。

3 系統(tǒng)測試及性能分析

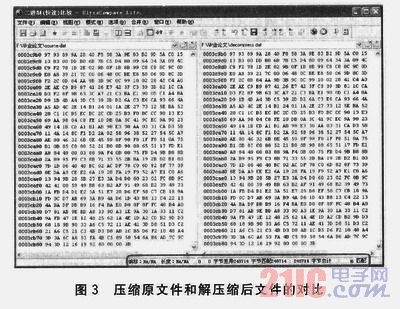

首先測試LZW算法模塊能否正確無誤地壓縮數(shù)據(jù),。先由上位機發(fā)送數(shù)據(jù)給FPGA,F(xiàn)PGA壓縮數(shù)據(jù)并寫入SRAM存儲器,。壓縮結束后,,上位機讀取SRAM中的數(shù)據(jù)并存為一個文件,最后再將這個文件與用軟件壓縮的結果作比較,,來判斷結果正確與否,。圖3是壓縮原文件和解壓后文件以十六進制形式對比后的結果,從圖中下方框中的信息可知,,兩個文件的大小都是248 714字節(jié),,0字節(jié)差異,完全匹配。為了提高測試的全面性,,避免出現(xiàn)因為偶然而造成的個別功能死角沒被測到,,利用格式各異的數(shù)據(jù)文件進行了大量的壓縮結果對比實驗,最終實驗結果表明軟硬件壓縮的結果是一致的,,并且解壓后與源文件也是一樣的,,說明LZW數(shù)據(jù)壓縮模塊實現(xiàn)了功能上的要求。

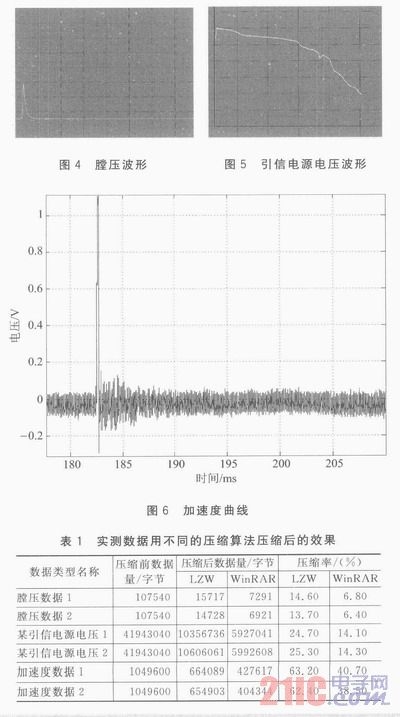

然后對壓縮模塊的壓縮率進行測試,。整個設計最初的定位是應用于微體積,、微功耗的測試系統(tǒng)中,現(xiàn)選取了實驗室里一些實測數(shù)據(jù)(圖4~6),,對其分別用LZW與WinRAR進行壓縮實驗,。WinRAR是一種商業(yè)的無損壓縮軟件,使用的是混合壓縮算法,,可根據(jù)需要向計算機申請內(nèi)存作為哈希字典,,字典大小可達4 MB。壓縮后的最終結果如表1所列,。表中的壓縮率是按壓縮后的數(shù)據(jù)量除以壓縮前的數(shù)據(jù)量計算的,,壓縮率數(shù)值越小表明壓縮效果越好。

從表中可以粗略看出以下兩點:

?、偻粔嚎s算法對同一類數(shù)據(jù)壓縮效果相差不多,,但同一壓縮算法對不同類的數(shù)據(jù)壓縮效果相差較大。

?、贚ZW壓縮算法的壓縮性能低于商業(yè)軟件WinRAR,,并且這種壓縮性能對不同類的數(shù)據(jù)的表現(xiàn)也不盡相同。

從上表可以看出,,所設計的算法對某些類型的數(shù)據(jù)的壓縮效果還是非常顯著的,。雖然從壓縮率上來說,LZW不如WinRAR出色,,這是由于LZW算法要比使用混合算法的winRAR簡單,,同時還受到在FPGA器件中構造的哈希字典容量大小的限制。但LZW的優(yōu)點也在于其算法簡單,,在對同一數(shù)據(jù)文件進行壓縮時,,速度上LZW比WinRAR要勝出一籌,這個速度特性在實時壓縮時尤為重要,。

結語

介紹了一種用FPGA實現(xiàn)的數(shù)據(jù)壓縮系統(tǒng),。通過大量測試驗證,結果表明系統(tǒng)能夠正確無誤地工作,,壓縮時的最大數(shù)據(jù)吞吐量在8 MB/s以上,,對實測數(shù)據(jù)壓縮率最高可達13.70%,,壓縮效果顯著,大大減少了對存儲空間的要求,,實現(xiàn)了壓縮性能與壓縮速度的統(tǒng)一,。同時,當FPGA工作在主頻為24 MHz,,A/D采樣頻率在1 Msps時,,整個電路的供電電流只有37 mA,滿足了測試系統(tǒng)低功耗的要求,。若用外部RAM存儲器實現(xiàn)LZW字典,,將能大幅度地擴大字典容量,顯著改善數(shù)據(jù)的壓縮效果,。